Hardware-Software Co-Design for Optimization

Enroll to start learning

You’ve not yet enrolled in this course. Please enroll for free to listen to audio lessons, classroom podcasts and take practice test.

Interactive Audio Lesson

Listen to a student-teacher conversation explaining the topic in a relatable way.

Introduction to Hardware-Software Co-Design

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Today we're discussing hardware-software co-design. This approach integrates hardware capabilities with software algorithms. Why do you think this is essential for AI applications?

I think it’s important because AI applications need to process data quickly and efficiently. If the hardware can't keep up, it won't matter how good the software is.

Exactly! By designing software that leverages specific hardware features, we can enhance performance and energy efficiency. Can anyone think of a specific example of this?

Maybe using custom algorithms for FPGAs would be an example? Those are programmable right?

Great point! FPGAs allow for custom designs and optimizations that can significantly speed up processing for AI tasks. Let's remember this as we move forward.

Custom AI Algorithms

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Now, let's talk about custom AI algorithms. What advantages do you think they provide when paired with specific hardware?

They can be optimized to run more efficiently on that hardware, right? So they could use less power or compute more quickly?

Exactly! Techniques like dataflow optimization or algorithm pruning can lead to significant performance gains. For instance, pruning could remove parts of a neural network that do not contribute much to accuracy.

And that would help with speed too, since there are fewer calculations to process?

Yes, that's right! This leads to faster computations and less energy consumed—definitely a win-win.

Compiler Optimizations

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Let's move on to compiler optimizations. How do you think these affect the performance of AI systems?

I think they help map complex AI algorithms to hardware better, ensuring that the software takes full advantage of the hardware's capabilities.

Exactly! Advanced compilers can automate the optimization process, saving developers time and effort. Can anyone give an example of how a compiler might change code for better hardware performance?

Maybe it could reorganize loops or functions to reduce memory usage or improve speed?

Spot on! Such optimizations improve overall AI system performance by streamlining code execution on specific architectures.

Real-World Applications of Co-Design

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Lastly, let's explore the real-world applications of hardware-software co-design. Why do you think this is pivotal in field applications?

It's crucial for industries where performance and energy efficiency matter, like in automotive AI for self-driving cars.

Excellent example! In that context, quick decision-making is vital, and hardware-software co-design supports that. What other industries can benefits from this?

Possible applications include healthcare, robotics, or even smart cities, where processing vast amounts of data efficiently is necessary.

Well said! As AI continues to evolve, the importance of co-design strategies will certainly increase.

Introduction & Overview

Read summaries of the section's main ideas at different levels of detail.

Quick Overview

Standard

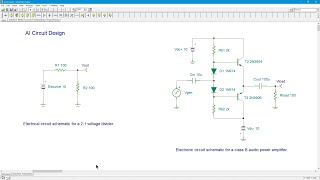

The hardware-software co-design approach focuses on creating optimized AI algorithms tailored for specific hardware architectures, such as ASICs and FPGAs, to achieve peak performance. This involves employing techniques like dataflow optimization and custom compiler tools to ensure that AI tasks are executed efficiently on available hardware.

Detailed

Hardware-Software Co-Design for Optimization

Hardware-software co-design is a critical approach in AI circuit design, as it ensures that AI algorithms are optimized for the hardware they run on. This practice not only maximizes performance but also enhances energy efficiency, allowing AI systems to operate effectively in real-world applications.

Key Aspects of Hardware-Software Co-Design:

- Custom AI Algorithms: Tailoring AI algorithms to leverage the capabilities of specific hardware accelerators—like ASICs (Application-Specific Integrated Circuits) and FPGAs (Field-Programmable Gate Arrays)—can lead to considerable improvements in performance. Techniques such as dataflow optimization, algorithm pruning, and the development of custom instruction sets are commonly utilized to achieve these optimizations.

- Compiler Optimizations: Advanced compilation techniques and tools have emerged to assist developers in efficiently mapping AI workloads to hardware architectures. These compilers employ machine learning methods to automate and enhance code optimization, ensuring that AI systems run at their peak efficiency.

Overall, hardware-software co-design is a powerful strategy in AI circuit optimization, facilitating the development of high-performance and energy-efficient systems necessary for today’s demanding AI applications.

Youtube Videos

Audio Book

Dive deep into the subject with an immersive audiobook experience.

Custom AI Algorithms

Chapter 1 of 2

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

By designing AI algorithms specifically for hardware accelerators like ASICs and FPGAs, developers can achieve significant performance improvements. This may involve dataflow optimization, algorithm pruning, or custom instruction sets.

Detailed Explanation

In this part, we learn about how AI algorithms can be tailored to run perfectly on specific types of hardware like ASICs (Application Specific Integrated Circuits) and FPGAs (Field Programmable Gate Arrays). When developers create algorithms tailored to the specific characteristics of the hardware, they can significantly boost the performance of those algorithms. This customization might include optimizing how data is processed (dataflow optimization), removing unneeded parts of the algorithm (algorithm pruning), or creating specialized commands that the hardware can execute more efficiently (custom instruction sets).

Examples & Analogies

Think of a tailor crafting a bespoke suit for a specific individual. Just as a tailor adjusts the fit, fabric, and style to the client's unique proportions and preferences, developers customize AI algorithms to fit the 'shape' and capabilities of a specific hardware platform. This results in a product (the AI system) that performs exceptionally well for its intended purpose.

Compiler Optimizations

Chapter 2 of 2

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Advanced compilers and software tools are being developed to automatically map AI workloads onto the most efficient hardware. These tools use machine learning techniques to optimize code for various AI accelerators.

Detailed Explanation

Here, we discuss how compilers—programs that translate code from high-level languages to machine code—play a critical role in enhancing the efficiency of AI systems. New types of compilers are emerging that use machine learning methods to automatically identify the best way to allocate computing tasks to different hardware components. This helps to ensure that AI workloads run on the most suitable hardware, maximizing performance and energy efficiency.

Examples & Analogies

Imagine a busy restaurant where the chef must assign different tasks to various staff (like chopping vegetables, grilling, and plating). If the chef has a smart system that can analyze which staff are best suited for each task at any moment, it ensures that the food is prepared faster and more efficiently. Similarly, compilers optimize the allocation of tasks to hardware, resulting in improved performance in AI systems.

Key Concepts

-

Co-Design: Integrating hardware capabilities with software algorithms.

-

Custom Algorithms: Specific AI algorithms tailored for optimized performance on dedicated hardware.

-

Compiler Optimizations: Techniques enhancing the efficiency of code execution on given hardware.

Examples & Applications

Using FPGAs in AI applications to create custom processing units that execute specific algorithms faster than general-purpose processors.

Employing compiler optimizations to restructure machine learning code for increased execution speed on specific AI accelerators.

Memory Aids

Interactive tools to help you remember key concepts

Rhymes

To design fine with AI in mind, optimize code, and hardware aligned.

Stories

Imagine a world where software and hardware partners dance together to solve complex AI tasks efficiently, hand in hand.

Memory Tools

C.A.C. – Custom Algorithms and Compilers help optimize!

Acronyms

HSC – Hardware-Software Co-design

High-Speed Computing.

Flash Cards

Glossary

- HardwareSoftware CoDesign

An integrated approach that optimizes AI algorithms for specific hardware.

- Custom Algorithms

Algorithms tailored for specific hardware capabilities, enhancing performance.

- Compiler Optimizations

Techniques used by compilers to improve the execution efficiency of code on hardware.

Reference links

Supplementary resources to enhance your learning experience.