Equivalence Checking

Enroll to start learning

You’ve not yet enrolled in this course. Please enroll for free to listen to audio lessons, classroom podcasts and take practice test.

Interactive Audio Lesson

Listen to a student-teacher conversation explaining the topic in a relatable way.

Introduction to Equivalence Checking

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Today, we will discuss equivalence checking. What do you think it means in the context of VLSI design?

I think it’s about making sure two different designs do the same thing?

Exactly! Equivalence checking verifies that two representations of the same design are functionally equivalent, such as comparing RTL and gate-level representations.

Why is this process important?

It ensures that synthesis, which transforms high-level designs into lower-level representations, does not introduce errors. This is crucial to maintain the integrity of our design!

What tools do we use for this?

Great question! One common tool is the Binary Decision Diagram or BDD. These help represent Boolean functions efficiently and facilitate functional checks.

So, are BDDs essential for all equivalence checks?

Yes, particularly for combinational equivalence checking, where we compare two logic circuits directly.

To summarize, equivalence checking is vital for ensuring design correctness, especially after synthesis. BDDs help in performing these checks efficiently.

Binary Decision Diagrams (BDDs)

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Let’s dive deeper into Binary Decision Diagrams. Can anyone explain how they work?

Do they represent Boolean functions in a way that's easier to manage?

Exactly! They simplify complex Boolean expressions into a more manageable form, making comparisons easier.

How do they help in avoiding errors?

By using BDDs, we can check that both circuit representations yield the same outputs for identical inputs, thus identifying discrepancies efficiently.

Can we visualize BDDs?

Yes! A BDD is often visualized as a directed acyclic graph. Each node represents a variable, while the paths lead to outcomes, allowing for an intuitive way to understand the function representation.

So, how do we use BDDs in practice?

In practice, we convert the circuits into BDDs and then perform equivalence checks by comparing these diagrams directly to ensure they represent the same logical functions.

To recap, BDDs are a powerful tool in equivalence checking, crucial for simplifying comparisons between complex designs.

Combinational Equivalence Checking

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Now, let’s discuss combinational equivalence checking. What do you all think it involves?

Is it about checking if two logic circuits perform the same operation?

Yes, precisely! It’s about verifying that two logic circuits are equivalent, ensuring that any transformations during synthesis have not changed their functionality.

What kind of transformations are we concerned about?

We’re mainly concerned with optimizations and modifications that can occur during synthesis. Combinational checks help catch issues introduced during these processes.

How do we perform these checks?

We create Boolean expressions for both circuits and compare them. If they simplify to the same form or yield the same outputs, they are equivalent.

Are there tools that automate this checking?

Yes! Many verification tools automate combinational equivalence checking, integrating BDDs for efficient comparisons.

To sum up, combinational equivalence checking is vital to verify circuits post-synthesis, utilizing methodologies and tools that streamline this verification process.

Introduction & Overview

Read summaries of the section's main ideas at different levels of detail.

Quick Overview

Standard

This section covers equivalence checking, a key formal verification technique that ensures two representations of a design, such as RTL and gate-level descriptions, are functionally equivalent, utilizing tools like Binary Decision Diagrams (BDD) for efficient comparison.

Detailed

Equivalence Checking

Equivalence checking is a crucial formal verification technique used to ascertain that two different representations of the same design—like Register Transfer Level (RTL) and gate-level descriptions—are functionally equivalent. This verification step is essential to ensure that the design synthesis process does not introduce errors, maintaining its correctness throughout the transition between abstraction levels.

Key Components of Equivalence Checking

- Binary Decision Diagrams (BDDs): BDDs play a vital role in this process by offering a compact and efficient representation of Boolean functions. They facilitate the comparison of two finite-state systems at the functional level, streamlining the verification process.

- Combinational Equivalence Checking: This involves directly comparing the logic circuits to confirm their equivalence. It is particularly relevant during the verification of transformations that occur during synthesis or optimization efforts in VLSI designs.

Understanding equivalence checking is critical in ensuring that various representations of a design maintain consistent functionality, thereby reinforcing the integrity of VLSI design processes.

Youtube Videos

![VLSI Design [Module 05 - Lecture 19] Verification: LTL/CTL based Verification](https://img.youtube.com/vi/41vpxiPKmwQ/mqdefault.jpg)

![VLSI Design [Module 05 - Lecture 21] Verification: BDD based verification](https://img.youtube.com/vi/nJOz4fnrRoA/mqdefault.jpg)

Audio Book

Dive deep into the subject with an immersive audiobook experience.

Definition of Equivalence Checking

Chapter 1 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Equivalence checking is a formal verification technique used to verify that two different representations of the same design (e.g., RTL and gate-level) are functionally equivalent. This is an important step in verifying that the synthesis process has not introduced any errors.

Detailed Explanation

Equivalence checking is a method to ensure that two different versions or representations of a design, such as a Register Transfer Level (RTL) design and a gate-level representation, behave the same way in terms of function. This is crucial in the design process because if there are inconsistencies between these representations after synthesis, it could lead to errors or bugs in the final product. Verifying that they are equivalent helps confirm the correctness of the transformations that have taken place during the synthesis.

Examples & Analogies

Think of equivalence checking like comparing two different cookbooks for the same recipe. One cookbook might offer a detailed, step-by-step guide, while the other might provide a simplified version. Even though the format is different, if both result in the same delicious dish, we can say they are equivalent in purpose. Just as you want to ensure you end up with the same dish regardless of the recipe format, equivalence checking ensures that both design formats behave the same.

Use of Binary Decision Diagrams (BDD)

Chapter 2 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Binary Decision Diagrams (BDD): BDDs are widely used for equivalence checking as they provide a compact and efficient representation of Boolean functions, making it easier to compare two designs at the functional level.

Detailed Explanation

Binary Decision Diagrams, or BDDs, are a data structure used to represent Boolean functions in a way that makes them easier to manipulate and compare. When performing equivalence checking, BDDs help to condense the complexity of the design, allowing for changes in the design to be represented more compactly. This efficiency is critical because it allows tools to quickly determine whether two representations of a function yield the same output for all possible inputs.

Examples & Analogies

Imagine BDDs as a map that shows different paths (inputs) to reach various destinations (outputs) for two different routes. Instead of writing detailed directions for each possible journey, the map summarizes the key intersections and turns, making it easy to see if both routes lead to the same destinations. This visualization helps you quickly assess whether two journeys (designs) arrive at the same conclusion (output), simplifying the process of comparison.

Combinational Equivalence Checking

Chapter 3 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

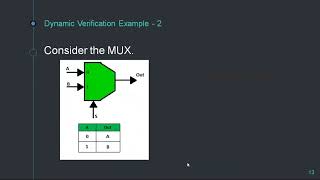

Combinational Equivalence Checking: This involves checking the equivalence between two logic circuits by comparing their Boolean functions. This method is particularly useful when verifying transformations during synthesis or optimization.

Detailed Explanation

Combinational equivalence checking is a specific application of equivalence checking that focuses on comparing two combinational logic circuits. By examining their Boolean functions, engineers can determine if both circuits will produce the same output for every possible input. This step is especially important during the design's synthesis phase, where logic can change and transform. Ensuring that the pre- and post-synthesis designs are equivalent guarantees that no logic errors have been introduced during that process.

Examples & Analogies

Consider two different routes to get to the same train station: one is direct while the other might take a scenic detour. In combinational equivalence checking, we compare both routes, ensuring that no matter which way you go, you will arrive at the station on time (with the same outputs). If one route says it's a 10-minute ride and the other says 15 minutes, you must double-check if both actually arrive in sync with the train schedule (equivalent outputs).

Key Concepts

-

Functional Equivalence: The condition where two representations of a design perform identically under all possible inputs.

-

Synthesis: The process of transforming a high-level design representation into a lower-level format without changing its functionality.

-

BDDs: A data structure used to represent Boolean functions efficiently, facilitating equivalence checking.

Examples & Applications

Comparing an RTL description of an AND gate to its corresponding gate-level implementation to ensure they yield the same results for inputs 0 and 1.

Using BDDs to simplify the comparison between two versions of a digital circuit to verify that optimizations haven't altered its behavior.

Memory Aids

Interactive tools to help you remember key concepts

Rhymes

If two designs produce the same, equivalence checking is the name of the game!

Stories

Imagine two friends, one cooking and the other baking—both end up with delicious cake! Equivalence checking is like ensuring that both methods yield the same result.

Memory Tools

E.B.C. - Equivalence, BDDs, Combinational checks.

Acronyms

C.E.C. - Combinational Equivalence Checking for verifying combinational circuits.

Flash Cards

Glossary

- Equivalence Checking

A formal verification process used to confirm that two representations of a design are functionally equivalent.

- Binary Decision Diagrams (BDDs)

A data structure that efficiently represents Boolean functions, facilitating the comparison of different designs.

- Combinational Equivalence Checking

A technique that verifies the equivalence of two logic circuits by comparing their Boolean functions.

Reference links

Supplementary resources to enhance your learning experience.