ARMv7-A ISA Features

Interactive Audio Lesson

Listen to a student-teacher conversation explaining the topic in a relatable way.

32-bit Architecture and Memory Addressing

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Let's start with the ARMv7-A's architecture. It uses a 32-bit design, which allows it to address up to 4GB of memory. Does anyone know why that limitation might exist?

I think it has to do with how many addresses can be created in a 32-bit space.

Exactly right! A 32-bit number can represent 2^32 possible addresses, which equals 4GB. This is essential for embedded systems and mobile devices that need moderate memory management.

Does this mean ARMv7-A cannot use more memory than that?

Correct, without memory extensions, that's the limit. It’s a trade-off for efficiency in design when developing mobile devices.

What if I had an application that needed more memory?

In that case, developers would look for a solution like using a different architecture that supports 64-bit addressing.

To recap, ARMv7-A’s 32-bit architecture is optimal for its target applications but comes with its memory limitations. Does everyone remember that?

Execution Modes

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Now, let's discuss the various execution modes in ARMv7-A. Can anyone name a mode?

There's User Mode, right?

That's correct, Student_4! User Mode is where regular applications run with limited privileges. What about another mode?

Um, System Mode?

Great job! In System Mode, more privileged operations can be performed which are necessary for running the operating system. This segmentation ensures that critical system operations aren’t violated by user applications.

And what about interrupts?

Good question! ARMv7-A has distinct interrupt modes, namely IRQ for normal interrupts and FIQ for fast interrupts. They help manage system responsiveness and processing priority. A good mnemonic to remember is 'I for Interrupt and F for Fast'.

To summarize, understanding these execution modes helps developers ensure that applications can run securely and efficiently.

Thumb-2 Instruction Set

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Next, let’s dive into the Thumb-2 instruction set. Why do we think it’s advantageous?

It allows writing smaller code, right? That’s good for efficient memory use.

Exactly, Student_3! Thumb-2 includes both 16-bit and 32-bit instructions, resulting in better code density. It helps in reducing the program size without losing performance quality.

How does it affect the performance, though?

Great question! By minimizing the size of the program, the processor can fetch instructions faster, leading to enhanced performance. It’s key for mobile applications where resources are limited.

What’s the trade-off for using Thumb-2?

Well, sometimes, in very performance-critical applications, utilizing all 32-bit instructions might yield better performance. Developers must make decisions based on specific application needs.

Remember, the benefit of Thumb-2 is its balance between size and speed, which is crucial in mobile computing.

Pipeline Architecture

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Lastly, let’s look at pipeline architecture. ARMv7-A uses a 5-stage pipeline. Why do you think that matters?

Does it allow multiple instructions to be processed at once?

Exactly! By dividing instruction processing into stages - Fetch, Decode, Execute, Memory, and Write-back - it enables overlapping instruction execution, which significantly increases throughput. This means better performance!

Are there any downsides?

That's a keen insight! Pipeline stalls can occur if an instruction depends on the results of a previous one, which may reduce the efficiency. However, modern CPUs manage this with techniques like branch prediction.

So, it's all about balancing speed and complexity?

Yes! Efficient use of a pipeline contributes greatly to the performance of architectures like ARMv7-A. Keep this in mind as it enables performance-critical applications to thrive.

Introduction & Overview

Read summaries of the section's main ideas at different levels of detail.

Quick Overview

Standard

The ARMv7-A ISA includes essential features such as a 32-bit architecture, different execution modes, the Thumb-2 instruction set for better code density, and a multi-level exception system, enhancing performance, security, and system integration suitable for advanced computing environments.

Detailed

ARMv7-A ISA Features

The ARMv7-A instruction set architecture (ISA) includes various features designed to enhance performance, security, and system integration in high-end applications. Key elements of the ARMv7-A architecture include:

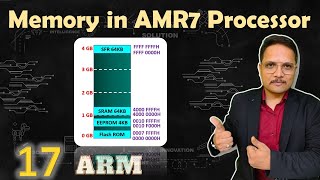

- 32-bit Architecture: The ARMv7-A architecture allows for direct memory addressing of up to 4GB without the use of extensions, making it well-suited for mobile and embedded systems.

- Execution Modes: ARMv7-A includes multiple execution modes:

- User Mode: Where standard applications run with limited privileges.

- System Mode: A privileged mode for accessing system-level operations.

- Supervisor Mode (SVC Mode): Used primarily by the operating system for specific tasks.

- Interrupt Modes: Enable handling of hardware exceptions, with IRQ for normal interrupts and FIQ for fast interrupts, allowing differentiated priority handling.

- Thumb-2 Instruction Set: ARMv7-A introduces Thumb-2, a combined set of 16-bit and 32-bit instructions enhancing code density, allowing for smaller programs that do not compromise on performance.

- Exception Levels (EL): The architecture supports four exception levels from EL0 (user applications) to EL3 (secure environment), enhancing system security and isolation.

- Pipeline Architecture: ARMv7-A uses a 5-stage pipeline (Fetch, Decode, Execute, Memory, Write-back) to ensure high instruction throughput, crucial for performance-sensitive applications.

In conclusion, these features makes the ARMv7-A architecture a powerful choice for mobile devices, embedded systems, and enterprise applications that require high-performance processing and efficient memory management.

Youtube Videos

Audio Book

Dive deep into the subject with an immersive audiobook experience.

32-bit Architecture

Chapter 1 of 5

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

ARMv7-A is based on a 32-bit architecture, meaning it can address up to 4GB of memory directly (without extensions). This is suitable for mobile and embedded systems requiring moderate memory addressing.

Detailed Explanation

The ARMv7-A architecture is defined as a 32-bit system. This is important because it dictates how much memory theprocessor can handle at once. In a 32-bit architecture, the maximum amount of directly addressable memory is 4 gigabytes (GB). This means that applications running on devices using ARMv7-A can utilize up to 4GB of RAM effectively, which is often sufficient for mobile devices and embedded systems that don’t require vast amounts of memory. For instance, a simple mobile app may only use a fraction of this memory, ensuring smooth operation without needing excessive resources.

Examples & Analogies

Consider your kitchen as representing your computer's memory. If your kitchen can only hold four large cupboards (representing 4GB of memory), you can fit a variety of ingredients but may struggle if you try to buy a whole warehouse of supplies. So, in a 32-bit system like ARMv7-A, you have a sufficient amount of space for the applications that typically run on mobile devices.

ARMv7-A Execution Modes

Chapter 2 of 5

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

ARMv7-A Execution Modes:

- User Mode: The mode where application software runs with limited privileges.

- System Mode: A privileged mode for system-level software like the operating system.

- Supervisor Mode: Also called SVC Mode, used by an operating system kernel to perform protected tasks.

- Interrupt Modes: Including IRQ (normal interrupts) and FIQ (fast interrupts) for handling hardware exceptions with different priorities.

Detailed Explanation

ARMv7-A supports multiple execution modes, each designed for different use cases. In User Mode, applications run with limited permissions to prevent them from executing sensitive operations that could harm the system. System Mode is utilized by the operating system to manage resources and provide services. Supervisor Mode (or SVC Mode) allows the OS kernel to perform critical functions with elevated privileges. Additionally, ARMv7-A has two types of interrupt modes: IRQ for standard interrupts and FIQ for higher priority tasks that require immediate attention, optimizing how the CPU handles various tasks.

Examples & Analogies

Think of these execution modes like the different levels of authority in a library. A regular librarian (User Mode) can check books in and out but can't access restricted sections. The library manager (System Mode) has broader access to manage the library. The head librarian (Supervisor Mode) can decide which sections get opened after hours. Meanwhile, urgent requests (similar to FIQ) get prioritized over normal requests (like IRQ) for immediate attention.

Thumb-2 Instruction Set

Chapter 3 of 5

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

ARMv7-A introduces the Thumb-2 instruction set, which is a mixed 16-bit and 32-bit instruction set, providing better code density (smaller program size) without sacrificing performance. Thumb-2 allows developers to write more compact code while still benefiting from high performance.

Detailed Explanation

The Thumb-2 instruction set is a significant feature of the ARMv7-A architecture. It combines both 16-bit and 32-bit instructions, allowing developers to create smaller and more efficient programs. By using smaller instructions when possible (16-bit), the overall size of the application can be reduced without compromising its performance. This is especially useful in mobile devices where storage space and memory usage are critical factors, enabling software to run smoothly and efficiently.

Examples & Analogies

Consider packing for a trip. If you can use smaller containers (16-bit instructions) to hold your essentials while still packing some larger items (32-bit instructions) efficiently, your suitcase won't be overloaded. This means you can go on your trip with everything you need, fitting it all nicely without running out of space.

Exception Levels (EL)

Chapter 4 of 5

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

ARMv7-A supports multiple exception levels (EL0 to EL3), which determine the privilege level and the set of instructions that can be executed by different parts of the system, providing improved security and system isolation.

Detailed Explanation

The ARMv7-A architecture defines several exception levels, numbered from EL0 to EL3. Each level represents a different privilege category: EL0 is the least privileged and is typically where user applications run, whereas EL3 is the most privileged and is dedicated to secure operations like handling system management. This hierarchy increases the system's security and ensures that critical tasks can be secured from less trusted code, avoiding unauthorized access or interference between different application contexts.

Examples & Analogies

Imagine a multi-story building where the ground floor (EL0) is open to the public and is where visitors can access general services. Higher floors (like EL3) are restricted to authorized personnel, where sensitive company operations take place. This structure prevents unauthorized access to important functions, ensuring security and safety across the organization.

Pipeline Architecture

Chapter 5 of 5

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

ARMv7-A processors use a 5-stage pipeline (Fetch, Decode, Execute, Memory, Write-back). The efficient pipeline design enables high instruction throughput, making it suitable for performance-critical applications.

Detailed Explanation

The ARMv7-A architecture employs a 5-stage pipeline process that enhances instruction execution efficiency. Each stage of the pipeline allows different parts of an instruction to be processed simultaneously – fetching new instructions while simultaneously decoding and executing others in different stages. This overlapping significantly boosts the number of instructions that can be processed in a given timeframe, making ARMv7-A highly effective for applications that demand rapid processing and responsiveness.

Examples & Analogies

Consider a factory assembly line where different workers perform specific tasks at the same time. One worker might be assembling a part (Execute) while another prepares to assemble the next part (Fetch). By working in stages, the factory can produce items much faster than if each worker could only focus on one task at a time, just like how a pipeline allows ARMv7-A to handle multiple instructions in parallel.

Key Concepts

-

32-bit Architecture: Allows addressing of up to 4GB of memory.

-

Execution Modes: Several modes such as User, System, Supervisor, and Interrupts for privileged operations.

-

Thumb-2: Improved instruction set for compact and efficient coding.

-

Exception Levels: Multi-level privilege system enhancing security and isolation.

-

Pipeline Architecture: A 5-stage design for high instruction throughput.

Examples & Applications

An application developed on ARMv7-A can run efficiently on mobile devices due to its 32-bit capabilities, addressing typical memory requirements without requiring larger systems.

Games on smartphones that leverage Thumb-2 can reduce the application size while maintaining a richer graphical experience.

Memory Aids

Interactive tools to help you remember key concepts

Rhymes

In a land of 32 bits, 4GB is where it fits; mode meanings thus explore, to secure and access more.

Stories

Imagine a smart mobile device, built on ARMv7-A, its 32-bit heart beats steadily, addressing tasks effortlessly. Its Thumb-2 fingers write code so tight, ensuring apps fit just right.

Memory Tools

To remember execution modes: User, System, Supervisor, skip to Interrupts. Use the acronym 'USSI' - 'U See Secure Instructions.'

Acronyms

P.E.M.W.F. for Pipeline stages

for Fetch

for Execute

for Memory

for Write-back

and D for Decode.

Flash Cards

Glossary

- 32bit Architecture

An architecture that allows direct addressing of up to 4GB of memory.

- Execution Modes

Different modes in which the processor operates, each with specific privileges.

- Thumb2

An instruction set that combines 16-bit and 32-bit instructions for better code density.

- Pipeline Architecture

A technique in processors that allows overlapping execution of instructions in stages.

- Exception Levels (EL)

Various privilege levels in the architecture that determine instruction access and security.

Reference links

Supplementary resources to enhance your learning experience.