AMBA 3 AHB-Lite Bus

Enroll to start learning

You’ve not yet enrolled in this course. Please enroll for free to listen to audio lessons, classroom podcasts and take practice test.

Interactive Audio Lesson

Listen to a student-teacher conversation explaining the topic in a relatable way.

Introduction to AHB-Lite Bus

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Today, we're going to explore the AMBA 3 AHB-Lite Bus. This bus interface allows our Cortex-M0 processor to communicate efficiently with memory and peripherals. Who can tell me why a bus interface is important?

Is it because it helps with data transfers between the processor and other components?

Exactly, it manages data flow efficiently! The AHB-Lite allows for both single and burst data transfers. Can anyone explain what burst data transfer means?

It means sending a block of data in a single transfer instead of multiple single transfers, right?

Correct! Burst transfers significantly improve performance for applications that need to move large amounts of data quickly.

Memory-Mapped I/O

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Moving on, let's talk about memory-mapped I/O. This feature of the AHB-Lite Bus simplifies programming. Can anyone tell me how this works?

I think it means that we can access peripherals through standard memory instructions?

Exactly! By mapping peripherals into the memory space, we can use simple load and store instructions to interact with them, just like we do with regular memory.

That sounds much easier than separate I/O management!

It is! This architecture allows developers to write more efficient code with less overhead.

Direct Memory Access (DMA)

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Now let’s dive into Direct Memory Access, or DMA. Who can explain why DMA is beneficial?

Isn't it that DMA lets peripherals transfer data to memory without involving the CPU?

That's right! This offloads work from the CPU, allowing it to perform other tasks while data is being transferred.

So, it improves efficiency especially when handling large data blocks, right?

Exactly, and it helps maintain responsiveness in real-time applications.

Integration of AHB-Lite in Embedded Systems

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

As we wrap up, how does the AHB-Lite Bus contribute to the design of embedded systems?

It optimizes data transfers, making the system more efficient overall.

And it simplifies programming with memory-mapped I/O!

Correct! The AHB-Lite Bus significantly enhances the performance capabilities of systems using the Cortex-M0 by providing a seamless way to integrate memory and peripherals.

Recap of ARM Cortex-M0 Overview

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Let's recap what we learned about the ARM Cortex-M0 processor. Can anyone tell me the primary focuses of its design?

It's designed for low power consumption and high efficiency.

Correct! This makes it perfect for embedded systems where resources are limited. What else is unique about its architecture?

It has a three-stage pipeline: Fetch, Decode, and Execute, which helps in reducing latency.

Exactly! This streamlined pipeline simplifies processing. Now, does anyone remember the instruction set it uses?

The Thumb-2 instruction set, right?

Yes! It allows for better code density, which is crucial in embedded applications. Great job!

Interrupt Handling in ARM Cortex-M0

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Now, let's talk about interrupt handling. What is the significance of the Nested Vectored Interrupt Controller?

It manages interrupts efficiently and allows for fast response with ISRs.

Good! The NVIC can handle up to 32 interrupt sources. Why do you think prioritization is important here?

To ensure critical interrupts are processed before less important ones!

Exactly! What are PendSV and SysTick used for in this context?

PendSV is for context switching, and SysTick helps with timing tasks.

Great explanation! Efficient handling of interrupts is vital for real-time applications.

Bus Interface and Memory Management

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Next, let's discuss the bus interface. Can anyone explain what the AHB-Lite bus does for the Cortex-M0?

It connects the processor to memory and peripherals and supports single and burst transfers.

Exactly right! And how does memory-mapped I/O simplify programming?

It treats peripherals as memory, which makes it easier to interact with them.

Well done! Now, can someone explain how the Memory Protection Unit aids in memory management?

It defines access permissions, preventing unauthorized memory access.

Exactly! This is crucial for maintaining system integrity. Let's summarize what we learned.

Power Management Techniques

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Power management is vital in embedded systems, especially for battery-operated devices. What features does the Cortex-M0 have to save power?

It has multiple sleep modes and dynamic voltage and frequency scaling.

Great! What do these sleep modes entail?

The Sleep Mode halts execution but allows for quick waking, while Deep Sleep Mode turns off non-essential components.

Right! And what about power gating?

It powers down parts of the chip not in use to prevent consuming unnecessary power.

Excellent job! Remember: efficient power usage is essential for the longevity of embedded systems.

System Control and Security Features

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Finally, let's talk about system control and security. What role does the System Control Block play?

It manages resets, interrupts, and exception handling!

Exactly! And how does the Cortex-M0 handle debugging?

It has a serial wire debug interface for real-time debugging features.

That's correct! Although it lacks advanced security like TrustZone, what can developers do?

They can implement software-based security measures!

Absolutely! In mission-critical applications, even simple protections can help.

Introduction & Overview

Read summaries of the section's main ideas at different levels of detail.

Quick Overview

Standard

The section discusses the AMBA 3 AHB-Lite Bus, highlighting its ability to support single and burst data transfers, memory-mapped I/O for simplified programming, and Direct Memory Access (DMA) for efficient data handling without CPU intervention.

Detailed

AMBA 3 AHB-Lite Bus

The AMBA 3 AHB-Lite Bus is an integral component of the ARM Cortex-M0 architecture that streamlines communication between the microprocessor core, memory, and I/O peripherals. This bus interface supports both single and burst data transfers, making it well-suited for high-performance applications.

Key Features:

- Memory-Mapped I/O: Peripherals are integrated into the same address space as memory, facilitating simpler programming and quicker data communications.

- Direct Memory Access (DMA): The support for basic DMA functionality allows peripherals to transfer data directly to memory without using CPU resources, improving system efficiency, particularly during large data transfers.

The AHB-Lite interface enhances the overall performance of systems utilizing the Cortex-M0 by optimizing data flow and reducing processing overhead, thereby playing a critical role in embedded system design.

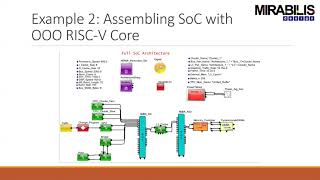

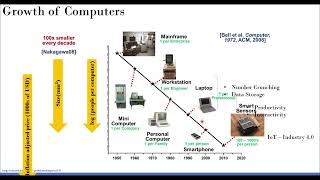

Youtube Videos

Audio Book

Dive deep into the subject with an immersive audiobook experience.

Introduction to AHB-Lite Bus

Chapter 1 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

The Cortex-M0 processor connects to the system's memory and peripherals using the AHB-Lite (Advanced High-Performance Bus) interface. This bus supports both single and burst data transfers and connects the processor to the system's memory and I/O devices.

Detailed Explanation

The AHB-Lite (Advanced High-Performance Bus) is an interface that connects the Cortex-M0 processor to the various components of a system, such as memory and input/output devices. It is designed to handle different types of data transfers - both single transfers, where one piece of data is sent, and burst transfers, where multiple pieces of data are sent in quick succession. This capability allows the processor to communicate efficiently with other parts of the system, improving overall performance.

Examples & Analogies

Think of the AHB-Lite bus like a multi-lane highway where cars (data) travel between different cities (memory and peripherals). Some cars may travel alone, while others travel in groups, speeding up transport significantly. Just as a highway facilitates the flow of traffic, the AHB-Lite bus ensures smooth and efficient communication between the processor and all connected devices.

Memory-Mapped I/O

Chapter 2 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Peripherals are mapped into the same address space as memory, which simplifies programming and enables efficient I/O communication. This allows the processor to communicate directly with peripherals like timers, UARTs, or GPIOs, without complex I/O management overhead.

Detailed Explanation

In a memory-mapped I/O system, devices like timers and communication ports are assigned specific memory addresses, just like regular RAM. This means that the processor can interact with these devices using standard memory instructions. For example, to read data from a sensor (a peripheral), the processor simply requests the data from a specific address. This design significantly simplifies programming because there’s no need for complicated commands to manage I/O operations separately.

Examples & Analogies

Imagine a vast library where every piece of information, including books, magazines, and digital resources, is stored under specific catalog numbers (memory addresses). By knowing the catalog number, a librarian (the processor) can easily find and access any resource quickly. This is similar to how memory-mapped I/O allows the processor to seamlessly interact with device peripherals.

Direct Memory Access (DMA)

Chapter 3 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

The Cortex-M0 supports basic DMA functionality, allowing peripherals to directly access memory without CPU intervention. This reduces CPU load and improves system efficiency, especially when transferring large blocks of data.

Detailed Explanation

Direct Memory Access (DMA) is a capability that allows certain peripherals to transfer data to and from memory without needing the central processing unit (CPU) to manage each byte of data. This is especially useful for tasks like reading large files from storage or receiving data from sensors. By allowing peripherals to handle these transfers, the CPU can perform other tasks concurrently, leading to better overall system efficiency and performance.

Examples & Analogies

Consider a busy restaurant where the chef (CPU) is preparing meals while the waitstaff (DMA) takes care of delivering orders to the kitchen from customers. By letting the waitstaff handle this delivery, the chef can focus on cooking and preparing meals without the interruption of running back and forth, making the entire restaurant operate more efficiently.

Key Concepts

-

AMBA 3 AHB-Lite Bus: A communication interface optimizing data transfer between the processor and memory/peripherals.

-

Memory-Mapped I/O: A technique to access peripherals through memory addresses for simplified programming.

-

Direct Memory Access (DMA): Allows peripherals to access memory without CPU involvement, enhancing efficiency.

Examples & Applications

Example of memory-mapped I/O can be accessing a timer peripheral through its address just like reading a variable.

DMA is utilized in audio systems where a sound card can send audio data directly to memory without stalling the main CPU.

Memory Aids

Interactive tools to help you remember key concepts

Rhymes

AHB-Lite, transfers data alright, single, burst, makes them bright!

Stories

Imagine a busy post office. AHB-Lite is like a fast conveyor belt that delivers mail directly to houses (memory) and doesn't occupy the postmen (CPU) when carrying large amounts of letters (data).

Memory Tools

AMBA B.M.D. - AHB-Lite for Burst and Memory-Mapped for Direct access!

Acronyms

DMA - Direct Memory Access saves you from CPU weight!

Flash Cards

Glossary

- AMBA

Advanced Microcontroller Bus Architecture, a set of specifications for interfacing components in a microcontroller or processor system.

- AHBLite

The Advanced High-Performance Bus Lite, a simplified version of AHB that supports high-speed connectivity for embedded systems.

- MemoryMapped I/O

A method that allows peripherals to be accessed as if they are memory addresses, simplifying programming.

- Direct Memory Access (DMA)

A feature that allows certain hardware subsystems to access system memory independently of the CPU.

Reference links

Supplementary resources to enhance your learning experience.