ARM Cortex-M0 System Control and Security Features

Enroll to start learning

You’ve not yet enrolled in this course. Please enroll for free to listen to audio lessons, classroom podcasts and take practice test.

Interactive Audio Lesson

Listen to a student-teacher conversation explaining the topic in a relatable way.

Introduction to System Control Block

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Today, we're going to discuss the System Control Block, or SCB. It is integral to how the ARM Cortex-M0 manages system control and exception handling. Can anyone tell me what they think the SCB might do?

Maybe it manages how the processor handles different system states?

Exactly! The SCB manages system resets, interrupt vectoring, and even exception priority handling. These functions help keep the system stable. For instance, if a critical fault occurs, the SCB enables the processor to reset quickly. Let’s remember SCB as 'System Control Bursts' – it bursts into action when a fault happens.

How does it decide which exception to handle first?

Great question! The SCB uses a priority scheme to handle exceptions. More critical exceptions have higher priority, ensuring quick response times. This is crucial in mission-critical applications.

What happens during a system reset?

During a reset, all system states are cleared, and the processor returns to a known state. This is critical for recovering from faults. To remember this, think of the term SCB as 'Safe Control Breach.' At the end of this session, we recall that the SCB manages system status and resets for stability.

Debugging and Tracing Capabilities

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Next, let's explore debugging. The ARM Cortex-M0 features a Serial Wire Debug interface. Who can tell me how this helps developers?

It probably allows them to see what's happening in their code while it's running!

Exactly! It enables real-time debugging, meaning you can pause execution, set breakpoints, and monitor variables. This function is crucial for identifying and fixing bugs quickly. Remember it as 'SWD: See What Debugging.'

What is the Instrumented Trace capability?

Good question! It's a feature that allows developers to trace program execution flow. This helps in optimizing performance and debugging. Think of it as having a roadmap for your code. Debugging is like driving; sometimes you need to see all the turns you've made.

Why is real-time debugging beneficial?

Real-time debugging reduces development time by enabling immediate inspection and testing. Excel in your projects by utilizing SWD to 'Snag Warnings Defects.'

Security Features of Cortex-M0

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Finally, let’s discuss security. While Cortex-M0 doesn’t have TrustZone, it supports basic software-based security. Why do you think this is important?

Because many embedded systems still need some protection against unauthorized access?

Exactly! Even if high-level security is not feasible, implementing software-based measures helps protect critical functions. We can think of it as 'So You Keep Basic,' which implies keeping security fundamental but effective.

What type of applications might use this security feature?

Great question! Applications requiring basic security, like IoT devices or medical devices, can implement these features. Knowing this helps you appreciate security in the Cortex-M0. At the end of this session, let’s recap: security may not be high-end but it provides essential protections.

Recap of ARM Cortex-M0 Overview

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Let's recap what we learned about the ARM Cortex-M0 processor. Can anyone tell me the primary focuses of its design?

It's designed for low power consumption and high efficiency.

Correct! This makes it perfect for embedded systems where resources are limited. What else is unique about its architecture?

It has a three-stage pipeline: Fetch, Decode, and Execute, which helps in reducing latency.

Exactly! This streamlined pipeline simplifies processing. Now, does anyone remember the instruction set it uses?

The Thumb-2 instruction set, right?

Yes! It allows for better code density, which is crucial in embedded applications. Great job!

Interrupt Handling in ARM Cortex-M0

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Now, let's talk about interrupt handling. What is the significance of the Nested Vectored Interrupt Controller?

It manages interrupts efficiently and allows for fast response with ISRs.

Good! The NVIC can handle up to 32 interrupt sources. Why do you think prioritization is important here?

To ensure critical interrupts are processed before less important ones!

Exactly! What are PendSV and SysTick used for in this context?

PendSV is for context switching, and SysTick helps with timing tasks.

Great explanation! Efficient handling of interrupts is vital for real-time applications.

Bus Interface and Memory Management

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Next, let's discuss the bus interface. Can anyone explain what the AHB-Lite bus does for the Cortex-M0?

It connects the processor to memory and peripherals and supports single and burst transfers.

Exactly right! And how does memory-mapped I/O simplify programming?

It treats peripherals as memory, which makes it easier to interact with them.

Well done! Now, can someone explain how the Memory Protection Unit aids in memory management?

It defines access permissions, preventing unauthorized memory access.

Exactly! This is crucial for maintaining system integrity. Let's summarize what we learned.

Power Management Techniques

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Power management is vital in embedded systems, especially for battery-operated devices. What features does the Cortex-M0 have to save power?

It has multiple sleep modes and dynamic voltage and frequency scaling.

Great! What do these sleep modes entail?

The Sleep Mode halts execution but allows for quick waking, while Deep Sleep Mode turns off non-essential components.

Right! And what about power gating?

It powers down parts of the chip not in use to prevent consuming unnecessary power.

Excellent job! Remember: efficient power usage is essential for the longevity of embedded systems.

System Control and Security Features

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Finally, let's talk about system control and security. What role does the System Control Block play?

It manages resets, interrupts, and exception handling!

Exactly! And how does the Cortex-M0 handle debugging?

It has a serial wire debug interface for real-time debugging features.

That's correct! Although it lacks advanced security like TrustZone, what can developers do?

They can implement software-based security measures!

Absolutely! In mission-critical applications, even simple protections can help.

Introduction & Overview

Read summaries of the section's main ideas at different levels of detail.

Quick Overview

Standard

The ARM Cortex-M0's system control and security features are crucial for maintaining stability and reliability in embedded systems. Key components include the System Control Block (SCB) for managing exceptions and interrupts, debugging capabilities for development, and software-based security measures for adequate protection in less secure environments.

Detailed

ARM Cortex-M0 System Control and Security Features

The ARM Cortex-M0 processor integrates important system control and security features that play a vital role in ensuring the reliability and safety of embedded systems, especially in mission-critical applications. Here are the main components:

System Control Block (SCB)

The SCB is responsible for managing system control and exception handling. It includes:

- System Reset: Facilitates the restart of the system to recover from faults.

- Interrupt Vectoring: Directs incoming interrupts to the correct interrupt handler.

- Exception Priority Handling: Ensures that more critical exceptions are serviced before less critical ones. The SCB allows control over the processor's operational mode (e.g., Handler or Thread mode) and manages fault conditions, such as usage and bus faults, thereby enhancing the robustness of the system.

Debugging and Tracing

The Cortex-M0 supports essential debugging features through its Serial Wire Debug (SWD) interface, allowing for:

- Real-Time Debugging: Developers can inspect the execution state of programs, set breakpoints, and monitor variable states.

- Instrumented Trace Capability: Enables tracing of execution flow for debugging and performance optimization, which is essential during development and troubleshooting.

Security and TrustZone

While the Cortex-M0 does not incorporate ARM's advanced TrustZone technology (found in higher-end cores), its streamlined architecture supports basic software-based security measures. This allows developers to implement necessary security protocols and practices, making it suited for applications where high-level security is not the primary concern, but still safeguarding critical functions.

In summary, these system control and security features ensure that the ARM Cortex-M0 can reliably manage system events, debug operations efficiently, and implement basic security measures, making it a robust choice for numerous embedded applications.

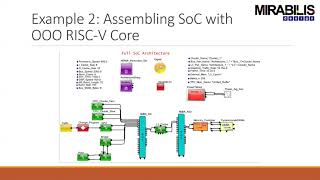

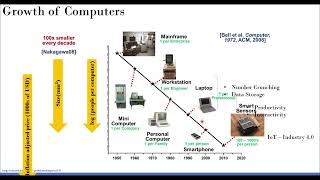

Youtube Videos

Audio Book

Dive deep into the subject with an immersive audiobook experience.

System Control Block (SCB)

Chapter 1 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

System Control Block (SCB)

The SCB manages system control and exception handling, including system reset, interrupt vectoring, and exception priority handling.

The SCB also includes registers for controlling the processor's mode (e.g., Handler or Thread mode) and for controlling fault management (e.g., usage fault, bus fault).

Detailed Explanation

The System Control Block (SCB) is a crucial component of the ARM Cortex-M0 processor. It manages key system functionalities such as resetting the system, handling exceptions (which are unexpected events that require immediate attention), and prioritizing these exceptions. The SCB can control whether the processor operates in either 'Handler mode' (for executing interrupt service routines) or 'Thread mode' (for running the main application). Additionally, it manages faults, which are issues that can affect the operation of the system, such as attempting to access illegal memory locations.

Examples & Analogies

Think of the SCB like the manager at a busy airport. The airport manager ensures that all flights are properly scheduled (interrupt vectoring), deals with delays and emergencies (fault management), and decides whether staff need to prioritize urgent situations (exception priority handling). Just like the airport manager ensures smooth operations and quick response to issues, the SCB ensures the processor runs efficiently and can handle unexpected events.

Debugging and Tracing

Chapter 2 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Debugging and Tracing

The Cortex-M0 supports basic debugging capabilities through its serial wire debug (SWD) interface. This interface allows real-time debugging, including step execution, breakpoints, and watchpoints for monitoring variables.

The Instrumented Trace capability allows developers to trace execution flow for debugging and performance optimization.

Detailed Explanation

Debugging and monitoring code execution is essential for developers, especially when building complex systems. The Cortex-M0 provides a Debugging feature using a Serial Wire Debug (SWD) interface that allows developers to interact with the processor in real-time. They can step through the code line by line, set breakpoints (which pause execution at specific points), and watch variables (monitor their values as the code runs). This makes identifying and fixing errors easier. Additionally, Instrumented Trace helps developers visualize how the program runs over time, which is valuable for improving performance.

Examples & Analogies

Imagine debugging like being a detective trying to solve a mystery. The SWD interface is your magnifying glass that helps you look closely at each clue (code execution), while breakpoints are like markers that tell you to stop and examine specific evidence. Meanwhile, tracing is like setting up a camera to capture how the mystery unfolds, allowing you to review the entire process and find out where things went wrong.

Security and TrustZone

Chapter 3 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Security and TrustZone

While the Cortex-M0 does not include ARM’s TrustZone technology (available in higher-end Cortex-M cores), its simple design allows it to be used in many systems where security is not a primary concern. However, developers can implement software-based security measures for basic protection.

Detailed Explanation

The ARM Cortex-M0 lacks the advanced security feature known as TrustZone, which is available in more powerful ARM Cortex processors. This means the Cortex-M0 is typically used in less security-sensitive environments. However, developers can still implement basic security measures through software to protect critical functionalities. This allows the Cortex-M0 to be used in a variety of applications ranging from simple to more complex systems, with appropriate security considerations depending on the use case.

Examples & Analogies

Consider the Cortex-M0 like a small-town library without a security guard (TrustZone), which means it might not have high-tech protection against theft or vandalism. While this might be appropriate for a place where books are mostly community donations and there isn’t much valuable information, the librarians can still put up some basic measures—like requiring sign-outs for rare books or monitoring who uses the computers—for essential security.

Key Concepts

-

System Control Block (SCB): Manages system control functions and exception handling in Cortex-M0.

-

Serial Wire Debug (SWD): Provides real-time debugging and monitoring capabilities.

-

Software-based Security: Fundamental protective measures without advanced hardware technology.

Examples & Applications

The SCB allows the processor to reset in case of critical errors, ensuring stability.

SWD enables developers to stop execution, analyze variable states, and continue running the program smoothly.

Basic software-based security measures can be implemented in IoT devices to safeguard sensitive information.

Memory Aids

Interactive tools to help you remember key concepts

Rhymes

SCB helps when things go wrong, resetting systems, keeping them strong!

Stories

Imagine a software developer named Sam. Sam uses the SWD tool to catch every bug in his code. It’s like having a detective that helps him navigate problems!

Memory Tools

Remember 'SDS' for Security: Software, Debugging, SCB.

Acronyms

Recall SCB as 'System Control Box' where all control functions are stored.

Flash Cards

Glossary

- System Control Block (SCB)

A component of the ARM Cortex-M0 responsible for managing system control, exception handling, and processor modes.

- Serial Wire Debug (SWD)

A debugging interface that allows for real-time program debugging and monitoring.

- Debugging and Tracing

Techniques used to identify issues in software and track execution flow for optimization.

- TrustZone

ARM's security technology that allows for the creation of secure and non-secure areas in a processor, not available in Cortex-M0.

- Softwarebased Security Measures

Security practices implemented in software to protect systems without hardware support.

Reference links

Supplementary resources to enhance your learning experience.