Power Gating

Enroll to start learning

You’ve not yet enrolled in this course. Please enroll for free to listen to audio lessons, classroom podcasts and take practice test.

Interactive Audio Lesson

Listen to a student-teacher conversation explaining the topic in a relatable way.

Introduction to Power Gating

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Today, we're going to explore power gating. Can anyone tell me what power gating means?

Is it about saving energy by turning off parts of the processor?

Exactly! Power gating allows specific areas of the chip to be powered down when they're not in use. This leads to significant energy savings. Let's think about why this matters—especially in battery-operated devices.

So, it helps keep the battery life longer?

Correct! The longer the battery lasts, the better the user experience. Can anyone give me an example of a device that might use this feature?

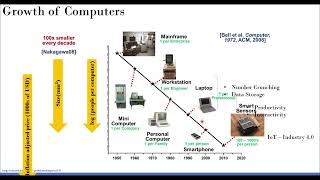

Maybe a smartwatch or a sensor?

Great examples! Both types of devices benefit from power gating.

In summary, power gating is a critical feature that optimizes energy use in processors. It powers down sections when they're not needed, enhancing battery life.

Significance of Power Gating

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Now that we understand what power gating is, let’s discuss why it’s significant for embedded systems. Who wants to start?

It seems like embedded systems can't afford to waste energy since they use batteries.

Absolutely! Power gating directly influences how efficiently these systems operate. Can someone explain how this relates to the overall design of a processor?

It has to be integrated with other features like sleep modes, right?

Exactly! Together with sleep modes and DVFS, power gating creates a comprehensive system for managing energy. Why do you think this is crucial for modern applications?

Because many devices are becoming portable and rely heavily on batteries.

Precisely! Power management ensures devices can function efficiently for extended periods without frequent charging.

Power Gating Techniques

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Let’s dive deeper into how power gating is implemented in the Cortex-M0. What are some potential techniques that might be used?

Could it be as simple as just switching off power to parts?

Very focused! That’s indeed part of it. The processor can isolate and turn off parts that are not needed. What would be an example of parts that could be powered down?

Like peripheral units or unused cores?

Exactly! Powering down non-essential units can significantly reduce leakage current. What do you think happens to performance when these regions are powered back on?

It should come back quickly since it’s designed for efficiency.

Right! The Cortex-M0 is designed for minimal latency when waking up those regions!

In summary, power gating techniques in the Cortex-M0 are essential for enhancing power efficiency and maintaining performance.

Recap of ARM Cortex-M0 Overview

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Let's recap what we learned about the ARM Cortex-M0 processor. Can anyone tell me the primary focuses of its design?

It's designed for low power consumption and high efficiency.

Correct! This makes it perfect for embedded systems where resources are limited. What else is unique about its architecture?

It has a three-stage pipeline: Fetch, Decode, and Execute, which helps in reducing latency.

Exactly! This streamlined pipeline simplifies processing. Now, does anyone remember the instruction set it uses?

The Thumb-2 instruction set, right?

Yes! It allows for better code density, which is crucial in embedded applications. Great job!

Interrupt Handling in ARM Cortex-M0

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Now, let's talk about interrupt handling. What is the significance of the Nested Vectored Interrupt Controller?

It manages interrupts efficiently and allows for fast response with ISRs.

Good! The NVIC can handle up to 32 interrupt sources. Why do you think prioritization is important here?

To ensure critical interrupts are processed before less important ones!

Exactly! What are PendSV and SysTick used for in this context?

PendSV is for context switching, and SysTick helps with timing tasks.

Great explanation! Efficient handling of interrupts is vital for real-time applications.

Bus Interface and Memory Management

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Next, let's discuss the bus interface. Can anyone explain what the AHB-Lite bus does for the Cortex-M0?

It connects the processor to memory and peripherals and supports single and burst transfers.

Exactly right! And how does memory-mapped I/O simplify programming?

It treats peripherals as memory, which makes it easier to interact with them.

Well done! Now, can someone explain how the Memory Protection Unit aids in memory management?

It defines access permissions, preventing unauthorized memory access.

Exactly! This is crucial for maintaining system integrity. Let's summarize what we learned.

Power Management Techniques

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Power management is vital in embedded systems, especially for battery-operated devices. What features does the Cortex-M0 have to save power?

It has multiple sleep modes and dynamic voltage and frequency scaling.

Great! What do these sleep modes entail?

The Sleep Mode halts execution but allows for quick waking, while Deep Sleep Mode turns off non-essential components.

Right! And what about power gating?

It powers down parts of the chip not in use to prevent consuming unnecessary power.

Excellent job! Remember: efficient power usage is essential for the longevity of embedded systems.

System Control and Security Features

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Finally, let's talk about system control and security. What role does the System Control Block play?

It manages resets, interrupts, and exception handling!

Exactly! And how does the Cortex-M0 handle debugging?

It has a serial wire debug interface for real-time debugging features.

That's correct! Although it lacks advanced security like TrustZone, what can developers do?

They can implement software-based security measures!

Absolutely! In mission-critical applications, even simple protections can help.

Introduction & Overview

Read summaries of the section's main ideas at different levels of detail.

Quick Overview

Standard

Power gating is a crucial feature of the ARM Cortex-M0 processor, allowing specific regions of the chip to be powered down when inactive, thus minimizing energy waste. This section discusses the implications of power gating for embedded systems, particularly in battery-operated applications.

Detailed

Power Gating in ARM Cortex-M0

In the ARM Cortex-M0 architecture, power management is vital for optimizing performance in resource-constrained environments. Power gating allows certain regions of the processor to be shut down when not in use, effectively reducing overall power consumption. This section explores:

- Efficiency in Power Management: The ARM Cortex-M0 features a design that can selectively power down components, ensuring that energy is conserved when the system is idle.

- Impact on Embedded Systems: This functionality is particularly beneficial for applications that rely on battery power, as it extends operational life without compromising performance.

- Integration with Other Features: Power gating works alongside various sleep modes and Dynamic Voltage and Frequency Scaling (DVFS) techniques, creating a comprehensive power management strategy that enhances the efficiency of the overall system.

Youtube Videos

Audio Book

Dive deep into the subject with an immersive audiobook experience.

Benefits of Power Gating

Chapter 1 of 1

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

This prevents unnecessary power consumption.

Detailed Explanation

By implementing power gating, devices equipped with the Cortex-M0 can greatly extend battery life and reduce heat generation from unnecessary power draw. This is particularly valuable in portable electronics, where battery efficiency is crucial for user experience. Furthermore, the reduction in power usage not only helps in energy savings but also contributes to a more environmentally friendly design as it minimizes the overall energy footprint.

Examples & Analogies

Think of power gating like turning off unused appliances in your home. If you leave your television, computer, and lights on when you are not home, you waste a lot of electricity. However, if you remember to turn off those devices, you save energy and lower your electric bill. Similarly, power gating ensures that only essential components of the chip consume power, leading to savings on energy.

Key Concepts

-

Power Gating: A method to turn off inactive sections of the processor to save energy.

-

Embedded Systems: Systems designed for specific tasks with limited resources.

-

Dynamic Voltage and Frequency Scaling: A method to optimize power based on task demands.

Examples & Applications

Smartwatches use power gating to extend battery life by powering down when not in use.

Battery-operated sensors that only activate their processing core when measurements are needed.

Memory Aids

Interactive tools to help you remember key concepts

Rhymes

Power gating saves you a lot of power, closing down parts like a quiet flower.

Stories

Imagine a city where streetlights automatically turn off during the day; just like that, power gating keeps parts of the processor off when not needed.

Memory Tools

Remember 'SOP' – Sleep modes, Off regions, and Power efficiency when thinking about power management.

Acronyms

GATE – Gating Active Transistor Energy, which reminds us of how power gating works.

Flash Cards

Glossary

- Power Gating

A power management technique that allows sections of a processor to be powered down to save energy when not in use.

- Embedded Systems

Computer systems designed for specific control functions within larger systems, often with limited resources and battery-operated.

- Dynamic Voltage and Frequency Scaling (DVFS)

A technique that adjusts the voltage and frequency of a processor based on workload demands to optimize energy consumption.

- Sleep Mode

A low power state where the CPU halts execution but can quickly resume operation.

- Integrated Circuit

A set of electronic circuits on a small chip, which can accommodate thousands of transistors for various functions.

Reference links

Supplementary resources to enhance your learning experience.