Combinational Logic Design using Verilog

Interactive Audio Lesson

Listen to a student-teacher conversation explaining the topic in a relatable way.

Overview of Combinational Logic

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Today we'll start our journey into combinational logic design. Can anyone tell me what defines a combinational circuit?

Isn't it a circuit where the output only depends on the current inputs?

Exactly! Outputs rely solely on current input values, and there's no memory involved. Think of it as a 'real-time' condition. Can someone tell me why not having memory might be important?

Because it means the output can change instantly with different inputs?

Correct! Now let's summarize: Combinational logic has immediate outputs based on inputs without storing data.

Implementing Multiplexers

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Next, let’s dive into multiplexers. Who can explain what a multiplexer does?

It selects one of many input signals and forwards it to a single output line, right?

Yes! You did great. Now let’s consider a 4-to-1 multiplexer. Who would like to show how we could code this in Verilog using an assign statement?

We can use an expression like `assign Y = (Sel == 2'b00) ? D0 : (Sel == 2'b01) ? D1 : (Sel == 2'b10) ? D2 : D3;`

Great job! This code lets us select the correct data input based on the select lines. Now can anyone tell me why using an assign statement is beneficial here?

It's concise and makes it clear how the output relates directly to the inputs!

Perfect! Remember, concise code can be crucial for understanding.

Decoders and Demultiplexers

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Now, what about demultiplexers? Why do we use them?

To route one input to multiple outputs based on select lines.

"Exactly! For instance, in a 1-to-4 demultiplexer, we can write:

Encoders and Comparators

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Let’s now discuss encoders, particularly the priority encoder. How would a priority encoder handle multiple active inputs?

It outputs the highest priority active input, right?

"Exactly! Let's look at an example implementation:

Review of Key Concepts

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

To wrap up, let's summarize what we learned about combinational logic designs. What were the key components?

Multiplexers, demultiplexers, decoders, and encoders were key!

Also, that memory is not involved with combinational circuits!

Exactly! Those aspects define their functionality. Anyone remember how we implemented a multiplexer?

We used an assign statement to choose which input to output!

Fantastic! Let’s keep these concepts fresh in our minds as we move on.

Introduction & Overview

Read summaries of the section's main ideas at different levels of detail.

Quick Overview

Standard

In this section, we delve into how to effectively translate combinational logic into Verilog code. We explore structures such as multiplexers, demultiplexers, encoders, and comparators through clear code examples, emphasizing their key characteristics such as outputs being dependent solely on current inputs without memory elements.

Detailed

Combinational Logic Design using Verilog

In this section of the chapter, we focus on the implementation of combinational logic circuits using Verilog. Combinational logic is characterized by the property that the output is determined only by the current inputs, with no memory elements or required clock signals. The primary goal is to depict the behavior of combinational systems such as multiplexers, demultiplexers, decoders, and encoders through Verilog coding.

Key Points:

- Combinational Logic Properties: Output solely depends on current input values, thus having no opportunity for memory elements.

- Implementing Common Circuits: We cover how to write Verilog code for various components:

- Multiplexers (Muxes): Example of a 4-to-1 multiplexer can be implemented using either dataflow style with assign statements or behavioral style with always blocks.

- Demultiplexers (Demuxes): These components distribute a single input signal into multiple output lines based on select inputs.

- Decoders: These convert binary inputs into one-out-of-N outputs. For instance, a 2-to-4 decoder where specific input combinations drive an output high according to the decoded value.

- Encoders: Particularly a priority encoder which ensures that higher-priority inputs are represented in outputs when multiple inputs are active.

- Adders and Comparators: The understanding of ripple-carry adders has previously been demonstrated, along with implementing combinational logic for comparing bit patterns.

The goal of this section is not only to learn how to write Verilog for these devices but also understand their operation and purpose within digital systems.

Youtube Videos

Audio Book

Dive deep into the subject with an immersive audiobook experience.

Review of Combinational Logic Properties

Chapter 1 of 6

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Output depends only on current inputs.

No memory elements.

No clock signal is required for function, only for synchronization if part of a larger synchronous system.

Delay is due to gate propagation.

Detailed Explanation

Combinational logic is a type of digital circuit where the output is determined entirely by the current inputs, without any memory or feedback from previous states. This means that for any given input, the output is immediately produced based on the logical operations defined. Since there are no memory elements involved, such circuits do not require a clock signal; however, in larger systems, synchronization might still be relevant. The delay in output is primarily due to the propagation time, which is the time it takes for signals to travel through the logic gates.

Examples & Analogies

Imagine a simple vending machine. When you press a button, the machine immediately responds by dispensing your chosen item based solely on which button you pressed, without storing any previous interactions. The time it takes the item to drop is like the propagation delay; it needs a moment to travel from the machine to you.

Implementing Common Combinational Circuits - Multiplexers

Chapter 2 of 6

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Multiplexers (Muxes):

Dataflow (assign): Best and most concise way. Uses conditional operator.

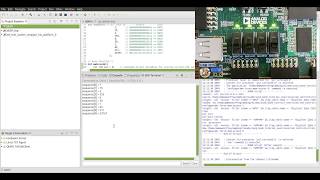

module MUX4_1 (output wire Y, input wire D0, D1, D2, D3, input wire [1:0] Sel); assign Y = Sel[1] ? (Sel[0] ? D3 : D2) : (Sel[0] ? D1 : D0); endmodule

Behavioral (always @(*) with case or if-else):

module MUX4_1_behavioral (output reg Y, input wire D0, D1, D2, D3, input wire [1:0] Sel); always @(*) begin case (Sel) 2'b00: Y = D0; 2'b01: Y = D1; 2'b10: Y = D2; 2'b11: Y = D3; default: Y = 1'bx; // Handle unknown select lines endcase end endmodule

Detailed Explanation

A multiplexer (mux) is a device that selects one of several input signals and forwards the selected input into a single line. In our Verilog code example, we show two ways to implement a 4-to-1 multiplexer. The first method uses a dataflow approach with the assign statement, which is clear and uses a conditional operator for selection. The second method is behavioral, utilizing an always block combined with a case statement to define the output based on the selector inputs. This highlights flexibility in Verilog; you can express the same logic in different styles depending on your needs.

Examples & Analogies

Think of a television remote: you have several channels (inputs). The channel you actually see on the screen is determined by the button you press (selector). In a mux, just like the remote, only one channel is displayed at any time based on the selected button, demonstrating how this component efficiently directs signals.

Implementing Common Combinational Circuits - Demultiplexers

Chapter 3 of 6

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Demultiplexers (Demuxes):

module DEMUX1_4 ( output wire Y0, Y1, Y2, Y3, input wire DataIn, input wire [1:0] Sel ); assign Y0 = (Sel == 2'b00) ? DataIn : 1'b0; assign Y1 = (Sel == 2'b01) ? DataIn : 1'b0; assign Y2 = (Sel == 2'b10) ? DataIn : 1'b0; assign Y3 = (Sel == 2'b11) ? DataIn : 1'b0; endmodule

Detailed Explanation

A demultiplexer takes a single input signal and directs it to one of multiple outputs, based on the control signal, which selects the output line. The Verilog example demonstrates a 1-to-4 demultiplexer where the data input (DataIn) is sent to one of the four outputs (Y0, Y1, Y2, Y3) based on the 2-bit selection input. If the selection matches one of the defined cases, the data is sent to that output; otherwise, the output is set to zero.

Examples & Analogies

Consider a switchboard operator at a telephone exchange. The operator receives a call (the single input) and connects the caller to one of several lines (the outputs) based on the caller's request (selection input). Just as the operator routes the call to the appropriate line, a demultiplexer routes data to the desired output.

Implementing Common Combinational Circuits - Decoders

Chapter 4 of 6

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Decoders:

module Decoder2_4 ( output wire [3:0] Out, input wire [1:0] In ); assign Out[0] = (In == 2'b00); // Only 1 if true, else 0 assign Out[1] = (In == 2'b01); assign Out[2] = (In == 2'b10); assign Out[3] = (In == 2'b11); endmodule

Detailed Explanation

A decoder converts binary information from n input lines to a maximum of 2^n unique output lines. In this example, the 2-to-4 decoder translates 2 input bits into 4 output lines. For each possible combination of the input, only one output can be activated at any time, providing a unique high signal when the input matches a specific value.

Examples & Analogies

Think of a restaurant menu: when you place an order, you communicate your choice (the input) to the waiter. The waiter then brings the specific dish to your table (the relevant output). A decoder functions similarly, ensuring that only the correct output is activated in response to its specific input combination.

Implementing Common Combinational Circuits - Encoders

Chapter 5 of 6

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Encoders (Priority Encoder example):

module PriorityEncoder4_2 ( output reg [1:0] EncodedOut, output reg Valid, input wire [3:0] In ); always @(*) begin Valid = 1'b1; // Default to valid case (In) 4'b0001: EncodedOut = 2'b00; 4'b001x: EncodedOut = 2'b01; // x for don't care, e.g., 0010, 0011 4'b01xx: EncodedOut = 2'b10; 4'b1xxx: EncodedOut = 2'b11; default: begin Valid = 1'b0; EncodedOut = 2'bxx; end // No input active or multiple endcase end endmodule

Detailed Explanation

An encoder is the opposite of a decoder; it converts multiple input lines into fewer output lines. A priority encoder outputs the binary representation of the highest priority input that is active. The Verilog example shows a 4-to-2 priority encoder where it checks the inputs and assigns the output to reflect the highest active line while also setting a valid indicator. In case multiple inputs are active, it prioritizes the one that has the highest significance.

Examples & Analogies

Imagine a school assembly: when multiple students raise their hands to answer a question, the teacher (the encoder) pays attention only to the student who raises their hand first (the highest priority). Just like the encoder prioritizes inputs, the teacher focuses on the most immediate response, ensuring clarity.

Implementing Common Combinational Circuits - Comparators

Chapter 6 of 6

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Comparators:

module MagnitudeComparator_8bit ( output wire A_gt_B, A_eq_B, A_lt_B, input wire [7:0] A, B ); assign A_eq_B = (A == B); assign A_gt_B = (A > B); assign A_lt_B = (A < B); endmodule

Detailed Explanation

A comparator is a circuit that compares two binary numbers and produces outputs indicating their relative magnitudes. The example provided shows an 8-bit magnitude comparator that checks if one number is greater than, less than, or equal to another. The outputs are straightforward: A_eq_B indicates equality, A_gt_B shows if A is greater, and A_lt_B if A is less than B.

Examples & Analogies

Think of a scoring system in a game where the current score of Team A is compared to Team B's score. A referee checks the scores and determines if Team A has more points, has the same points, or has fewer points. Just as the referee’s decisions inform the game outcome based on scores, a comparator evaluates the binary numbers and signals their relationship.

Key Concepts

-

Combinational Logic: Outputs depend only on current inputs.

-

Multiplexers: Devices that select one input from many.

-

Demultiplexers: Distribute inputs to multiple outputs.

-

Decoders: Convert binary inputs into specific outputs.

-

Encoders: Prioritize and produce binary outputs from inputs.

-

Comparators: Compare binary numbers to determine magnitude.

Examples & Applications

4-to-1 Multiplexer Verilog code snippet, demonstrating output selection based on two select lines.

1-to-4 Demultiplexer implementation in Verilog, showing how a single data line distributes to multiple outputs.

2-to-4 Decoder in Verilog that drives outputs based on input binary values.

Memory Aids

Interactive tools to help you remember key concepts

Rhymes

In combinational logic where inputs flow, Outputs come quick, as fast as the show.

Stories

Imagine a busy city intersection: cars (inputs) going in every direction, and at any moment, city lights (the output) decide which cars can move based solely on current traffic.

Memory Tools

MDEC for remembering types of combinational devices: Mux, Demux, Encoder, Decoder.

Acronyms

CLOG

Combinational logic outputs are governed by current inputs.

Flash Cards

Glossary

- Combinational Logic

A type of logic circuit where the output depends only on the current inputs.

- Multiplexer (Mux)

A device that selects one of several input signals and forwards it to a single output line.

- Demultiplexer (Demux)

A device that takes a single input signal and distributes it across multiple output lines based on select inputs.

- Encoder

A device that converts information from one format to another, often condensing multiple inputs into fewer outputs.

- Decoder

A circuit that converts binary inputs into a single active output line.

- Priority Encoder

An encoder that resolves multiple active inputs by prioritizing the highest value.

- Comparator

A device that compares two binary values and determines their relative magnitude.

Reference links

Supplementary resources to enhance your learning experience.