Introduction to the ARM Cortex-M0 Processor

Enroll to start learning

You’ve not yet enrolled in this course. Please enroll for free to listen to audio lessons, classroom podcasts and take practice test.

Interactive Audio Lesson

Listen to a student-teacher conversation explaining the topic in a relatable way.

Introduction to ARM Cortex-M0 Features

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Today we will discuss the ARM Cortex-M0 processor. Can anyone explain what kind of applications you think it is designed for?

Maybe for things like smartphones and tablets?

Good guess! The Cortex-M0 is actually more targeted towards embedded systems, IoT devices, and even medical applications. It's designed to be low-cost and low-power. Do you know why these features are important in those fields?

I think it's because many devices need to run for a long time without running out of battery.

Exactly! The low power consumption makes it perfect for battery-powered devices. Let's remember it with the acronym 'LEAD': Low power, Efficient, Affordable, Designed for embedded systems. Now, what do you know about the architecture of the Cortex-M0?

Is it 32-bit?

Yes! It is a 32-bit processor with a 16-bit instruction set. This blend allows efficient programming while maintaining low pain on memory. A key aspect of its architecture is the separation between data and instructions. Shall we dive deeper into this?

Yes, please!

Awesome! It uses what's called a Harvard architecture, which means it has separate pathways for data and instructions. This leads to faster processing. Remember, 'Separate paths, speedy results!' Let's summarize what we've learned today: the ARM Cortex-M0 is highly suitable for low-power applications and has a 32-bit architecture with a 16-bit instruction set.

Cortex-M0 in Target Applications

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Now that we have an idea about the Cortex-M0's architecture, let’s explore some target applications. Student_1, can you guess some sectors where it might be used?

Maybe in smart home devices like lights?

Absolutely! Smart homes are a perfect example. The Cortex-M0 is also utilized in automotive systems where real-time performance is crucial. Can anyone think of another application?

What about in medical devices?

Great point! Medical devices often require low-power and reliable performance. Memory aid here could be 'CAMPS': Consumer electronics, Automotive, Medical devices, and Smart home. Why do you think low power consumption is critical in these applications?

Because devices in these areas often need to work continuously and can't afford to use too much energy.

Correct! Continuous operation without needing frequent recharges is paramount. So, what is the takeaway from today’s session?

The ARM Cortex-M0 is widely used in various important sectors where low power and efficiency are vital.

Overview of ARM Cortex-M0 Architecture

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Let’s look deeper into the architecture of the Cortex-M0. Can anyone explain what a pipeline architecture is?

Isn't it like a conveyor belt system for instructions?

Exactly! The Cortex-M0 uses a three-stage pipeline: Fetch, Decode, and Execute. This means while one instruction is being executed, another can be fetched. Can anyone repeat those three phases?

Fetch, Decode, Execute!

Perfect! It’s efficient and reduces latency. If we remember 'FDE' for Fetch, Decode, Execute, it helps simplify our understanding. Next, what do you think is the advantage of using a 16-bit instruction set?

I think it saves memory and makes processing faster.

Exactly! Smaller instructions mean a smaller memory footprint. Well done, everyone! So let's summarize: the ARM Cortex-M0’s three-stage pipeline and 16-bit instruction set contribute significantly to its efficient processing.

Introduction & Overview

Read summaries of the section's main ideas at different levels of detail.

Quick Overview

Standard

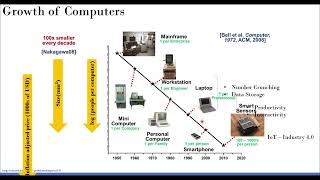

The ARM Cortex-M0 processor is engineered to provide optimal functionality in low-power, cost-efficient applications, particularly in the microcontroller market. Its architecture is well-suited for embedded systems in sectors ranging from consumer electronics to automotive, thanks to its efficient 16-bit instruction set and specialized design for real-time performance.

Detailed

Introduction to the ARM Cortex-M0 Processor

The ARM Cortex-M0 is a pivotal member of the ARM Cortex-M family, representing a 32-bit architecture optimized for low-power, cost-effective applications.

Key Features and Architecture

- Processor Design: The Cortex-M0 is recognized for its simplicity and low cost, making it ideal for applications in embedded systems, IoT devices, and other areas where resources are limited.

- Target Applications: It finds usage in diverse fields such as consumer electronics, automotive systems, medical devices, and home automation — industries where compact size, minimal power consumption, and real-time performance are vital.

- Architecture Overview: Its architecture features a 32-bit processing capacity combined with a 16-bit instruction set, supported by an efficient pipeline designed to maintain high performance even at lower clock speeds.

In essence, the ARM Cortex-M0 offers a blend of efficiency and functionality that empowers a variety of modern technological applications.

Youtube Videos

Audio Book

Dive deep into the subject with an immersive audiobook experience.

Overview of ARM Cortex-M0

Chapter 1 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

The ARM Cortex-M0 is a 32-bit processor designed for low-power, cost-effective applications.

Detailed Explanation

The ARM Cortex-M0 processor is specifically engineered to be efficient in terms of both power usage and cost. Being a 32-bit processor means it can handle a sizable amount of data at once, which is beneficial for a variety of applications. It is particularly targeted towards scenarios where power efficiency is necessary, such as battery-operated devices. This unique design helps ensure that it performs well while consuming minimal resources.

Examples & Analogies

Think of the ARM Cortex-M0 as a small, fuel-efficient car. Just like this car can travel a long distance on a small amount of fuel, the Cortex-M0 can perform complex tasks with minimal power consumption, making it perfect for applications like smartwatches or fitness trackers.

Target Applications

Chapter 2 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

ARM Cortex-M0 is widely used in areas such as consumer electronics, automotive, medical devices, and home automation where small size, low power, and real-time performance are essential.

Detailed Explanation

The ARM Cortex-M0 processor is versatile and finds applications in various fields. It is particularly popular in consumer electronics like smartphones and tablets, automotive systems for engine control, medical devices for monitoring health, and home automation gadgets like smart lighting and security systems. These sectors benefit from the processor's small size and efficient real-time performance, making it ideal for tightly constrained environments where resources are limited.

Examples & Analogies

Imagine a smart refrigerator that can keep track of your food items, suggest recipes, and notify you when you’re running low on essentials. The ARM Cortex-M0 acts like the brain of this refrigerator, managing all these tasks efficiently without using too much energy.

Cortex-M0 Architecture

Chapter 3 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Designed to offer a 32-bit processor with a 16-bit instruction set and an efficient pipeline to provide high performance at low clock speeds.

Detailed Explanation

The architecture of the Cortex-M0 is carefully crafted to optimize performance while maintaining low power consumption. The use of a 16-bit instruction set means that the processor can handle complex commands efficiently, while the 32-bit architecture allows for faster processing. The pipeline execution allows the Cortex-M0 to work on multiple instructions at various stages simultaneously, which helps improve performance even when it is operating at lower clock speeds. This architecture is key to its efficiency.

Examples & Analogies

Think of a production line in a factory where different workers are assigned to different tasks, and they work simultaneously on various stages of production. This setup allows for faster overall output. Similarly, the Cortex-M0's pipeline architecture allows it to execute multiple instructions at the same time, boosting its performance.

Key Concepts

-

Low-Power Design: The ARM Cortex-M0 is specifically designed for applications requiring minimal power consumption.

-

16-bit Instruction Set: Allows more efficient coding and better memory utilization.

-

Harvard Architecture: Enhances performance by separating instruction and data pathways.

-

Microcontroller Targeting: Designed for markets demanding cost-effective solutions in embedded systems.

Examples & Applications

The Cortex-M0 is frequently used in fitness trackers to monitor health data continuously while prolonging battery life.

An automotive system using Cortex-M0 manages real-time operations for airbag deployment, enhancing safety.

Memory Aids

Interactive tools to help you remember key concepts

Rhymes

In the embedded scene, the ARM Cortex-M0 glows, Low power, so easy, it's the king of the shows!

Stories

Imagine a tiny robot in a house, it quietly monitors tasks without fuss. Powered by Cortex-M0, it works all day, using little power, in its tiny way.

Memory Tools

Use 'LEAD' to remember: Low power, Efficient, Affordable, Designed for embedded systems.

Acronyms

Remember 'CAMPS'

Consumer electronics

Automotive

Medical devices

Smart home.

Flash Cards

Glossary

- ARM CortexM0

A 32-bit processor designed for low-power, cost-effective applications in the microcontroller market.

- Microcontroller (MCU)

A compact integrated circuit designed to govern a specific operation in an embedded system.

- Pipeline Architecture

An architecture where multiple instruction phases are overlapped, similar to a conveyor belt.

- Thumb2 Instruction Set

An efficient instruction set that allows for reduced instruction size and enhanced performance.

- Harvard Architecture

An architecture that separates data and instruction pathways for improved performance.

Reference links

Supplementary resources to enhance your learning experience.