Memory Management in ARM Cortex-M0

Enroll to start learning

You’ve not yet enrolled in this course. Please enroll for free to listen to audio lessons, classroom podcasts and take practice test.

Interactive Audio Lesson

Listen to a student-teacher conversation explaining the topic in a relatable way.

Linear Addressing

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Let's start our discussion with linear addressing. The ARM Cortex-M0 utilizes a linear memory addressing scheme. This means that memory addresses are continuous and simple to manage.

How does linear addressing simplify memory management compared to other methods?

Great question! Unlike virtual memory techniques that introduce complexity, linear addressing provides a straightforward approach, as each address directly corresponds to a physical memory location.

So, every time we reference a memory address, it points directly to a specific location?

Exactly! It simplifies programming and debugging significantly. Remember, this linear approach is particularly advantageous in embedded systems.

Can you explain how this affects performance?

Definitely! Since there’s no translation overhead, memory access is faster and more efficient, crucial for real-time applications.

In summary, the linear addressing method streamlines memory operations and enhances performance for embedded applications.

Memory Protection Unit (MPU)

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Now let's delve into the Memory Protection Unit, or MPU. Unlike a full memory management unit, the MPU provides basic memory protection by defining regions with specific access rights.

What kind of access rights can it define?

Excellent inquiry! The MPU can assign read, write, or execute permissions to different memory regions. This is essential for safeguarding critical data and code in embedded applications.

Why is it significant not to have a full MMU?

A full MMU can introduce complexity and resource demands that are often unnecessary for simple embedded systems. The MPU strikes a balance between protection and efficiency.

Does software have to manage the MPU settings?

Absolutely. Developers need to configure the MPU in their applications, ensuring that permissions align with the intended access to maintain system integrity.

To summarize, the MPU enables basic memory protection, which is crucial in embedded systems for maintaining data integrity and security while keeping the system efficient.

Stack Pointer and Program Counter Management

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Let's wrap up our discussion by talking about the stack pointer and program counter. The ARM Cortex-M0 utilizes both a 32-bit stack pointer and a program counter. Who can tell me the role of each?

The stack pointer keeps track of the top of the stack, right?

Correct! The stack pointer helps manage function calls and local variables efficiently by keeping track of where the last data was stored.

And the program counter? Is it just about keeping track of where to go next?

Exactly! The program counter indicates the address of the next instruction to be fetched and executed. It's critical for managing the flow of execution.

Does this differ in other processors?

Yes, while most 32-bit processors follow a similar structure, specifics like how they utilize these pointers can vary. In the Cortex-M0, their integration ensures efficient execution flow, which is essential in real-time systems.

In summary, the stack pointer and program counter are vital for execution control, aiding in efficient memory use and flow within embedded applications.

Introduction & Overview

Read summaries of the section's main ideas at different levels of detail.

Quick Overview

Standard

The memory management system in ARM Cortex-M0 is straightforward, utilizing a linear addressing scheme to facilitate ease of programming. It includes an optional Memory Protection Unit (MPU) for basic memory protection and employs a 32-bit stack pointer and program counter for managing execution flow.

Detailed

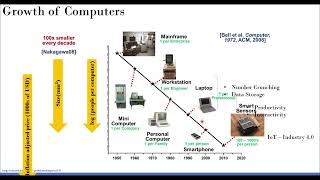

The ARM Cortex-M0 employs a simple and efficient memory management system geared towards embedded applications. Utilizing a linear addressing model allows for enhanced simplicity in memory operations, distinguishing it from more complex systems that rely on virtual memory management. The optional Memory Protection Unit (MPU) serves to delineate memory regions and impose access restrictions, enhancing security and stability within embedded systems. Additionally, the processor maintains a 32-bit stack pointer and program counter for managing the execution flow, typical of many 32-bit processors. These factors contribute to the ARM Cortex-M0's effectiveness in resource-constrained environments, vital for the growing embedded market.

Youtube Videos

Audio Book

Dive deep into the subject with an immersive audiobook experience.

Linear Addressing

Chapter 1 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

The Cortex-M0 uses a linear memory addressing scheme, which simplifies memory management and avoids the complexity of virtual memory found in more powerful processors.

Detailed Explanation

In the ARM Cortex-M0 processor, memory management is very straightforward because it uses a linear addressing system. This means that each memory location is identified by a unique linear address, making it easy for the processor to find and access data. Unlike more advanced processors that use virtual memory (a more complex system that maps addresses to memory), the Cortex-M0 keeps it simple. This simplification is beneficial in embedded systems, where efficiency and low resource usage are crucial.

Examples & Analogies

Think of linear addressing like a street where each house has a specific number. If you want to visit a house, you simply look up its number and go directly to it, making navigation easy and straightforward. In contrast, virtual memory is like a complex neighborhood with multiple ways to get to a house depending on traffic, detours, etc. The simpler the address system (linear), the easier it is to find what you need quickly.

Memory Protection Unit (MPU)

Chapter 2 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Although the Cortex-M0 does not include a full memory management unit (MMU), it includes an optional MPU. The MPU can provide basic memory protection for embedded applications by defining memory regions with different access rights (read/write/execute).

Detailed Explanation

The ARM Cortex-M0 features a Memory Protection Unit (MPU), which is a simplified alternative to a full Memory Management Unit (MMU). The MPU allows the system designer to divide memory into different regions, each with specific access rights. For instance, certain areas of memory can be set to allow read or write access only, preventing unauthorized access and enhancing system security. This is especially important in embedded systems, where sensitive data or critical code may reside in memory.

Examples & Analogies

Imagine a library where only certain people can access specific sections of books. The librarian (MPU) controls who can read or borrow books from different sections (memory regions). If someone tries to enter a restricted section, the librarian will stop them, ensuring that only authorized individuals can access sensitive materials.

Stack Pointer and Program Counter

Chapter 3 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

The Cortex-M0 uses a 32-bit stack pointer and program counter for managing execution flow, which is typical in many 32-bit processors.

Detailed Explanation

The Cortex-M0 processor makes use of two important registers: the stack pointer and the program counter. The stack pointer indicates the current top of the stack, which is a special area of memory used for storing temporary data such as function parameters and local variables while executing programs. The program counter, on the other hand, keeps track of the instruction that the processor is currently executing. These two components work together to ensure that the processor can execute instructions smoothly and efficiently.

Examples & Analogies

Think of the stack pointer like a plate stack in a cafeteria. The top plate represents the most recent one placed there (the current function), and you keep adding or removing plates from the top as you serve meals (execute functions). The program counter is like a chef who refers to a recipe book—always looking at the next instruction to make sure the meal is prepared correctly. This ensures that everything proceeds in an orderly fashion, without forgetting any steps.

Key Concepts

-

Linear Addressing: A simplified memory addressing where each address corresponds directly to physical memory locations, improving efficiency.

-

Memory Protection Unit (MPU): An optional component providing basic memory protection by defining access permissions for different regions.

-

Stack Pointer: Essential for managing local data and function calls by pointing to the top of the stack.

-

Program Counter: Manages the flow of program execution by holding the address of the next instruction.

Examples & Applications

In embedded systems, a linear addressing model allows programmers to easily allocate memory for sensor data.

When setting up memory protection for a critical firmware section, a developer configures the MPU to allow read access but deny write access.

Memory Aids

Interactive tools to help you remember key concepts

Rhymes

In the Cortex-M0, memory's linear, oh so neat, Makes programming easy and access quick on your feet.

Stories

Imagine a library where each book (memory location) is lined up in a row (linear addressing), making it easy to find what you need. The MPU acts like a librarian who won't let you read restricted sections!

Memory Tools

Remember the acronym 'MPS' for Memory Protection System, which reminds us of the functions: Manage, Protect, Simplify!

Acronyms

MPU = Memory Protection Unit, where 'Protect' is crucial to manage access and security.

Flash Cards

Glossary

- Linear Addressing

A memory addressing scheme where each address points directly to a corresponding physical memory location.

- Memory Protection Unit (MPU)

An optional unit that provides basic memory protection by defining memory regions with different access rights (read/write/execute).

- Stack Pointer

A register that points to the top of the current stack in memory, essential for managing function calls and local data.

- Program Counter

A register that holds the address of the next instruction to be executed in a program.

Reference links

Supplementary resources to enhance your learning experience.