The ARM Cortex-M0 Processor Architecture: Part 1

Enroll to start learning

You’ve not yet enrolled in this course. Please enroll for free to listen to audio lessons, classroom podcasts and take practice test.

Interactive Audio Lesson

Listen to a student-teacher conversation explaining the topic in a relatable way.

Introduction to ARM Cortex-M0 Processor

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Today, we're diving into the ARM Cortex-M0 processor, a 32-bit architecture developed for low-power and low-cost applications. Can anyone share where they think such a processor might be used?

It's probably used in small gadgets, like smartwatches or IoT devices.

How about in automotive applications?

Exactly! It's prevalent in consumer electronics, automotive, and medical devices. Now, what's special about its architecture?

I think it has something to do with being efficient at low clock speeds.

Correct! The Cortex-M0's design permits real-time performance even at lower frequencies. Remember the acronym 'LCP' for low power, cost-effective, and performance.

Okay, to summarize, the ARM Cortex-M0 is built for efficiency and low power, making it very suitable for resource-constrained applications.

Key Features of ARM Cortex-M0

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Now that we understand the introduction, let’s look into some of its key features. What’s the significance of using a low power consumption strategy in the Cortex-M0?

I think it's important for devices that rely on batteries.

Exactly! This design choice is critical in fulfilling the demands of battery-operated gadgets. Does anyone know what the Thumb-2 instruction set is?

Correct! The Thumb-2 instruction set aids in executing more efficient code. This is essential for devices with limited memory resources.

Lastly, the Harvard Architecture, which uses separate pathways for instructions and data, helps us achieve speedy access. Let's conclude this session: the ARM Cortex-M0’s key features — efficiency, low power, and a concise core size — make it optimal for embedded systems.

Cortex-M0 Internal Architecture

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Next, let's dive into the internal architecture of Cortex-M0. Who can remind me of the three stages of its pipeline architecture?

Fetch, Decode, and Execute!

Great! The pipeline design allows it to process commands more efficiently. Each stage plays a vital role: Fetching retrieves instructions, decoding interprets them, and executing performs the action. Why is this three-stage process beneficial?

It helps to reduce latency, right?

Yes! Additionally, it leads to higher throughput for simpler tasks, which is essential for embedded systems. Keep in mind the simple mnemonic 'FDE' to remember the stages: Fetch, Decode, Execute.

So in summary: the Cortex-M0's pipeline architecture enhances efficiency through its structured approach.

Interrupt System and Memory Management

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Now, onto the Cortex-M0's efficient interrupt system! Why might having a low-latency interrupt system be advantageous for embedded applications?

It can respond faster to external events, which is crucial for real-time systems.

Precisely! The Nested Vectored Interrupt Controller, or NVIC, is responsible for this. It maintains 8 priority levels for interrupts. What's the significance of this priority system?

It ensures that critical tasks are handled first!

Well said! It’s important to manage tasks based on urgency. Now, regarding memory management, does anyone understand how linear addressing simplifies things?

It avoids the complexities of virtual memory?

Exactly! So today, we've discussed the importance of an efficient interrupt system and simple memory management, crucial for embedded systems.

Introduction & Overview

Read summaries of the section's main ideas at different levels of detail.

Quick Overview

Standard

This section outlines the ARM Cortex-M0 processor’s architecture, emphasizing its low power consumption, efficient interrupt handling, and simple design that cater to the requirements of embedded and real-time applications. Key features like the Thumb-2 instruction set, Harvard architecture, and memory management techniques are also discussed.

Detailed

Detailed Summary of ARM Cortex-M0 Processor Architecture

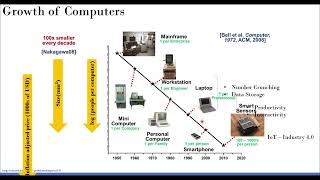

The ARM Cortex-M0 processor is a 32-bit architecture specifically tailored for low-power, cost-effective devices in the embedded systems market. It uniquely balances performance and energy efficiency, making it ideal for applications spanning consumer electronics, automotive systems, medical devices, and smart home technologies.

Key Features:

- Low Power Consumption: The Cortex-M0 is engineered for energy efficiency, crucial for battery-driven functionalities.

- Instruction Set: Its use of the Thumb-2 instruction set allows for smaller code size and efficient execution.

- Harvard Architecture: By having separate instruction and data paths, the processor enhances speed and performance.

- Simplicity: Its minimal core design reduces complexity and cost, which is essential for resource-constrained environments.

Performance Characteristics:

- The Cortex-M0 employs a 3-stage pipeline that facilitates instruction fetching, decoding, and execution, resulting in meaningful latency reduction and improved throughput.

- Memory management is straightforward with linear addressing and an optional MPU that allows basic memory protection.

- The processor supports an efficient bus system (AHB-Lite) and facilitates communication with multiple peripherals through established interfaces like UART, SPI, and I2C.

- It includes advanced power management techniques, enabling various low-power states that optimize energy usage based on operational needs.

In summary, the ARM Cortex-M0 processor's architecture is designed to cater specifically to the requirements of modern embedded systems, providing a robust foundation for low-power applications.

Youtube Videos

Audio Book

Dive deep into the subject with an immersive audiobook experience.

Introduction to the ARM Cortex-M0 Processor

Chapter 1 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

The ARM Cortex-M0 is a 32-bit processor designed for low-power, cost-effective applications. It is part of the ARM Cortex-M family, which targets microcontroller (MCU) markets with its optimized architecture for embedded systems.

● Overview: ARM Cortex-M0 is a simple, low-cost, low-power processor that is widely used in embedded systems, IoT devices, and other resource-constrained applications.

● Target Applications: Widely used in areas such as consumer electronics, automotive, medical devices, and home automation where small size, low power, and real-time performance are essential.

● Cortex-M0 Architecture: Designed to offer a 32-bit processor with a 16-bit instruction set and an efficient pipeline to provide high performance at low clock speeds.

Detailed Explanation

The ARM Cortex-M0 processor is a compact and efficient 32-bit chip aimed at affordable applications. It belongs to the family of ARM Cortex-M processors, specifically tailored towards microcontroller markets, focusing on lower power usage and smaller size. This processor is particularly suitable for devices that require real-time performance, like smart home devices and medical monitors. Its architecture is designed to run a 16-bit instruction set, meaning it can perform tasks efficiently while keeping power consumption low.

Examples & Analogies

Think of the ARM Cortex-M0 as a very efficient assistant. Just like how a personal assistant helps by handling tasks quickly and at a low cost, the Cortex-M0 manages to run multiple applications in a resource-constrained environment while using very little energy.

Key Features of ARM Cortex-M0

Chapter 2 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

This section covers the main features of the Cortex-M0 architecture, including its unique aspects that make it suitable for embedded applications.

● Low Power Consumption: Cortex-M0 is specifically designed for energy-efficient applications, making it ideal for battery-powered devices.

● Thumb-2 Instruction Set: Cortex-M0 uses the Thumb-2 instruction set, allowing for more efficient code execution with a smaller memory footprint.

● Harvard Architecture: The Cortex-M0 uses a Harvard architecture, where the instruction and data paths are separate, providing faster and more efficient access to both program code and data.

● Simplicity and Small Core Size: With a small and efficient design, the Cortex-M0 features a minimalistic approach to control and data flow, ensuring cost-effectiveness.

Detailed Explanation

One of the key highlights of the Cortex-M0 is its low power consumption, making it excellent for devices that run on batteries. It employs an instruction set known as Thumb-2, which enhances the efficiency of code execution, helping to save system resources. The Cortex-M0 also utilizes a Harvard architecture; this means that the paths for retrieving instructions and data are separate, allowing the processor to work more quickly. Furthermore, the processor's core is designed to be simple and small—this minimalistic approach not only saves space in the hardware but also makes it cheaper to manufacture.

Examples & Analogies

Imagine driving a lightweight electric car instead of a heavier, fuel-consuming vehicle. The Cortex-M0's design is like that lightweight car—it runs tasks smoothly while consuming minimal resources and energy.

ARM Cortex-M0 Processor Core Architecture

Chapter 3 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

The core of the ARM Cortex-M0 processor is designed for simplicity and efficiency while maintaining flexibility for different embedded applications.

● Pipeline Architecture: Cortex-M0 uses a 3-stage pipeline (Fetch, Decode, Execute), which provides a balance between performance and simplicity. This architecture helps to reduce latency and improve throughput for many embedded tasks.

○ Stage 1: Fetch: The instruction is fetched from memory.

○ Stage 2: Decode: The fetched instruction is decoded, and the necessary control signals are generated.

○ Stage 3: Execute: The instruction is executed, and the result is written back to the appropriate register or memory.

● Instruction Set: The Cortex-M0 uses the ARMv6-M architecture, which implements the 16-bit Thumb instruction set with optional 32-bit instructions. The Thumb-2 technology reduces the instruction size, improving both performance and memory efficiency.

● Register File: The ARM Cortex-M0 processor has a small register file to store data temporarily during processing. It includes 16 general-purpose 32-bit registers and a link register, which stores the return address for function calls.

Detailed Explanation

The Cortex-M0 core is built to be straightforward and efficient, which makes it adaptable for various uses. It implements a pipeline architecture with three phases—fetching the instruction from memory, decoding it, and then executing it. This means that while one instruction is being executed, the next can be fetched and prepared, resulting in enhanced efficiency. The core also utilizes the ARMv6-M architecture with a special instruction set that helps to minimize the size of the code, which in turn makes optimal use of the available memory. Additionally, the processor has a limited but powerful register file designed to quickly handle data.

Examples & Analogies

Think of the pipeline architecture like an efficient assembly line in a factory. Just as one worker gathers materials while another assembles a product, the Cortex-M0 can handle multiple instructions simultaneously, making the whole process quicker.

Key Concepts

-

Low Power Consumption: Essential for battery-operated devices.

-

Thumb-2 Instruction Set: Efficient code execution with reduced memory footprint.

-

Harvard Architecture: Separates instruction and data paths for enhanced performance.

-

Pipeline Architecture: A three-stage (Fetch, Decode, Execute) system that improves processing speed.

-

Interrupt System: Efficiently handles multiple interrupts with prioritization.

Examples & Applications

The Cortex-M0 processor is used in heart rate monitors which require immediate response to sensor data while also conserving battery life.

Smart home devices, like light switches that respond quickly to user inputs, leverage the interrupt handling capabilities of the Cortex-M0.

Memory Aids

Interactive tools to help you remember key concepts

Rhymes

In a little chip so small, power's saved for all, Cortex-M0 stands tall, for devices, it heeds the call.

Stories

Imagine a small robot that controls home appliances. With the ARM Cortex-M0's efficiency, it doesn't waste battery but reacts instantly when you press a button.

Memory Tools

Use the acronym 'FDE' to remember the CPU stages: Fetch, Decode, Execute.

Acronyms

LCP - Low Cost, Power-efficient, provides Performance.

Flash Cards

Glossary

- ARM CortexM0

A 32-bit processor designed for low-power and cost-effective embedded applications.

- Thumb2 Instruction Set

An instruction set that allows for more efficient execution with a smaller memory footprint.

- Harvard Architecture

A microarchitecture that separates instruction and data paths for improved performance.

- Pipeline Architecture

A technique where multiple instruction stages are executed simultaneously to increase processing efficiency.

- Interrupt Controller

A component allowing the processor to respond quickly to external events.

- Memory Protection Unit (MPU)

A system component that provides basic memory protection by defining access rights.

Reference links

Supplementary resources to enhance your learning experience.