AXI4 Bus Protocol Details

Interactive Audio Lesson

Listen to a student-teacher conversation explaining the topic in a relatable way.

Key Channels in AXI4

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Today, we will explore the key channels in the AXI4 protocol. AXI4 uses multiple channels to manage the flow of data. Can anyone name the first channel?

Is it the Read Address Channel?

Correct! The Read Address Channel, or AR, is used to send addresses and control information for read operations. What do you think is the role of the Write Address Channel?

It probably sends addresses for write operations?

Exactly! The Write Address Channel, or AW, handles that. Remember, AXI4 channels are key to ensuring efficient communication. Here's a mnemonic to help you remember the five channels: 'Read A Works Really Well.' It stands for Read Address, Write Address, Read Data, Write Data, and Write Response.

So, the mnemonic covers all five channels?

Yes! Now, can someone explain what each channel carries?

Read Address carries the address for reads, Read Data carries the data back, Write Address carries the address for writes, Write Data carries the actual data, and Write Response tells if the write was successful!

Excellent! You all understand the channels of AXI4 well.

Handshaking Mechanisms

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Now, let’s move on to handshaking mechanisms in AXI4. This is crucial for synchronizing data transfer. Can anyone tell me how handshaking works?

Is it about ensuring both the master and slave are ready to send and receive data?

Spot on! The signals like valid, ready, and response help synchronize communication. What are the implications of not having proper handshaking?

It could lead to data not being received properly or even lost!

Exactly! Think of it like a conversation where both people need to agree before speaking. If one person interrupts too soon, the message can be lost. Remember: 'Validate, Readiness, Response' – this can help you remember the key signals!

Got it! It’s like making sure both parties agree before talking.

Exactly! Now, how do you think QoS fits into this picture?

Burst Types

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Next, let’s explore burst types in AXI4. There are three main types. Who can name them?

Fixed, Incrementing, and Wrapping bursts!

Correct! Let’s break them down. What is a Fixed Burst?

The size and address stay the same during the burst.

Exactly! What about Incrementing Bursts?

The address increases between transfers!

Very good! Lastly, can anyone explain the Wrapping Burst?

The address wraps around after reaching a limit!

Yes! That’s useful for circular buffers. To help remember, think of a ‘Fixed Price, Incrementing Costs, Wrapping Up’ – it’s a funny way to recall the bursts.

Quality of Service (QoS)

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Finally, let’s discuss Quality of Service or QoS. Why do you think QoS is important in AXI4?

To prioritize critical data transfers!

Exactly! QoS allows the system to treat certain types of traffic with higher priority. Can you think of examples in real life where prioritizing is crucial?

Emergency vehicles need precedence in traffic.

Great example! Let's create a memory aid for QoS: 'Quick on Service' – that can help remind us of its purpose in data management.

So, QoS ensures that important data gets delivered first?

Precisely! Remember, prioritizing data transfer is essential in many systems, making your communication much more efficient.

Introduction & Overview

Read summaries of the section's main ideas at different levels of detail.

Quick Overview

Standard

The AXI4 bus protocol includes various channels for effective communication between components, detailed handshaking mechanisms for synchronization, different types of burst transactions, and quality of service capabilities to prioritize data transfer. These features contribute significantly to the high performance, scalability, and flexibility of ARM-based SoCs.

Detailed

AXI4 Bus Protocol Details

The AXI4 protocol is designed to ensure high performance in ARM-based Systems on Chip (SoCs). It accomplishes this through several key mechanisms:

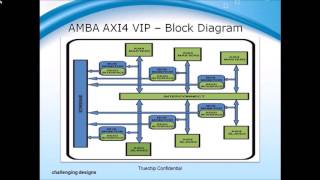

- Key Channels: AXI4 comprises five primary channels:

- Read Address Channel (AR): Responsible for sending read addresses and control information during read operations.

- Read Data Channel (R): Carries the data retrieved from a read operation to the master device.

- Write Address Channel (AW): Transmits addresses and control signals for write operations.

- Write Data Channel (W): Delivers the actual data being written to the slave device.

- Write Response Channel (B): Provides responses to indicate the success or failure of a write operation.

- Handshaking Mechanisms: Handshaking is essential for ensuring synchronous communication between the master and slave components. It employs signals such as valid, ready, response, and address signals, allowing both parties to coordinate the flow of data effectively.

- Burst Types: AXI4 supports different burst types, allowing efficient data transfer. These types include:

- Fixed Burst: The data size and address remain constant throughout the burst.

- Incrementing Burst: The address changes incrementally with each transfer.

- Wrapping Burst: The address wraps after reaching a specific boundary, optimizing memory usage in circular buffers.

- Quality of Service (QoS): The QoS feature enables prioritized data transfer so that critical data can be sent before less critical traffic, thus optimizing system performance in varying conditions.

With these capabilities, the AXI4 protocol stands as a robust choice for high-performance, flexible communication in modern SoC design.

Youtube Videos

Audio Book

Dive deep into the subject with an immersive audiobook experience.

Key Channels in AXI4

Chapter 1 of 4

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

AXI4 defines multiple channels for handling different types of signals between master and slave components. These channels are:

- Read Address Channel (AR): Carries the address and control information for read operations.

- Read Data Channel (R): Carries the data returned from a read operation.

- Write Address Channel (AW): Carries the address and control information for write operations.

- Write Data Channel (W): Carries the data for write operations.

- Write Response Channel (B): Carries the response for write operations, indicating whether the write was successful or not.

Detailed Explanation

In AXI4, communication happens through several dedicated channels. Each channel serves a specific purpose:

- Read Address Channel (AR): When a master device wants to read data, it sends the address of the requested data through this channel.

- Read Data Channel (R): After the data is requested, the slave device sends the requested data back to the master through this channel.

- Write Address Channel (AW): When the master wants to write data, it sends the address where it wants to store the data using this channel.

- Write Data Channel (W): This channel is used to transfer the actual data that the master wants to write to the slave.

- Write Response Channel (B): Once the write operation is completed, the slave device sends back a response indicating whether the write was successful.

Examples & Analogies

Imagine a library where the librarian (the slave) handles requests from various patrons (the masters). If a patron wants a book, they fill out a request form (AR channel). Once the book is found, the librarian gives it to the patron (R channel). If the patron wants to return a book, they fill out a return form (AW channel) and hand over the book (W channel). After processing the return, the librarian informs the patron that the return was successful (B channel).

Handshaking Mechanisms

Chapter 2 of 4

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

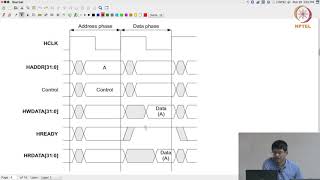

AXI4 uses a handshaking protocol where each channel has a set of signals to indicate readiness for data transfer, such as valid, ready, response, and address signals. This ensures synchronization between the master and slave components during communication.

Detailed Explanation

Handshaking in AXI4 is crucial for ensuring that both the master and slave components are ready to exchange data without conflicts. Each channel has specific signals:

- Valid signal: This indicates that the valid data is present and ready to be used.

- Ready signal: This indicates that the receiving component (master or slave) is ready to accept the data.

- Response signal: This is used in write operations to confirm the result of the data transfer.

- Address signal: Used to specify where data is to be read from or written to.

This process allows both components to communicate effectively, pacing the data exchange correctly without overflowing any buffers.

Examples & Analogies

Think of a conversation between two friends. Before one friend starts speaking, they might check if the other is paying attention (ready). Once they are sure, only then do they begin talking (valid). The other friend can nod to confirm they are listening and ready to respond. This back-and-forth ensures that both friends are synchronized in the conversation.

Burst Types

Chapter 3 of 4

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

AXI4 defines several burst types to optimize data transfer:

- Fixed Burst: The burst size and address do not change during the burst.

- Incrementing Burst: The address increments between each transfer in the burst.

- Wrapping Burst: The address wraps around after a specific boundary, useful for circular buffers or memory with limited address space.

Detailed Explanation

AXI4 supports different burst types to increase efficiency and flexibility in data transfers:

- Fixed Burst: In this case, the addresses and sizes of data being transferred remain constant. It’s useful when you are sending a consistent block of data.

- Incrementing Burst: Here, the address changes incrementally for each data transfer, allowing efficient sequential data access, like reading an array of values in memory.

- Wrapping Burst: This method allows addresses to wrap around, which is particularly effective when working with buffers that have a fixed size, ensuring you don't exceed the buffer limits.

Examples & Analogies

Picture a line of people at a concert jumping up and down together. A fixed burst would be like everyone jumping at the same height consistently. An incrementing burst is like each person jumping a bit higher each time; they start at different heights but keep increasing together. A wrapping burst would be akin to dancers who, after reaching the end of the stage, travel back to continue their movements in a loop.

Quality of Service (QoS)

Chapter 4 of 4

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

AXI4 supports QoS to prioritize traffic on the bus, ensuring that critical data can be given higher priority in systems with varying performance requirements.

Detailed Explanation

Quality of Service (QoS) is an important feature in AXI4 that helps manage the flow of data based on its urgency or importance. In a system, various types of data may have different requirements:

- Critical data may need to be processed immediately to avoid delays in time-sensitive operations.

- Less urgent data can be processed later.

Through QoS settings, the AXI4 protocol can prioritize critical packets over less important ones, ensuring a more reliable and efficient system overall.

Examples & Analogies

Imagine a doctor in a hospital; a critical patient (high-priority data) will be attended to immediately, while someone with a minor ailment (low-priority data) will wait. The hospital staff has protocols to prioritize patients based on the severity of their conditions, ensuring that urgent needs are addressed swiftly.

Key Concepts

-

Channels: Components of AXI4 like Read Address, Write Address, etc., for data management.

-

Handshaking: Synchronization between components ensuring proper data transfer.

-

Burst Types: Modes of data transfer—Fixed, Incrementing, and Wrapping bursts.

-

Quality of Service: Mechanism prioritizing traffic to ensure efficient communication.

Examples & Applications

In a video processing system, the Read Data Channel retrieves frames from memory using the AR channel while the Write Data Channel pushes processed data back using the W channel.

Utilizing QoS in an automotive system allows critical sensor data to be transmitted at higher priority than less time-sensitive data like infotainment system updates.

Memory Aids

Interactive tools to help you remember key concepts

Rhymes

AR and AW, handling addresses anew; R brings back what you need, W sends data to succeed.

Stories

Imagine a post office where AR is the keeper of addresses, R delivers packages (data), AW sends mailing orders, W carries outgoing materials, and B confirms delivery!

Memory Tools

Remember 'A Really Well' for AR, AW, R, W, and B channels.

Acronyms

BARS - for understanding the basic channels

for Write Response

for Write Address

for Read Data

for Slave channel.

Flash Cards

Glossary

- Read Address Channel (AR)

Channel in AXI4 that carries address and control information for read operations.

- Read Data Channel (R)

Channel in AXI4 that carries the data returned from a read operation.

- Write Address Channel (AW)

Channel in AXI4 that carries address and control information for write operations.

- Write Data Channel (W)

Channel in AXI4 that carries the actual data for write operations.

- Write Response Channel (B)

Channel in AXI4 that carries the response for write operations, indicating success or failure.

- Handshaking

Protocol ensuring synchronization between master and slave components via signals like valid and ready.

- Burst Types

Different transaction modes in AXI4 defining how data is transferred in bursts.

- Quality of Service (QoS)

Feature in AXI4 that prioritizes traffic on the bus, ensuring critical data has higher priority.

Reference links

Supplementary resources to enhance your learning experience.