Integrating DDR Memory Controller in SoCs

Interactive Audio Lesson

Listen to a student-teacher conversation explaining the topic in a relatable way.

Introduction to DDR Memory Controller Integration

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Today, we will delve into how DDR memory controllers are integrated in ARM-based SoCs. Let's start with why a DDR memory controller is crucial in these designs. Who can remind us what a DDR memory controller does?

It manages the read and write operations to DDR memory, ensuring data is transferred efficiently.

Exactly! It facilitates high-speed data transfers. Now, does anyone know what the AMBA AXI4 interface is used for?

It allows communication between the processor and peripherals like the DDR memory.

Correct! One key benefit of using AXI4 is its ability to provide high bandwidth and low latency. Can anyone explain how multi-channel memory controllers enhance system performance?

They allow multiple data streams to be processed at once, increasing overall memory bandwidth!

Brilliant! In summary, integrating a DDR memory controller into an SoC via AXI4 facilitates efficient memory operations, significantly improving performance.

Performance Considerations

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

In our last session, we touched on multi-channel memory controllers. Let's discuss performance considerations in greater detail. Why is it important to balance memory clock speed with bus width and latency?

If we don’t balance those, we could end up with a bottleneck, reducing the system's overall efficiency.

Exactly! A bottleneck can severely impact system performance. Now, remember low-power DDR variants like LPDDR? Why are they significant in certain applications?

They are designed for energy efficiency, making them ideal for mobile and battery-powered devices.

That's right! As a summary, focusing on performance considerations helps in optimizing SoC design, especially in applications where power efficiency is critical.

Applications of Integrated DDR Memory Controllers

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Now that we understand the integration and performance aspects, let's explore some real-world applications of integrated DDR memory controllers. Can someone give me an example?

Smartphones use DDR memory controllers for efficient multitasking and fast access to applications.

Great example! And how about automotive systems? What role do DDR memory controllers play there?

They handle high-bandwidth data needs for infotainment systems and advanced driver-assistance systems.

Exactly! In summary, DDR memory controllers are essential for enabling high-performance applications across various industries.

Introduction & Overview

Read summaries of the section's main ideas at different levels of detail.

Quick Overview

Standard

The section details the integration of the DDR memory controller within ARM-based SoCs via interconnects like AMBA AXI4, emphasizing the advantages of using multi-channel controllers for increased bandwidth and the significance of performance considerations in design.

Detailed

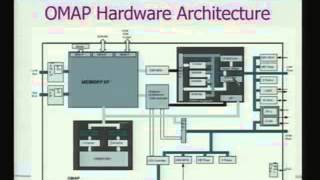

Integrating DDR Memory Controller in SoCs

In ARM-based System-on-Chips (SoCs), the DDR memory controller is a critical component that facilitates high-speed memory operations. This section describes how the DDR controller is integrated with other system components, particularly through the AMBA AXI4 interface, which allows efficient communication between the processor and memory. The use of multi-channel memory controllers is emphasized, as they enhance memory bandwidth by enabling concurrent operations across multiple data streams. Additionally, considerations around performance, such as balancing memory clock speed and latency, are crucial in achieving optimal performance. The integration of low-power DDR variants like LPDDR is also noted, catering to energy-efficient applications, especially in mobile and battery-operated devices. Overall, understanding these integrations is vital for designing effective SoCs capable of handling various demanding applications.

Youtube Videos

Audio Book

Dive deep into the subject with an immersive audiobook experience.

AMBA AXI4 Interface

Chapter 1 of 4

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

The DDR memory controller typically uses the AXI4 or AXI4-Lite protocol to communicate with the CPU or other system components. The AXI4 interconnect provides high-bandwidth, low-latency data transfer between the processor and the DDR memory.

Detailed Explanation

This chunk discusses the AMBA AXI4 interface, which is a communication standard used in SoCs. The DDR memory controller employs the AXI4 or AXI4-Lite protocol to facilitate communication with the CPU. AXI4 is favored for its ability to manage high-speed data transfer efficiently. By using this interface, the DDR memory controller can quickly send and receive data from the processor, which is necessary for tasks requiring access to large amounts of memory.

Examples & Analogies

Imagine a busy postal service where trucks (the AXI4 interface) transport packages (data) between a central hub (the processor) and various storage facilities (DDR memory). The trucks are designed to navigate efficiently, ensuring that deliveries happen quickly without delays.

Multi-channel Memory Controllers

Chapter 2 of 4

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

In high-performance SoCs, multi-channel DDR controllers are often used to increase the memory bandwidth. Each channel can operate independently, allowing the system to handle multiple data streams concurrently.

Detailed Explanation

This chunk highlights the use of multi-channel DDR controllers in advanced SoC designs. By utilizing multiple channels, the memory controller can read from or write to different memory locations simultaneously, effectively boosting the overall memory bandwidth. This parallelism enhances system performance, especially in applications requiring rapid data processing, such as gaming or video editing.

Examples & Analogies

Think of a multi-channel memory controller like a multi-lane highway. Each lane can accommodate its own flow of traffic (data), allowing for more cars (data streams) to travel at the same time. This reduces congestion and speeds up overall travel, similar to how multi-channel controllers enhance memory access speeds.

Performance Considerations

Chapter 3 of 4

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

When integrating a DDR controller into an SoC, it is important to balance the memory clock speed, bus width, and latency to ensure that the system performs optimally for the target application.

Detailed Explanation

This chunk emphasizes the importance of various technical factors when integrating a DDR memory controller into an SoC. The clock speed determines how fast the memory can operate, the bus width affects the amount of data that can be transferred at once, and latency refers to the delay between initiating a data request and receiving the data. A good balance among these factors is crucial for achieving optimal performance based on the application needs.

Examples & Analogies

Consider a chef preparing multiple dishes in a restaurant kitchen. If the chef (DDR controller) has all the tools (memory clock speed, bus width) but mismanages the cooking times (latency), some dishes might be served late. A well-balanced kitchen ensures all dishes are prepared and served promptly, just as a well-integrated DDR controller ensures efficient memory operations.

Power Management

Chapter 4 of 4

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Low-power DDR variants such as LPDDR2 or LPDDR4 can be integrated into the memory controller for energy-efficient applications, particularly in mobile or battery-powered devices.

Detailed Explanation

This chunk discusses the integration of low-power DDR variants into memory controllers to enhance energy efficiency, especially in mobile devices where battery life is critical. These low-power options, such as LPDDR2 and LPDDR4, are designed to consume less power while still providing sufficient performance for everyday tasks, thus extending the operational time of battery-powered devices.

Examples & Analogies

Imagine a smartphone designed with energy-efficient components like LED lights that use less electricity. Just as these lights prolong battery life by consuming less energy, low-power DDR memory helps devices run longer on a single charge without sacrificing necessary performance.

Key Concepts

-

Integration of DDR Memory Controller: Essential for managing high-speed memory operations in SoCs.

-

AMBA AXI4 Protocol: Enables efficient communication between processor and memory, crucial for performance.

-

Multi-channel Controllers: Enhances bandwidth and performance by managing multiple data streams concurrently.

Examples & Applications

In smartphones, DDR memory controllers support multitasking by ensuring fast memory access.

Automotive infotainment systems utilize DDR memory controllers to handle large data transfers effectively.

Memory Aids

Interactive tools to help you remember key concepts

Rhymes

DDR is fast, with speeds that last; Integration helps memory, performance is vast.

Stories

Imagine a bus running between a school (the processor) and a library (DDR memory). The conductors (DDR memory controllers) ensure all students get the books quickly, enhancing learning.

Memory Tools

Remember 'MCP' for Multi-Channel Performance: More channels, higher speeds.

Acronyms

AAMP - AXI4, AMBA, Multi-channel, Performance - key factors for SoC design.

Flash Cards

Glossary

- DDR Memory Controller

A component in SoCs that manages read and write operations to DDR memory, ensuring efficient data transfer.

- AMBA AXI4

An interconnect protocol that allows high-bandwidth and low-latency communication between the processor and memory or peripherals.

- Multichannel Memory Controller

A type of memory controller that operates multiple channels independently to increase memory bandwidth.

- Power Management

Techniques or methods used to reduce power consumption, especially in portable or battery-operated devices.

- LowPower DDR (LPDDR)

A type of DDR memory designed for energy efficiency, commonly used in mobile devices.

Reference links

Supplementary resources to enhance your learning experience.