Problem Statement

Enroll to start learning

You’ve not yet enrolled in this course. Please enroll for free to listen to audio lessons, classroom podcasts and take practice test.

Interactive Audio Lesson

Listen to a student-teacher conversation explaining the topic in a relatable way.

Minimizing Power Consumption

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Today, we will discuss the first challenge in our problem statement: how to minimize power consumption without sacrificing speed or functionality. Power consumption is critical as we design more complex circuits.

Why is it important to minimize power consumption?

Great question! Minimizing power consumption is essential because it prolongs the battery life of mobile devices, reduces heat generation, enhances reliability, and lowers energy costs.

Can you explain how we can achieve this?

Sure! We can utilize techniques such as reducing supply voltage, optimizing circuit design, and using more efficient technologies like FinFETs. Remember the acronym 'POWER' — it stands for 'Performance Optimization with Efficient Resources.'

Got it! So the goal is to maintain performance while using fewer resources, right?

Exactly! That's a key point; power and performance must go hand-in-hand.

Isn't there a trade-off between power and speed?

Yes, indeed! If we reduce voltage too much, we may slow down the speed of our circuits. That’s where the balancing act comes into play!

In summary, we must minimize power while maximizing performance through efficient design choices.

Understanding Leakage Power

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Now let's explore leakage power, especially as devices shrink below 45nm. Leakage becomes more significant at this scale. What do you think leakage power means?

Is it the power that leaks when the device is not active?

Exactly! Leakage power can drain battery life even when a device is in standby mode. Factors contributing to leakage include subthreshold leakage and gate oxide leakage.

Good question! Static power can be calculated simply as the product of leakage current and supply voltage. Knowing this, designers can target key design areas to reduce these forms of leakage.

What trade-offs are there when trying to reduce it?

Reducing leakage often involves increasing threshold voltage, which can slow switching speeds. It’s a complex dance between power, performance, and functional requirements!

To recap, leakage power needs to be controlled carefully, especially as technology nodes shrink, impacting overall device performance.

Evaluating CMOS and FinFET Technologies

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Let’s look at how CMOS and FinFET behave differently under the constraints we’ve discussed. What’s your understanding of these technologies?

CMOS is the standard technology, but I've heard FinFET is newer and more efficient.

Exactly! FinFET improves control over the channel, thus reducing leakage and dynamic power. If only we could choose one, it would solve our problems, right?

But isn't FinFET more expensive to manufacture?

Right again! The trade-off is between enhanced efficiency and cost. Designers must consider the specific application needs when choosing between these technologies.

So when should we use FinFET?

FinFET is better for high-performance applications that require low-power consumption, like mobile devices and high-density servers. But for lower-cost, simpler applications, CMOS might still be preferred.

To summarize today's key point: selecting between CMOS and FinFET involves evaluating their distinct advantages under specific design constraints.

Introduction & Overview

Read summaries of the section's main ideas at different levels of detail.

Quick Overview

Standard

As device complexity and miniaturization increase, designers must address the interconnected challenges of minimizing power consumption while preserving speed and functionality, balancing multiple factors such as dynamic power, leakage, cost, and area, particularly within the context of CMOS and FinFET technologies.

Detailed

Problem Statement

In the rapidly evolving landscape of semiconductor design, as both circuit complexity increases and device dimensions shrink, engineers face several critical challenges. Notably, they must focus on minimizing power consumption without compromising speed or inherent functionality. This optimization must occur while striking a balance among various competing factors:

- Dynamic Power: The power consumed during active operation must be minimal to improve efficiency.

- Leakage Power: Static leakage, particularly in deep submicron technologies, poses a significant challenge.

- Area and Cost: The physical layout should remain efficient in terms of space while also being economically viable.

Furthermore, the distinct behaviors of CMOS and FinFET technologies under these constraints must be thoroughly evaluated since the optimal design choices can vary significantly based on the application, such as mobile devices or servers. The significance of this problem statement lies in its emphasis on understanding technology limitations and making informed decisions to achieve effective low-power design.

Youtube Videos

Audio Book

Dive deep into the subject with an immersive audiobook experience.

Minimizing Power and Maintaining Functionality

Chapter 1 of 4

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

As circuit complexity grows and devices shrink, designers must: ● Minimize power without sacrificing speed or functionality.

Detailed Explanation

As electronic devices become smaller and more complex, it becomes crucial for designers to reduce the amount of power these devices consume. However, they must do this without affecting the performance of the devices, meaning the speed at which they operate and their functional capabilities should remain intact. This creates a challenge, particularly in mobile devices where battery life is critical. Hence, power management strategies must be carefully crafted to achieve this balance.

Examples & Analogies

Think of a car that needs to be both fuel-efficient and fast. If the car is designed to use less fuel, it might slow down. However, if engineers can find a way to make the engine run efficiently without reducing speed, it will be desirable for consumers who want to travel quickly without stopping frequently at gas stations.

Balancing Power Components

Chapter 2 of 4

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

● Balance dynamic power, leakage, area, and cost.

Detailed Explanation

Designers face the task of balancing various components of power consumption, including dynamic power (the power consumed during operation), static leakage power (power lost when the device is not switching), the size of the circuit (area), and the manufacturing costs. Each of these factors can influence not only the performance but also the practicality of the design in real-world applications. For example, a design that minimizes leakage may increase area, leading to higher costs, which is something designers must navigate carefully.

Examples & Analogies

Imagine trying to build a small house on a budget. You could use cheaper materials (reducing cost), but that might compromise durability (increasing leakage). Alternatively, if you use high-end materials, the budget might increase, but the house will last longer and be more energy-efficient. A good architect must balance these elements to achieve the best overall outcome for the homeowner.

Understanding Technology Behavior

Chapter 3 of 4

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

● Evaluate how CMOS and FinFET behave differently under these constraints.

Detailed Explanation

It’s important for designers to understand the differences in performance and power consumption characteristics between CMOS (Complementary Metal-Oxide-Semiconductor) and FinFET (Fin Field-Effect Transistor) technologies. Each technology responds differently to power management techniques and design constraints. While CMOS has been widely used, FinFETs offer advantages in terms of reduced leakage and better control of short-channel effects, which can potentially lead to better power efficiency. This evaluation guides the choice of technology based on the specific needs of the use case.

Examples & Analogies

Consider choosing between different brands of running shoes. Some brands are better for long-distance running, providing comfort and durability (like FinFETs in power efficiency), while others might be more about stability and control, suitable for sprinting (like CMOS). Understanding which shoes are better for your specific type of running can enhance your performance and minimize discomfort, much like how selecting the right technology improves circuit design.

Optimizing for Specific Use Cases

Chapter 4 of 4

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

The challenge is to optimize designs for specific use cases (e.g., mobile, server, IoT) while understanding the inherent trade-offs in each technology.

Detailed Explanation

Designers must also consider the specific use case of their circuits, as different applications demand different performance, power, and cost characteristics. For instance, a mobile device requires low power consumption for extended battery life, while a server might prioritize speed and processing power even if it means higher power usage. This necessitates an understanding of the trade-offs involved in choosing between CMOS and FinFET technologies, ensuring that each design is tailored to its intended application to maximize efficiency and performance.

Examples & Analogies

Think about a multi-tool that combines a knife, screwdriver, and bottle opener. If you need to slice bread, it’s best to use the knife, even though the multi-tool has other functions. Similarly, in circuit design, selecting the right technology like CMOS or FinFET based on what you need most (like low power or high speed) is crucial to achieving the best outcome for specific applications.

Key Concepts

-

Power Consumption: Key challenge in circuit design focused on reducing energy use while maintaining performance.

-

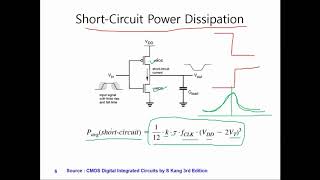

Dynamic Power: Power used when circuits switch states, directly affected by clock speed and voltage.

-

Leakage Power: Power dissipated in idle states, increasingly significant at smaller technology nodes.

-

Trade-offs: Necessity of balancing power, performance, cost, and area when choosing technologies like CMOS and FinFET.

Examples & Applications

Optimizing a mobile device design to maximize battery life while maintaining speed involves analyzing power consumption and selecting the right technology.

A server application might favor FinFET for its lower leakage and better efficiency, even at a higher cost, compared to CMOS.

Memory Aids

Interactive tools to help you remember key concepts

Rhymes

To save power, make haste; dynamic voltage, don’t waste!

Stories

Imagine two engineers, one using CMOS and the other FinFET. The FinFET engineer saves power and speed but spends more money, while the CMOS engineer has lower cost but faces leakage issues. Their choices illustrate the trade-offs they must navigate!

Memory Tools

To remember leakage: 'Simple Methods Avoid Costly Energy,' representing methods to minimize leakage.

Acronyms

Remember 'P.E.A.C.E.' for the design trade-offs

Power

Efficiency

Area

Cost

and Environment.

Flash Cards

Glossary

- CMOS

Complementary Metal-Oxide-Semiconductor; a technology for constructing integrated circuits.

- FinFET

Fin Field-Effect Transistor; a type of 3D semiconductor device that improves control over the channel.

- Dynamic Power

Power consumed when the circuit is active and switching states.

- Leakage Power

Static power consumed by the device when it is not switching, often due to leakage currents.

Reference links

Supplementary resources to enhance your learning experience.