Introduction to Low Power Circuit Design with CMOS and FinFETs

Enroll to start learning

You’ve not yet enrolled in this course. Please enroll for free to listen to audio lessons, classroom podcasts and take practice test.

Interactive Audio Lesson

Listen to a student-teacher conversation explaining the topic in a relatable way.

The Need for Low-Power Design

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

As we start our discussion today, let's think about the world around us. Why do you think low-power design is becoming so important in electronics?

I think it's because most devices run on batteries, and we don't want them to drain quickly.

Exactly! The demand for battery-powered devices indeed drives the need for low-power designs. Remember the acronym *B.E.E.*: Battery Efficiency and Energy conservation! How might high power consumption affect device usage?

It can lead to frequent recharging and might shorten the overall lifespan of the device.

Great point! It's also about improving user experience. In summary, low-power design is critical for extending battery life and enhancing device functionality.

Power Dissipation in CMOS Circuits

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Now, let's dive into CMOS circuits. Does anyone know the different types of power dissipation we can encounter?

There’s dynamic power and static power, right?

Exactly! Dynamic power is linked to switching activity. We can remember it using *'D.S.S.'*: Dynamic Switch Signal. It can be calculated using the formula: P_dyn = αCLVdd²f. What does each symbol stand for?

Alpha is the switching activity factor, CL is the load capacitance, Vdd is the supply voltage, and f is the operating frequency.

Correct! Static power arises from leakage currents. Can anyone explain why leakage becomes crucial as transistors get smaller?

Because it increases with smaller sizes, leading to higher power consumption when many transistors are used together!

Well said! Always consider the implications of scaling down in design.

Low-Power Techniques in CMOS Design

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

In our previous discussion, we covered the types of power dissipation in CMOS. Let's look at some strategies to counteract these. What techniques can we use?

I've heard of voltage scaling being effective.

Yes! Voltage Scaling is a key technique. Remember the phrase *'Lower the Voltage, Lower the Power'*! Besides that, have you heard about clock gating?

That's when inactive modules don't receive clock signals, right?

Right! This helps in reducing power further. Lastly, let’s think about dynamic voltage and frequency scaling. Can anyone explain how this works?

It adjusts the voltage and frequency based on workload, helping save power when full performance isn't needed.

Absolutely! So, using these techniques can lead to significant power savings and improve overall efficiency.

Transition to FinFETs

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Now, let's consider the shift from CMOS to FinFET technology. Why do you think designers prefer FinFETs at smaller nodes?

Because they help control leakage better and have improved drive strength?

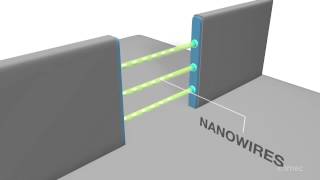

Exactly! FinFETs enhance gate control, reducing leakage, which becomes a bigger issue in nodes smaller than 22nm. Remember the mnemonic *'F.L.E.E.*': FinFET Lowers Electrostatic Leakage Effectively. How does the structure of FinFETs help improve performance?

The gate wraps around the silicon fin, allowing better control without increasing the size.

Great insight! This leads to improved performance without compromising power efficiency. Let's summarize the benefits of switching to FinFET technology.

Introduction & Overview

Read summaries of the section's main ideas at different levels of detail.

Quick Overview

Standard

In this section, we explore the fundamentals of low power circuit design, particularly utilizing CMOS and FinFET technologies. It emphasizes the necessity of low-power design in the context of increasing functionality and performance in integrated circuits, alongside strategies and techniques to manage power dissipation.

Detailed

Introduction to Low Power Circuit Design with CMOS and FinFETs

In the realm of electronics, the importance of low power circuit design is becoming increasingly paramount due to the proliferation of battery-powered devices and the need for energy-efficient systems. This section lays the groundwork for understanding low power circuit design by outlining:

- Need for Low-Power Design: Highlights the growing power consumption in integrated circuits (ICs) with advanced functionality and performance demands.

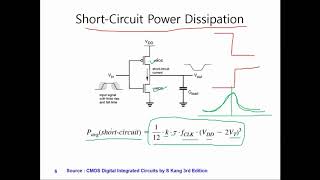

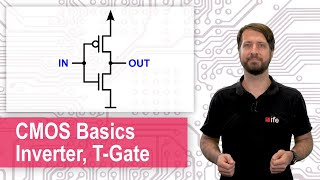

- Power Dissipation in CMOS Circuits: Details the components contributing to power consumption including dynamic power, static power, and short-circuit power, along with relevant equations.

- Low-Power Techniques: Explores various strategies such as voltage scaling, clock gating, and power gating to reduce power usage in CMOS designs.

- Transition to FinFETs: Addresses the advantages of FinFET technology over traditional CMOS, especially at smaller nodes, focusing on its reduced leakage and enhanced control due to the structure that wraps the gate around the channel.

- Practical Examples: Provides a design example of an inverter circuit comparing power profiles of CMOS versus FinFET, showcasing substantial power savings.

In closing, this section asserts that low-power design is essential in modern VLSI systems and the transition to FinFETs represents a significant advancement to sustain Moore’s Law amidst power constraints.

Youtube Videos

Audio Book

Dive deep into the subject with an immersive audiobook experience.

Fundamentals of Low Power Circuit Design

Chapter 1 of 4

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

In this chapter, we introduce the fundamentals of low power circuit design, focusing specifically on CMOS (Complementary Metal-Oxide-Semiconductor) and FinFET (Fin Field-Effect Transistor) technologies. With the proliferation of battery-powered devices and the rising demand for energy-efficient systems, minimizing power consumption has become a critical design objective.

Detailed Explanation

This chunk introduces foundational concepts in low power circuit design, highlighting two major technologies: CMOS and FinFET. Low power design is crucial because as more devices are powered by batteries, especially portable ones, the need for power efficiency increases. Designers strive to create circuits that use less power while still meeting performance requirements.

Examples & Analogies

Think of power consumption in circuit design like fuel efficiency in cars. Just as consumers want cars that consume less fuel for longer journeys, engineers want circuits that use less power for longer battery life. If a device consumes too much power, it needs to be recharged frequently, which can be inconvenient.

Need for Low-Power Design

Chapter 2 of 4

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

We will discuss the need for low-power design, the power dissipation sources in digital circuits, and the transition from CMOS to FinFETs to overcome leakage issues in advanced technology nodes. This sets the foundation for understanding practical low-power design techniques used in modern integrated circuits.

Detailed Explanation

The need for low-power design arises from the limitations of traditional technologies like CMOS, especially as we move to smaller technology nodes. Higher power dissipation can lead to inefficiencies, overheating, and shorter device life. FinFET technology helps address these challenges, especially with leakage currents that can waste power in smaller transistors.

Examples & Analogies

Imagine trying to keep a plant healthy in a small pot; if the pot is too small, the plant can't grow well, and it might consume more water than necessary. Similarly, as transistors get smaller, managing power effectively becomes essential to maintain 'plant' health in circuit design.

Power Dissipation Sources

Chapter 3 of 4

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Power consumption in integrated circuits (ICs) is growing with increased functionality and performance demands. Traditional CMOS technology suffers from:

● Dynamic Power Dissipation due to frequent switching.

● Static Power Dissipation due to subthreshold leakage currents.

● Increased Heat and Reduced Battery Life, especially in portable devices.

Detailed Explanation

Power consumption in circuits can be divided into three key types of dissipation: dynamic power, which occurs from the switching of states (turning on and off), static power, which is the power used even when the circuit isn’t switched on due to leakage currents, and the overall heat generated, which can affect device performance and lifespan. These factors create significant challenges for designers aiming to improve performance while keeping energy use low.

Examples & Analogies

Consider a school with multiple classes that frequently change subjects. Every time students switch classes (dynamic), they are using more energy, similar to how circuits use dynamic power. If some students don’t need to switch classes at all but still use resources (static), that’s akin to static power dissipation. Just like the school that needs to manage student movement efficiently for energy-saving, circuits must minimize both types of power.

Transition from CMOS to FinFET

Chapter 4 of 4

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Designers must explore low-power strategies using CMOS optimizations and transition to FinFET technology to maintain performance without sacrificing power efficiency.

Detailed Explanation

The move from CMOS to FinFET is driven by the need to optimize power efficiency. FinFETs provide advantages in controlling leakage currents and improving performance at smaller dimensions, which benefits integrated circuit design. This transition is crucial as technology nodes shrink below 22nm, where traditional CMOS technologies start to falter.

Examples & Analogies

This transition can be likened to upgrading from traditional light bulbs to LED bulbs. While traditional bulbs (CMOS) may have been efficient at one point, LEDs (FinFETs) provide far better energy savings and longevity, showing how innovation can lead to significant gains in efficiency.

Key Concepts

-

Power Consumption: The total energy used by integrated circuits, critical for battery-operated devices.

-

Dynamic Power: Power consumed during switching events in CMOS circuits.

-

Static Power: Power loss due to leakage currents in off-state transistors.

-

FinFET Technology: An advanced transistor structure designed to minimize leakage and enhance performance.

Examples & Applications

CMOS Inverter Power Profile: Vdd = 1.0V, CL = 10fF, f = 100MHz results in dynamic power (P_dyn) of approximately 1.0µW.

FinFET Inverter Power Profile: Vdd = 0.8V, CL = 8fF, f = 100MHz results in dynamic power (P_dyn) of approximately 0.51µW.

Memory Aids

Interactive tools to help you remember key concepts

Rhymes

In circuits where power we seek, / Low energy's what we will speak. / Scaling voltage, clocking with grace, / FinFET leads in the race!

Stories

Once upon a time, there were two friends, CMOS and FinFET. CMOS was reliable but struggled with leakage as he grew older and smaller. FinFET came with new capabilities and helped minimize leakage like a wise old wizard, making him favored for future designs in their town!

Memory Tools

To remember the power types: D.S.S. - Dynamic, Static, Short-circuit.

Acronyms

To recall low-power techniques

*V.C.M.P.* - Voltage Scaling

Clock Gating

Multi-Vt Cells

Power Gating.

Flash Cards

Glossary

- CMOS

Complementary Metal-Oxide-Semiconductor, a technology for constructing integrated circuits.

- FinFET

Fin Field-Effect Transistor, a type of non-planar transistor used in advanced technology nodes for better control of leakage current.

- Dynamic Power

Power consumed due to switching activity in a circuit, expressed as P_dyn = αCLVdd²f.

- Static Power

Power consumed by leakage currents in inactive transistors.

- Voltage Scaling

A technique used to reduce power consumption by lowering the supply voltage.

- Clock Gating

A technique that disables the clock to inactive circuit segments to save power.

- Dynamic Voltage and Frequency Scaling (DVFS)

A method that adjusts the voltage and frequency of a processor based on workload demands.

Reference links

Supplementary resources to enhance your learning experience.