Step 2: Low Power Techniques in CMOS Design

Enroll to start learning

You’ve not yet enrolled in this course. Please enroll for free to listen to audio lessons, classroom podcasts and take practice test.

Interactive Audio Lesson

Listen to a student-teacher conversation explaining the topic in a relatable way.

Voltage Scaling

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Let's start with voltage scaling. What do you think happens to power consumption when we reduce the supply voltage?

I think it would decrease power, right?

Exactly! Power is proportional to V_dd squared. So, if we reduce V_dd, we can significantly lower both dynamic and static power. Can anyone give me the formula for dynamic power?

It's P_dyn = αCLV_dd^2f, right?

Spot on, Student_2! The key takeaway is that voltage scaling is a powerful strategy to manage power in CMOS designs.

Clock Gating

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Next, let’s discuss clock gating. Why do you think it's important?

It seems like a way to save power by not letting inactive components use energy.

Exactly, Student_3! When parts of the circuit aren't needed, turning off the clock prevents unnecessary power usage. What would happen if we didn’t use clock gating?

Then we'd waste energy on components that aren't doing anything.

Right! It's crucial to implement clock gating effectively to optimize energy consumption.

Multi-Vt Cells

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Let’s explore multi-Vt cells. Who can explain the benefit of using both high and low threshold voltage transistors?

It seems they would balance not just speed but also leakage power.

Absolutely! High-threshold cells reduce leakage, while low-threshold cells provide faster switching. This combination optimizes performance without excessive power dissipation. How would you choose which type to use?

I guess it depends on the application's performance requirements?

Exactly! Timing and power budget need to guide your selection.

Power Gating

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Now, let’s talk about power gating. Who can tell me what it means to use sleep transistors?

It's like shutting off the power to parts of the circuit that aren't active!

Exactly right! This way, we minimize static power by cutting off the current entirely. What do you think happens at the design stage when we decide where to place these sleep transistors?

It takes careful planning to decide what's inactive and when to turn off those parts.

Yes! Effective power gating design is essential for performance optimization.

Dynamic Voltage and Frequency Scaling (DVFS)

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Lastly, let’s cover DVFS. Why is it necessary to adjust voltage and frequency?

That way you can respond to workload needs without wasting power.

Correct! DVFS allows systems to optimize performance dynamically. What are the potential challenges you see with DVFS?

Maybe the complexity in adapting to changes quickly?

Exactly! Timing when to scale down or up can be tricky, but it's crucial for power savings while still ensuring adequate performance.

Introduction & Overview

Read summaries of the section's main ideas at different levels of detail.

Quick Overview

Standard

In this section, we explore five primary techniques for reducing power usage in CMOS designs: voltage scaling, clock gating, multi-Vt cells, power gating, and dynamic voltage and frequency scaling (DVFS). Each method plays a crucial role in balancing power efficiency with performance.

Detailed

Step 2: Low Power Techniques in CMOS Design

In the transition towards more energy-efficient electronic components, designers of integrated circuits (ICs) utilize various low power techniques within CMOS design. This section focuses on five primary strategies:

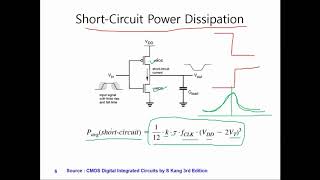

- Voltage Scaling: Reducing the supply voltage (V_dd) helps to decrease both dynamic and leakage power significantly. Since power consumption is proportional to the square of the voltage, a decrease in V_dd can lead to substantial savings in power.

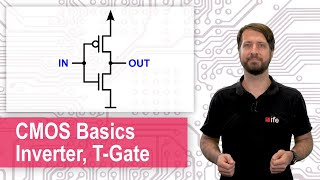

- Clock Gating: This technique involves disabling the clock signal for inactive modules. By doing so, energy is conserved during periods when certain components do not require active power, effectively lowering the dynamic power dissipation.

- Multi-Vt Cells: This strategy leverages a mixture of transistors with different threshold voltages (V_t) to strike a balance between speed and leakage. High-threshold transistors can be used where performance speed is less critical, while low-threshold transistors can be utilized where speed is paramount.

- Power Gating: Through the use of sleep transistors, this method disconnects the power supply to blocks that are not in use, which drastically reduces static power consumption.

- Dynamic Voltage and Frequency Scaling (DVFS): By modifying the voltage and frequency to match workload demands, DVFS provides an adaptive approach to manage performance levels while minimizing energy consumption.

These techniques are critical as they address the challenge of maintaining performance in increasingly complex designs while adhering to the imperative of low power usage.

Youtube Videos

Audio Book

Dive deep into the subject with an immersive audiobook experience.

Voltage Scaling

Chapter 1 of 5

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

● Voltage Scaling: Reducing VddV_{dd} decreases dynamic and leakage power.

Detailed Explanation

Voltage scaling involves lowering the supply voltage (Vdd) in circuit design. This technique is critical because both dynamic power and leakage power are directly related to the voltage applied. The formula for dynamic power is P_dyn = αCLVdd²f, which shows that power consumption increases with the square of the supply voltage. Thus, by reducing the Vdd, we can significantly decrease power consumption, making the circuit more power-efficient.

Examples & Analogies

Think of it like reducing pressure in a water pipe. When you lower the pressure (analogous to lowering voltage), less water (power) flows through, making the system more efficient without reducing performance.

Clock Gating

Chapter 2 of 5

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

● Clock Gating: Disables the clock signal in inactive modules.

Detailed Explanation

Clock gating is a power-saving technique where the clock signal is turned off for certain sections of the circuit that are not currently in use. Since many parts of the integrated circuit do not need to be operated continuously, disabling their clock signal reduces dynamic power consumption during idle times. This method is particularly effective in digital circuits, where clock activity can be significant.

Examples & Analogies

Imagine a light switch; turning off a light when you leave the room saves electricity. Similarly, clock gating prevents unnecessary power usage in digital circuits by 'turning off' parts that aren't needed.

Multi-Vt Cells

Chapter 3 of 5

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

● Multi-Vt Cells: Using a mix of high and low threshold voltage transistors to balance speed and leakage.

Detailed Explanation

The technique of using multi-Vt (threshold voltage) cells involves incorporating transistors with different threshold voltage levels in the circuit. High-Vt transistors are slower but leak less current, while low-Vt transistors are faster but have higher leakage. By strategically mixing these transistors, designers can optimize the performance of the circuit: ensuring that critical paths have low delay while minimizing overall leakage power.

Examples & Analogies

It's like choosing different types of coffee beans for different brews—using a robust blend for a strong cup (low leakage) and a smoother blend for a quick pick-me-up (high speed) to get the best combination of flavor and strength.

Power Gating

Chapter 4 of 5

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

● Power Gating: Disconnects power supply to unused blocks using sleep transistors.

Detailed Explanation

Power gating employs sleep transistors to disconnect power from unused blocks within an integrated circuit. This is beneficial in reducing leakage power since devices in sleep mode consume negligible power. By implementing power gating, designers can significantly enhance the efficiency of battery-powered devices by reducing the current draw when certain functions are not needed.

Examples & Analogies

Picture a car with a hybrid engine—when stationary, the engine turns off to save fuel (like reducing power to unused blocks), and it only runs when necessary. This preserves energy and improves efficiency.

Dynamic Voltage and Frequency Scaling (DVFS)

Chapter 5 of 5

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

● Dynamic Voltage and Frequency Scaling (DVFS): Adjusts performance levels based on workload.

Detailed Explanation

Dynamic Voltage and Frequency Scaling (DVFS) is a method that allows a system to dynamically change its voltage and frequency according to current computing demands. When the system needs to perform intensive tasks, it increases voltage and frequency for maximum performance, and when idle or performing lighter tasks, it reduces both to save power. This adaptability helps balance performance with power consumption throughout the operational profile.

Examples & Analogies

Consider a car that can shift gears and adjust its speed automatically. When going uphill (high workload), it uses more engine power (higher voltage and frequency), and when cruising on a flat road (low workload), it saves fuel by shifting to a lower gear (lower voltage and frequency). This optimizes performance while conserving energy.

Key Concepts

-

Voltage Scaling: Reducing voltage to lower power consumption.

-

Clock Gating: Prevents power draw by disabling clock in inactive modules.

-

Multi-Vt Cells: Incorporating various threshold voltages for balance.

-

Power Gating: Disconnecting power to inactive blocks saves energy.

-

Dynamic Voltage and Frequency Scaling (DVFS): Modulates performance based on workload.

Examples & Applications

Applying voltage scaling from 1.0V to 0.8V in a circuit reduces power by 36%.

Using clock gating in a processor can lead to power savings of 30% when not all cores are active.

Memory Aids

Interactive tools to help you remember key concepts

Rhymes

When it's time to save some power, lower voltages are the flower.

Stories

Imagine a city where streetlights turn on only when cars are nearby. This is like clock gating, where energy is saved by keeping parts of circuits inactive until needed.

Memory Tools

Remember the acronym 'VMPCD': Voltage Scaling, Multi-Vt Cells, Power Gating, Clock Gating, DVFS.

Acronyms

Use 'VMEGA' to remember techniques

Voltage scaling

Multi-Vt

Energy management through clock gating

Gating power

and Adjusting frequency.

Flash Cards

Glossary

- Voltage Scaling

A technique to lower the supply voltage, thereby reducing power consumption in circuits.

- Clock Gating

A method to disable the clock signal for inactive parts of a circuit to conserve power.

- MultiVt Cells

A design approach that uses transistors with different threshold voltages to optimize speed and leakage.

- Power Gating

The technique of using sleep transistors to disconnect power from unused circuit blocks to reduce static power.

- Dynamic Voltage and Frequency Scaling (DVFS)

A power management technique that adjusts voltage and frequency according to workload requirements.

Reference links

Supplementary resources to enhance your learning experience.