Step 6: Analysis and Results

Enroll to start learning

You’ve not yet enrolled in this course. Please enroll for free to listen to audio lessons, classroom podcasts and take practice test.

Interactive Audio Lesson

Listen to a student-teacher conversation explaining the topic in a relatable way.

CMOS Limitations

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Let’s start by discussing the limitations of CMOS. What do you all think happens when we try to utilize CMOS at smaller nodes?

I think it gets more power hungry because of leakage currents.

Exactly! CMOS faces higher leakage currents at lower nodes. This inefficiency becomes a critical issue for ultra-low-power devices. Can anyone tell me why leakage is particularly problematic?

Because it wastes battery power even when the device is not actively running.

Great insight! So, we have dynamic and static power dissipation affecting battery life in CMOS. Any thoughts on how FinFETs can help?

FinFETs might have better control over leakage, right?

Yes! That’s a crucial point. FinFETs offer stronger channel control which significantly reduces leakage.

In summary, while CMOS has its limitations at smaller nodes, particularly concerning leakage, FinFETs can overcome these issues...

Benefits of FinFETs

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Now let’s look at the benefits of using FinFET technology. Can anyone list a few advantages?

I know that FinFETs reduce leakage and can support higher density designs.

Good! Higher density is critical in enhancing performance without needing larger chips. What else?

Perhaps they might scale better as technology continues to advance?

Exactly! Scalability ensures that as we approach smaller nodes, FinFETs maintain efficiency. Remember, though, there are trade-offs. Any ideas on what those might be?

They might be harder and more expensive to manufacture.

Correct! Higher manufacturing costs and complexity are significant considerations for adopting FinFET technology.

In conclusion, although FinFETs present manufacturing challenges, their benefits in performance and battery life make them a favorable choice.

Design Trade-offs

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Let's delve into the design trade-offs associated with FinFETs. Why are these trade-offs important to designers?

Understanding trade-offs helps in selecting the right technology for specific applications.

Exactly! For instance, while FinFETs reduce leakage and enhance performance, they come with increased manufacturing complexity. Can you think of an application where this might matter?

Maybe in mobile devices where battery life is critical?

Yes! Battery life is paramount in mobile devices, which is why FinFETs, despite their cost, are often preferred. Let’s summarize here: understanding design trade-offs allows designers to optimize for their specific needs.

Introduction & Overview

Read summaries of the section's main ideas at different levels of detail.

Quick Overview

Standard

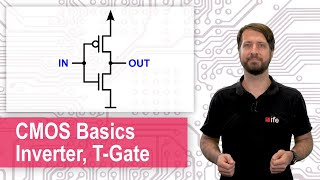

In this section, we analyze the constraints presented by traditional CMOS technology, particularly regarding leakage at smaller nodes. We also highlight the advantages of adopting FinFET technology, including improved performance characteristics and scalability for low-power applications.

Detailed

In this section, we conduct an in-depth analysis of the limitations of CMOS technology and the advantages offered by FinFETs in low-power circuit design. CMOS circuits exhibit significant leakage currents, particularly at technology nodes under 45nm, making them inefficient for ultra-low-power applications. In contrast, FinFETs feature enhanced channel control, which leads to reduced leakage and increased drive strength, making them suitable for high-density and scalable designs. Although FinFETs present manufacturing challenges and higher costs, they enable better performance per watt and promote longer battery life, essential aspects for modern low-power devices.

Youtube Videos

Audio Book

Dive deep into the subject with an immersive audiobook experience.

CMOS Limitations

Chapter 1 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

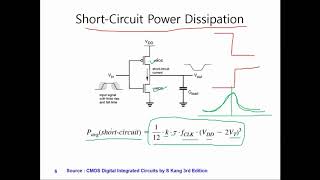

● CMOS Limitations: Higher leakage at lower nodes, inefficient for ultra-low-power devices.

Detailed Explanation

This chunk highlights the limitations associated with CMOS technology, particularly as technology scales down to smaller node sizes. With advances in fabrication, as transistors become smaller, they tend to have higher leakage currents, which leads to unnecessary power consumption. This is detrimental for ultra-low-power applications where keeping power usage to a minimum is crucial. Therefore, traditional CMOS technology may struggle to meet the demands of power-sensitive designs in modern electronics.

Examples & Analogies

Consider a leaking faucet in your home. If the faucet drips constantly, it may result in wasting a significant amount of water over time, similar to how CMOS circuits waste power due to leakage. Just as fixing the faucet can conserve water, using newer technologies can help conserve energy in electronics.

FinFET Benefits

Chapter 2 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

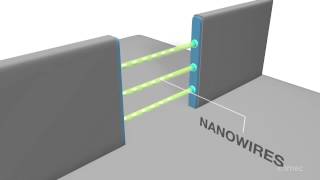

● FinFET Benefits: Strong channel control, reduced leakage, higher density, and scalability.

Detailed Explanation

This chunk discusses the advantages of FinFET technology over traditional CMOS. FinFETs provide better control of the channel through their three-dimensional structure, which allows for more efficient operation at smaller scales. Consequently, they exhibit significantly lower leakage currents compared to conventional transistors. Additionally, FinFETs can pack more transistors on a chip, which enhances density and scalability, making them well-suited for modern computing needs.

Examples & Analogies

Think of building a more efficient parking garage that uses vertical space (like FinFETs) instead of sprawling horizontally (like CMOS). By utilizing vertical space, you can fit more cars in a smaller footprint, just as FinFETs can fit more transistors in the same area compared to traditional designs.

Design Trade-offs

Chapter 3 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

● Design Trade-offs: FinFETs are harder to manufacture and costlier but offer longer battery life and better performance-per-watt.

Detailed Explanation

In this chunk, the focus is on the trade-offs involved while transitioning from CMOS to FinFET technology. While FinFETs offer significant performance benefits such as longer battery life and superior energy efficiency, they also come with challenges. Manufacturing FinFETs is more complex and expensive than traditional CMOS manufacturing, which can affect the overall cost of the devices. Designers must evaluate these trade-offs when deciding which technology to use for specific applications.

Examples & Analogies

Consider buying an energy-efficient appliance for your home. It might cost more upfront (similar to FinFETs), but it saves you money on energy bills in the long run (just like how FinFETs save power). Before making the purchase, you weigh the initial cost against long-term savings, just as engineers weigh performance against manufacturing complexity.

Key Concepts

-

CMOS Limitations: Higher leakage currents and power dissipation issues.

-

FinFET Benefits: Improved channel control and reduced leakage.

-

Design Trade-offs: Challenges in manufacturing and cost versus performance advantages.

Examples & Applications

For a 22nm FinFET circuit, the dynamic power consumption is significantly lower compared to a traditional CMOS circuit, helping maintain battery life in mobile devices.

A comparison of manufacturing processes illustrates that although FinFETs are complex to produce, they lead to lower overall power usage in high-performance applications.

Memory Aids

Interactive tools to help you remember key concepts

Rhymes

CMOS leaks, FinFET peaks; power savings make it sleek.

Stories

Once in the land of circuits, CMOS grew weary and old, always leaking power, becoming too bold. FinFET came to save the day, with a structure that kept leakage at bay.

Memory Tools

Remember 'COPE' for FinFET: Control, Overcome leakage, Perform better, Efficient.

Acronyms

FLIP

FinFET Leads to Improved Power efficiency.

Flash Cards

Glossary

- CMOS

Complementary Metal-Oxide-Semiconductor, a technology for constructing integrated circuits.

- FinFET

Fin Field-Effect Transistor, a type of non-planar transistor used in semiconductor devices.

- Leakage

Unwanted power consumed by a transistor when it is in the off state.

- Power Dissipation

Release of electrical energy as heat, particularly in electronic components.

- Scalability

The ability of a technology to be adapted to different sizes or scales.

Reference links

Supplementary resources to enhance your learning experience.