Clock Management Resources

Interactive Audio Lesson

Listen to a student-teacher conversation explaining the topic in a relatable way.

Importance of Clock Management

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Good morning, class! Today we’re going to talk about clock management resources in FPGAs. Can anyone explain why clock management is vital in digital designs?

It's important to have all parts of a system synchronized!

Exactly! Synchronization ensures that different components operate at the right moments. Can someone name a specific component used for clock management?

I think it's Phase-Locked Loops, or PLLs?

Right again! PLLs help align the frequency and phase of multiple clock signals. They play a crucial role in adapting signal timing across your design.

Understanding Phase-Locked Loops (PLLs)

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Let’s delve deeper into how PLLs work. Who can share something they know about PLLs?

PLLs can help generate different clock frequencies, right?

Yes! That's a great observation. They take an input clock and produce an output clock that can be adjusted in frequency, allowing for better performance across different operational requirements.

Are PLLs used in all FPGAs?

Most FPGAs have them, but the specific implementation can vary based on the design. Remember: PLLs are critical for maintaining signal integrity and reducing jitter in clock signals.

Role of Clock Dividers

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Now, let’s move on to clock dividers. Why do you think we need clock dividers in our designs?

To lower the frequency of a clock signal?

Correct! Clock dividers reduce the frequency, allowing us to use different rates for various components. This can help to save power and fit logic timing requirements.

Is it true that clock dividers can also create multiple clock domains?

Exactly! By using clock dividers, you can manage multiple clock domains effectively with different operational frequencies, crucial in designs needing scalability.

Synchronized Operation

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

To wrap up, why is synchronized operation so critical in FPGAs and digital design as a whole?

If components aren't synchronized, they can cause glitches and errors!

Spot on! Timing issues can lead to significant problems, affecting overall device reliability. So effective clock management with PLLs and clock dividers is essential.

How does this relate to performance?

Great question! When clock management is optimized, it enhances performance and efficiency, making your design robust. Synchronization is the heart of successful digital circuit operation!

Introduction & Overview

Read summaries of the section's main ideas at different levels of detail.

Quick Overview

Standard

This section discusses the significance of clock management resources within FPGAs, focusing on the use of Phase-Locked Loops (PLLs) and clock dividers to manage multiple clock domains and generate different clock frequencies, ensuring synchronized operations across the device.

Detailed

Clock Management Resources in FPGAs

Clock management is pivotal within Field-Programmable Gate Arrays (FPGAs) to maintain synchronous operations across various components of a digital design. Within this context, FPGAs incorporate two principal features to handle clock signals: Phase-Locked Loops (PLLs) and clock dividers.

Key Components of Clock Management

- Phase-Locked Loops (PLLs): These circuits are instrumental in synchronizing the phase and frequency of multiple clock signals. They allow designers to generate a stable clock signal from an external reference clock, which can be adjusted for frequency scaling and stability.

- Clock Dividers: These components are employed to reduce the frequency of the incoming clock signal. By dividing the frequency by a certain factor, clock dividers can manage various clock rates across different functional domains, essential for reducing power usage or adapting to specific timing requirements in digital designs.

Significance in Design

Efficient clock management is essential for ensuring that all parts of the FPGA operate harmoniously. By utilizing PLLs and clock dividers, designers can effectively handle multiple clock domains and enhance the overall performance of complex digital systems. Additionally, proper clock management resources help prevent timing issues that may lead to design failures or unanticipated behavior in deployed systems.

Youtube Videos

Audio Book

Dive deep into the subject with an immersive audiobook experience.

Importance of Clock Management

Chapter 1 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Clock management in FPGAs is critical for ensuring synchronized operation across the entire design.

Detailed Explanation

In FPGA designs, clock management is essential because all components of the system rely on a consistent timing signal, known as the clock. The clock synchronizes the operation of different parts of the design, ensuring that tasks and data transfers occur in harmony. If the clock signals are not managed properly, different components may operate out of sync, leading to incorrect behavior and potential errors in the digital system.

Examples & Analogies

Think of clock management like a conductor leading an orchestra. Just as the conductor guides musicians to play their parts at the right times so that the music flows harmoniously, clock management ensures that all components of the FPGA work together seamlessly, producing the correct output.

Phase-Locked Loops (PLLs)

Chapter 2 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

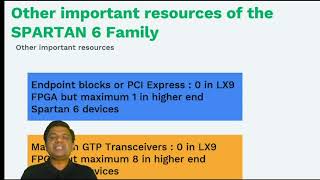

FPGAs contain Phase-Locked Loops (PLLs) and clock dividers to handle multiple clock domains and to generate different clock signals at various frequencies.

Detailed Explanation

Phase-Locked Loops (PLLs) within FPGAs are crucial for creating different clock frequencies needed for various components of a digital system. A PLL can take a single clock signal and generate multiple output signals that might run at different frequencies. This feature is particularly important for complex designs where different parts of the system need to operate at unique speeds. Clock dividers also help in managing the frequency of the clock signals, making sure that all components get the clock pulses they need, in the correct timing format.

Examples & Analogies

Imagine a bakery where the head chef (the PLL) is able to prepare multiple dishes (different frequencies) simultaneously, each needing to bake for different lengths of time. The chef divides their attention (clock division) to ensure that each dish comes out perfectly timed and in sync with each other.

Handling Multiple Clock Domains

Chapter 3 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

FPGAs use clock management resources to handle multiple clock domains effectively within a single design.

Detailed Explanation

In FPGA designs, it is common to have multiple clock domains, meaning different portions of the design may be driven by different clock signals, each with its own frequency. Managing these clock domains is essential to prevent data corruption and timing issues. The clock management resources in FPGAs, such as PLLs and clock dividers, allow designers to switch between or synchronize these different clock domains, ensuring that data can be communicated accurately between them.

Examples & Analogies

Think about cars in a multi-lane highway (different clock domains), where each lane may have a different speed limit (frequency). Without proper traffic management (clock management), cars could collide at lanes merging or transitioning, but with the right signals and timing, they can smoothly transition between lanes without accidents.

Key Concepts

-

Clock Management: The process of synchronizing and managing clock signals within FPGAs.

-

Phase-Locked Loops (PLLs): Essential circuits used to control clock frequencies and phases for reliable digital design.

-

Clock Dividers: Components that help in reducing clock frequencies, allowing for versatile signal adjustments in designs.

-

Clock Domains: Portions of a circuit that operate with specific clock signals, necessary for complex system designs.

Examples & Applications

Using a PLL to take a 50 MHz input clock and convert it to a 200 MHz output clock for a digital circuit.

Applying a clock divider to reduce a 100 MHz clock signal into 25 MHz for use in a lower-speed module.

Memory Aids

Interactive tools to help you remember key concepts

Rhymes

To keep the clock in line, PLLs help design, Dividers make signals fine, working together all the time.

Stories

Imagine a conductor leading an orchestra. Each musician has to play their notes at the right time, just like PLLs and clock dividers ensure signals are synchronized. Without the conductor, the performance would be chaotic!

Memory Tools

Remember 'PDC' for PLL, Divider, and Clock - the three keys to managing your clock signals effectively.

Acronyms

Use 'PLC' (Phase, Lock, Clock) to remember that PLLs help lock the phase of clock signals!

Flash Cards

Glossary

- Clock Management

The methods and resources employed in FPGA designs to synchronize and manage clock signals across various components.

- PhaseLocked Loop (PLL)

A control system that generates a signal with a fixed relation to the phase of a reference signal, commonly used for frequency synthesis and synchronization.

- Clock Divider

A circuit that divides the frequency of an incoming clock signal, allowing for different operational clock rates.

- Clock Domain

A section of a digital circuit where a particular clock signal is used; different clock domains can have different frequencies.

Reference links

Supplementary resources to enhance your learning experience.