Implementation (Place and Route)

Interactive Audio Lesson

Listen to a student-teacher conversation explaining the topic in a relatable way.

Understanding Place and Route

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Today, we're exploring the place and route phase in FPGA implementation. Can anyone tell me why this stage is critical?

I think it's because that's where the design gets physically organized on the FPGA?

Exactly! The place and route process determines how we fit our logic blocks onto the FPGA. We need to optimize for both placement and routing. Any thoughts on what that might involve?

Maybe making sure everything is connected properly and efficiently?

Yes, optimizing connections is crucial. Remember, we want to minimize power and increase speed. This is where logic blocks are placed effectively and routed intelligently.

What tools do we use for this?

Great question! Tools like Xilinx Vivado or Intel Quartus help automate much of this process. Let's summarize what we've learned: place and route involves organizing logic blocks and optimizing routing to meet performance goals.

Optimization Objectives

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Now, let’s dive deeper into the optimization goals during place and route. Who can list some optimization objectives?

I remember something about speed and power?

Yes! We optimize for speed to meet timing requirements and for power to ensure it runs efficiently. What else could be important?

Maybe area? Like using the least physical space?

Exactly! Minimizing the physical area is critical, as it can reduce costs and improve performance. Remember the acronym 'SPA': Speed, Power, Area. Can everyone repeat that?

SPA!

Fantastic! Let’s summarize: during implementation, we focus on optimizing speed, area, and power.

Role of Implementation Tools

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Next, let’s look at the tools we mentioned earlier. What is their role in the place and route phase?

Do they help with technical configurations?

Spot on! Tools automate placement and routing, analyze performance, and help fix timing issues. Can anyone name a popular FPGA tool?

Xilinx Vivado, I think!

Yes, great job! These tools streamline our work and reduce errors. In summary, the role of tools is to enhance efficiency and effectiveness in the place and route process.

Introduction & Overview

Read summaries of the section's main ideas at different levels of detail.

Quick Overview

Standard

Implementation is a critical stage in FPGA design where the synthesized netlist is translated into physical arrangements within the FPGA. This process includes placing logic blocks efficiently and routing their connections, while also optimizing for speed, area, and power consumption. Tools assist in automating this process, ensuring that the design meets the necessary requirements.

Detailed

Implementation (Place and Route)

The implementation, often referred to as place and route, is a pivotal phase in the FPGA design flow, which follows synthesis. In this stage, the previously synthesized netlist is mapped onto the FPGA's physical resources, which include programmable logic blocks and interconnects. The goal of implementation is to determine both the positioning of logic elements and the routing of connections between them, ensuring that the design fulfills performance metrics such as timing, area, and power efficiency.

- Mapping Logic Blocks: During the placing phase, the logic blocks, including lookup tables (LUTs) and flip-flops, are allocated specific locations on the FPGA fabric based on the design's requirements. Optimization algorithms are employed to enhance performance and resource utilization.

- Routing Connections: Following placement, the routing phase connects these logic blocks according to the netlist. This involves using the programmable interconnects within the FPGA, which are designed to facilitate intricate routing of signals.

- Optimization Goals: The implementation tools aim to minimize power consumption and the physical area used while satisfying speed requirements crucial for the functionality of the circuit.

- Utilization of Tools: Modern FPGA design software provides automated solutions to streamline the place and route process. These tools not only facilitate accurate mapping and routing but also evaluate potential timing issues and resource conflicts early in the design phase. This allows for corrective actions before finalizing the programming of the FPGA.

Implementation is thus a complex but essential step that transforms a design from theoretical models into practical hardware configurations, enabling the desired functionality in various applications.

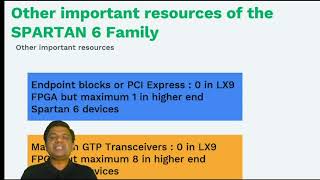

Youtube Videos

Audio Book

Dive deep into the subject with an immersive audiobook experience.

Implementation Process Overview

Chapter 1 of 2

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

The synthesized design is mapped onto the FPGA’s programmable resources. The implementation process involves placing logic blocks on the FPGA and routing the connections between them. The tools will optimize the design for area, speed, and power.

Detailed Explanation

In this step, after you have synthesized your design (which means converting your high-level description into something the FPGA can understand), the next task is to arrange the elements of your design onto the FPGA itself. This is called 'mapping.' During mapping, specific areas of the FPGA are allocated for different logic blocks according to the design specifications. Then, 'routing' comes into play, which connects these blocks together. This is a crucial stage because the arrangement can significantly impact how fast and efficiently your circuit works. The tools you use will automatically optimize your design so that it takes up less space, works faster, and uses less power.

Examples & Analogies

Imagine building a city (the FPGA) where you need to determine where to place schools, hospitals, and homes (the logic blocks). If you put all the houses too far from the schools, children will take longer to get there. Similarly, in place and route, you must think critically about where each logic block goes to ensure quick connections (like roads) between them.

Optimization Techniques

Chapter 2 of 2

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

The tools will optimize the design for area, speed, and power.

Detailed Explanation

Optimization in the context of FPGA implementation means fine-tuning your design so it operates effectively under different conditions. 'Area' refers to how much space the design takes on the FPGA, 'speed' relates to how fast the logic can execute, and 'power' indicates how much energy is consumed. FPGA design tools will use various algorithms to ensure that your design meets the required performance while utilizing the least amount of resources. This could involve rearranging logic blocks, minimizing the connections required, or even simplifying the logic used in some instances.

Examples & Analogies

Think of it like packing for a trip. You want to fit everything into one suitcase (the FPGA), but you don’t want it to be too heavy (power), and you want to be able to carry it quickly (speed). So, you carefully choose what to pack and how to arrange it (optimization), ensuring there’s enough space to grab things without taking a lot of time to find items (area efficiency).

Key Concepts

-

Place and Route: A critical phase in FPGA design that involves the physical arrangement of design elements.

-

Optimization Goals: Key objectives in implementation that include maximizing speed, minimizing area, and reducing power consumption.

-

Implementation Tools: Software tools that assist in automating the place and route process.

Examples & Applications

An FPGA design may require the placement of several logic blocks to perform a complex calculation. The place and route tool analyzes the connections to optimize signal paths.

Consider a digital signal processing application on an FPGA. The implementation should prioritize speed and power efficiency to meet real-time processing requirements.

Memory Aids

Interactive tools to help you remember key concepts

Rhymes

When placing blocks, don’t forget, speed and power are your best bet.

Stories

Imagine building a city (the FPGA) where you want to place houses (logic blocks) as close as possible to minimize travel time (routing) while keeping the energy costs low (power).

Memory Tools

Remember 'SPA' for optimization objectives: Speed, Power, and Area.

Acronyms

SPA - Speed, Power, Area.

Flash Cards

Glossary

- Place and Route

The process of arranging logic blocks within an FPGA and setting up their interconnections to optimize performance.

- Synthesis

The phase where HDL code is transformed into a gate-level netlist before implementation.

- Optimization

The practice of making a design more efficient, focusing on parameters like speed, area, and power.

Reference links

Supplementary resources to enhance your learning experience.