Emerging Trends in IC Packaging Technologies

Interactive Audio Lesson

Listen to a student-teacher conversation explaining the topic in a relatable way.

Introduction to IC Packaging Technologies

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Good morning, class! Today we’re diving into emerging trends in IC packaging technologies. Have you all heard about the demand for smaller and faster semiconductor devices?

Yes, but why is that so important?

Great question! As devices integrate more functions while becoming smaller, IC packaging must evolve to maintain high performance. For instance, new technologies like 3D IC packaging and FOWLP are critical. Who can tell me about 3D IC packaging?

Is it when multiple chips are stacked together?

Exactly right! This stacking allows for more compact design and improved performance through reduced interconnect lengths. Let's remember it with the acronym 'STACK'—'S' for 'space-saving', 'T' for 'thermal management', 'A' for 'applications', 'C' for 'connections', and 'K' for 'keeping it compact'.

What kind of applications use this technology?

Great follow-up, Student_3! Applications include mobile devices, data centers, and HPC systems. Does anyone know what TSVs are in 3D ICs?

I think they are vertical connections that help link chips?

Perfect! TSVs make shorter connections between ICs, enhancing speed and efficiency. Remember that TSVs are key in both thermal management and performance. Let’s summarize: stacking ICs allows for more functionality in less space—let’s call that the '3D Advantage'.

Understanding Fan-Out Wafer-Level Packaging (FOWLP)

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Now that we’ve discussed 3D IC packaging, let’s shift gears to Fan-Out Wafer-Level Packaging or FOWLP. Can anyone explain what this technology does?

Isn’t it about spreading connections out?

Yes! FOWLP spreads electrical connections over a larger area, which leads to smaller and thinner packages while preserving interconnect density. Don't forget to use the mnemonic 'FOWLP'—'F' for 'Fan-out', 'O' for 'Optimized thickness', 'W' for 'Wafer-level', 'L' for 'Large connections', and 'P' for 'Performance enhancement'.

What benefits does FOWLP provide?

FOWLP enhances performance and thermal conductivity while also reducing manufacturing costs. It’s widely used in IoT devices and mobile technology. How do you think this can help with product development?

It might speed up production because it can be automated!

Exactly! Automation reduces production costs and supports large-volume output. To summarize, FOWLP revolutionizes how we think about IC packaging—leading to lighter and more efficient devices.

Introduction & Overview

Read summaries of the section's main ideas at different levels of detail.

Quick Overview

Standard

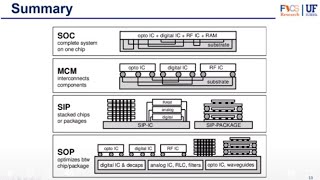

As semiconductor devices require higher performance and efficiency with reduced sizes, advanced IC packaging technologies such as 3D IC Packaging and Fan-Out Wafer-Level Packaging (FOWLP) are evolving. This section outlines the benefits, applications, and significant features of these technologies that meet the evolving demands of the industry.

Detailed

Detailed Summary

This section discusses key emerging trends in integrated circuit (IC) packaging technologies, focusing on the need for solutions that improve thermal management, signal integrity, and power delivery while optimizing interconnect density and minimizing package sizes.

3D IC Packaging

3D IC Packaging is a method wherein multiple ICs are stacked vertically to form a three-dimensional package. This approach utilizes Through-Silicon Vias (TSVs) to facilitate electrical connections between the components, enhancing integration while reducing the physical footprint. Key benefits include improved thermal management and performance, particularly in high-speed applications such as graphics processing units, high-performance computing, and memory devices.

Applications:

- Heterogeneous Integration: Combining different chip types such as processors and sensors.

- Common Uses: Mobile devices, data centers, IoT devices, and wearables.

Fan-Out Wafer-Level Packaging (FOWLP)

FOWLP employs a reconstituted wafer configuration that allows the IC connections to be distributed over a larger area, resulting in a thinner package maintaining high interconnect density. The advantages of FOWLP include enhanced performance, thermal conductivity, and reduced manufacturing costs.

Applications:

FOWLP is prevalent in mobile devices, IoT technologies, RF components, and high-performance memory applications.

Youtube Videos

Audio Book

Dive deep into the subject with an immersive audiobook experience.

Introduction to Package Technologies

Chapter 1 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Several new packaging techniques are being developed to address the challenges posed by increasingly complex and powerful ICs. These technologies aim to improve thermal management, signal integrity, power delivery, and interconnect density while reducing overall package size.

Detailed Explanation

The introduction discusses the need for new packaging techniques in the semiconductor industry. As integrated circuits (ICs) become more complex and powerful, traditional packaging methods may not be sufficient. These new techniques focus on enhancing key attributes such as thermal management (how heat is dissipated), signal integrity (how well signals maintain their quality), power delivery (how power is supplied effectively), and interconnect density (how many connections can be made in a given space) while simultaneously making the total package smaller.

Examples & Analogies

Imagine you have a larger, more intricate model of a castle that you want to fit into a smaller display case. You have to come up with innovative ways to lay out the pieces so that everything fits well together while ensuring it still looks impressive and functions correctly. Similarly, engineers must find advanced ways to package ICs to enhance performance without taking up too much space.

3D IC Packaging

Chapter 2 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

3D IC packaging involves stacking multiple ICs on top of each other to create a three-dimensional package. This technology allows for higher integration and smaller footprints, making it ideal for applications where space is limited.

● Through-Silicon Vias (TSVs): TSVs are vertical interconnects that pass through the silicon die, allowing for electrical connections between stacked ICs. This approach reduces the distance between components, improving signal speed and reducing power consumption.

● Benefits: 3D ICs provide better thermal management, higher performance, and reduced interconnect lengths, which are critical for high-speed applications like graphics processing units (GPUs), high-performance computing (HPC), and memory devices.

● Applications: Heterogeneous integration, where different types of chips (e.g., processors, memory, sensors) are stacked together, is a common use case. 3D ICs are used in mobile devices, data centers, IoT devices, and wearables.

Detailed Explanation

In 3D IC packaging, different chips are stacked vertically rather than laid out side by side. This stacking saves space and allows for more integration of different functions. Through-Silicon Vias (TSVs) are critical in this approach, as they provide a pathway for electrical connections between these stacked layers. By reducing how far signals must travel between components, TSVs enhance speed and cut power consumption. The benefits of this method include improved heat management, which is essential in high-speed applications, and a more compact design, suitable for devices where size is a constraint like smartphones and IoT gadgets.

Examples & Analogies

Think of 3D IC packaging like organizing books in a library. Instead of spreading them out on multiple shelves (2D), you stack them vertically. This way, you save space and can access the information you need much faster. Similarly, stacking ICs reduces the space needed while improving performance.

Fan-Out Wafer-Level Packaging (FOWLP)

Chapter 3 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Fan-out wafer-level packaging (FOWLP) is an advanced packaging technique where the IC is placed in a reconstituted wafer and the electrical connections are “fanned out” to a larger area. This provides a smaller, thinner package compared to traditional packaging methods while maintaining high interconnect density.

● Benefits: FOWLP allows for higher performance, better thermal conductivity, and higher integration density in a smaller space. The technique also reduces manufacturing costs due to its ability to support large volumes and automated assembly.

● Applications: FOWLP is widely used in mobile devices, IoT applications, RF components, and high-performance memory devices.

Detailed Explanation

FOWLP reconfigures how ICs are packaged by spreading connections outward from the chip, creating a larger area to connect with other components while keeping the overall package slim. This technique enhances performance by ensuring that the connection points are more efficient, which helps in reducing heat buildup (thermal conductivity) and allows more components to fit into a smaller area (integration density). It also benefits manufacturers by lowering costs and streamlining production due to its compatibility with automated machinery.

Examples & Analogies

Imagine a tree with branches spreading out wide and thin. Each branch (like electrical connections) can reach more leaves (other components) without needing to be a thick trunk (large case). This tree spreads widely but doesn’t take up much ground space. In electronics, FOWLP functions similarly by providing many connection points in a compact layout, making it useful for devices like smartphones.

Key Concepts

-

3D IC Packaging: Stacking multiple integrated circuits for compact design.

-

FOWLP: A technique for spreading electrical connections to enhance performance.

-

Thermal Management: Techniques to efficiently remove heat from ICs.

-

Heterogeneous Integration: Combining various chip types into one package.

-

TSVs: Vertical connections necessary for 3D packaging.

Examples & Applications

3D IC packaging is used in mobile devices like smartphones and tablets to improve processing power without increasing size.

FOWLP is utilized in IoT devices to enhance functionalities while keeping the devices lightweight and efficient.

Memory Aids

Interactive tools to help you remember key concepts

Rhymes

Stack it high, make it tight, 3D ICs take flight!

Stories

Imagine a small village where every house is stacked on top of each other, making the best use of limited space. Similarly, 3D IC packaging allows chips to stack up for efficiency.

Memory Tools

To remember FOWLP: 'Fan Out While Letting Performance rise'.

Acronyms

Use 'FOWLP'—'F' for Fan-Out, 'O' for Optimized, 'W' for Wafer-level, 'L' for Large connections, 'P' for Performance.

Flash Cards

Glossary

- 3D IC Packaging

A technique that involves stacking multiple integrated circuits to create a compact package.

- ThroughSilicon Vias (TSVs)

Vertical connections that facilitate electrical pathways between stacked silicon layers in 3D ICs.

- FanOut WaferLevel Packaging (FOWLP)

A method that distributes chip connections over a larger area, allowing for thinner packages with high interconnect density.

- Heterogeneous Integration

The combining of different types of chips into one package for enhanced functionality.

- Thermal Management

Methods and materials used to control the temperature of ICs to ensure reliability and performance.

Reference links

Supplementary resources to enhance your learning experience.