Capacitance-Voltage (C-V) Profiling

Interactive Audio Lesson

Listen to a student-teacher conversation explaining the topic in a relatable way.

Introduction to C-V Profiling

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Today, we will discuss Capacitance-Voltage profiling. It's a technique used to characterize semiconductor materials by measuring capacitance as a function of applied voltage.

Why is it important to measure capacitance in semiconductors?

Great question! Measuring capacitance helps in understanding properties like doping concentration and interface traps. These parameters directly affect device performance.

What kind of devices use C-V profiling?

It’s primarily used in Metal-Oxide-Semiconductor capacitors, which are key in MOSFETs and other semiconductor devices.

How do we actually perform this measurement?

We apply a voltage bias to the MOS capacitor and measure the capacitance at high frequency, like 1 MHz, to minimize the effects of interface traps.

Can we measure C-V at different frequencies?

Absolutely! Besides high-frequency, we also use quasi-static C-V measurements for more detailed analysis.

In short, C-V profiling is pivotal for semiconductor device characterization and optimization.

Key Measurements in C-V Profiling

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Now let's dive deeper into the measurement techniques used in C-V profiling. We have high-frequency and quasi-static methods.

What’s the difference between these two methods?

High-frequency C-V is fast and useful for analyzing the depletion region efficiently. In contrast, quasi-static C-V uses slower voltage sweeps for more precise trap density measurements.

Does the frequency affect our results?

Yes, the frequency is crucial. High frequency reduces the influence of trapped charges, while quasi-static measurements can reveal nuances of interface trap density.

Which method gives more accurate doping concentration?

High-frequency C-V tends to be more accurate for doping concentration due to its responsiveness to charge dynamics without trap interference.

So why would we still use both methods?

Using both methods allows for a comprehensive characterization, providing complementary information on the semiconductor properties.

To conclude, both measurement techniques are essential in analyzing various material characteristics.

Analyzing Results from C-V Profiling

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Let’s explore how to interpret the results obtained from C-V profiling.

What kind of data do we typically collect?

We collect capacitance values corresponding to various voltage settings, which we then plot as a C-V curve.

What can we learn from these curves?

The curves reveal critical insights, such as the flat-band voltage, doping profile, and potential charges on interfaces.

Can imperfections in the material affect these results?

Definitely! High interface trap density can distort C-V curves, indicating poor quality or defects in the semiconductor.

How can we address these imperfections?

We can improve fabrication methods to reduce defects and optimize the interface for better performance.

In summary, the data from C-V profiling is vital in understanding both material quality and device functionality.

Introduction & Overview

Read summaries of the section's main ideas at different levels of detail.

Quick Overview

Standard

Capacitance-Voltage (C-V) Profiling is essential in semiconductor characterization, particularly for Metal-Oxide-Semiconductor (MOS) capacitors. This method allows for the determination of key material parameters such as doping concentration, oxide thickness, and interface trap density by analyzing capacitance data at high frequency and quasi-static conditions.

Detailed

Capacitance-Voltage (C-V) Profiling

Capacitance-Voltage (C-V) profiling is a critical approach for characterizing semiconductor materials, particularly Metal-Oxide-Semiconductor (MOS) structures. It is employed to derive essential parameters like the doping concentration (N_A), oxide thickness (t_ox), and interface trap density (D_it) that significantly influence the electrical performance of semiconductor devices.

MOS Capacitors

C-V profiling relies on the analysis of MOS capacitors, where the capacitance is measured as a function of applied voltage. By adjusting the voltage while measuring capacitance, valuable information about the semiconductor's properties can be obtained.

Key Measurements

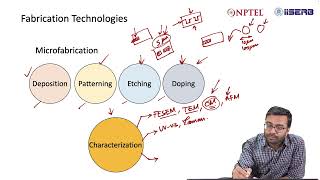

Two key measurement modes are used in C-V profiling:

1. High-frequency C-V (1 MHz): This mode is useful for obtaining information on the depletion region and for effective doping concentration measurements, as it minimizes the effects of slow interface traps.

2. Quasi-static C-V: This mode allows for detailed mapping of the voltage-capacitance relationship, useful for understanding interface trap density and oxide charge variations.

Understanding these parameters through C-V profiling is crucial for the development and optimization of semiconductor devices, ensuring better performance and reliability.

Youtube Videos

Audio Book

Dive deep into the subject with an immersive audiobook experience.

MOS Capacitor Analysis

Chapter 1 of 2

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Measures doping concentration (N_A)

Oxide thickness (t_ox)

Interface trap density (D_it)

Detailed Explanation

MOS Capacitor Analysis is a technique used in semiconductor characterization. It focuses on three key parameters:

1. Doping Concentration (N_A): This indicates how many impurities (dopants) are added to the semiconductor to control its electrical properties. The higher the doping concentration, the more carriers (electrons or holes) are available for conduction.

2. Oxide Thickness (t_ox): This is the thickness of the insulating layer usually made from silicon dioxide in MOS capacitors. It affects how the device operates, especially regarding capacitance and electric fields.

3. Interface Trap Density (D_it): This refers to the number of energy states at the interface between the semiconductor and the insulating layer. High density can lead to performance issues in devices as they trap charge carriers.

In essence, this analysis provides valuable data that aid in optimizing semiconductor devices.

Examples & Analogies

Imagine you are planting a garden (the semiconductor) and you want to know how many plants (dopants) you can fit in your garden based on its size (oxide thickness) and how many weeds (interface traps) you might need to deal with that could hinder your plants from growing. Just like this analysis helps optimize the garden for growth, C-V profiling helps optimize the semiconductor for electronic applications.

Key Measurements

Chapter 2 of 2

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

High-frequency C-V (1MHz)

Quasi-static C-V

Detailed Explanation

Key Measurements in C-V profiling involve different approaches to measuring capacitance:

1. High-Frequency C-V (1MHz): This measurement is performed at a high frequency (1 MHz), which allows for capturing the dynamic behavior of charge carriers in the semiconductor. It helps in determining parameters like doping concentration and oxide properties quickly, implying how the device will perform under fast switching conditions.

2. Quasi-static C-V: This measurement is performed at slower rates and approaches equilibrium conditions. It provides more detailed insights into the semiconductor's static capacitance, which is crucial for understanding how the device behaves under steady-state conditions. This is particularly important for examining the effects of traps at the interface and providing a more accurate assessment of the semiconductor quality.

Examples & Analogies

Think about a car test drive. A high-frequency test (like a 1 MHz measurement) is like speeding down a racetrack to see how fast the car can go under race conditions. In contrast, the quasi-static test is akin to taking a leisurely drive through a neighborhood at a slower pace, allowing you to notice the comfort features and how the car behaves under normal driving conditions. Both tests provide valuable information but in different contexts.

Key Concepts

-

Capacitance-Voltage Profiling: Essential for analyzing semiconductor properties.

-

MOS Capacitor: A key structure in C-V measurements.

-

High-frequency C-V: Method to minimize trap effects.

-

Quasi-static C-V: Method for precise trap density analysis.

-

Doping Concentration: Indicates the level of charge carriers in a semiconductor.

Examples & Applications

C-V profiling can be used to identify whether a semiconductor has been properly doped by measuring the resulting capacitance curves.

Variations in interface trap density can be evaluated using quasi-static C-V, revealing potential reliability issues in semiconductor devices.

Memory Aids

Interactive tools to help you remember key concepts

Rhymes

When capacitance you seek with voltage applied, Understanding C-V is key to not be denied.

Stories

Imagine a detective measuring the 'height' of energy in a MOS bridge. The balance of charge tells stories and secrets about the material.

Memory Tools

CAPTURE: C-V for Analyzing Properties & Trap density Under Review with Electronics.

Acronyms

MOS

Metal-Oxide-Semiconductor; essential for C-V profiling.

Flash Cards

Glossary

- CapacitanceVoltage (CV) Profiling

A technique used to evaluate the electrical properties of semiconductors by measuring capacitance as a function of applied voltage.

- MOS Capacitor

A type of capacitor made from a Metal-Oxide-Semiconductor structure, used in various electronic devices.

- Highfrequency CV

A C-V measurement conducted at high frequency to minimize the effect of interface states.

- Quasistatic CV

A C-V measurement technique involving slow voltage sweeps for detailed characterization of interface states.

- Doping Concentration (N_A)

The concentration of charge carriers in a semiconductor, typically expressed in atoms per cubic centimeter.

- Interface Trap Density (D_it)

A measure of the number of charge traps at the interface between the semiconductor and the oxide.

Reference links

Supplementary resources to enhance your learning experience.