Instructions Per Cycle (IPC)

Interactive Audio Lesson

Listen to a student-teacher conversation explaining the topic in a relatable way.

Understanding IPC

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Today, we’re going to dive into Instructions Per Cycle, or IPC. IPC measures how many instructions a processor can complete in one clock cycle. Can someone tell me why IPC might be important?

I guess higher IPC means better performance?

Exactly! A higher IPC value indicates that the processor is efficiently utilizing its execution units. This means more instructions can be completed in less time. What factors could affect the IPC?

Things like superscalar design and out-of-order execution?

Great points! Superscalar designs allow multiple instructions to be processed at once, while out-of-order execution helps maintain efficiency by executing instructions when resources become available. Let’s keep that in mind as we move forward.

Microarchitectural Factors

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Now, let's discuss how certain microarchitectural enhancements affect IPC. Who remembers what branch prediction does?

It helps the processor guess which way a branch will go, right? This should reduce stalls.

Exactly, excellent correlation! Branch prediction reduces stalls, which helps maintain a steady flow of instructions to execute. And how about instruction prefetching?

It tries to load instructions before they are needed to avoid delays?

Correct again! Instruction prefetching does help in avoiding cache misses, further supporting higher IPC. Overall, understanding these enhancements gives us insights into maximizing processor performance.

Practical Applications of IPC

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Finally, let's apply our understanding of IPC to a real-world scenario. If a processor has an IPC of 4 and runs at a clock speed of 2 GHz, how many instructions can it execute in one second?

I think that’s 4 instructions per cycle at 2 billion cycles per second, so 8 billion instructions?

That’s absolutely right! It shows how important IPC is for overall throughput. Whenever evaluating performance, high IPC is a clear indicator of an efficient processor.

Introduction & Overview

Read summaries of the section's main ideas at different levels of detail.

Quick Overview

Standard

IPC is a critical performance metric for Cortex-A processors that indicates how efficiently the processor utilizes its execution units. A higher IPC value reflects better performance, allowing the processor to complete more instructions within a given time frame.

Detailed

Instructions Per Cycle (IPC)

Instructions Per Cycle (IPC) is a pivotal metric in assessing the performance of Cortex-A processors. It quantifies the number of instructions successfully executed during a single clock cycle. Higher IPC values signify enhanced utilization of the processor's execution units, leading to improved performance and throughput.

Significance of IPC

Understanding IPC is vital for evaluating a processor's efficiency. It directly influences the overall execution speed of applications and systems. Optimizing for higher IPC often involves complex microarchitectural decisions that enhance the core's ability to handle multiple instructions concurrently and effectively.

Factors that Affect IPC

- Superscalar Design: By enabling multiple instructions to be processed simultaneously, a superscalar architecture can significantly boost IPC.

- Out-of-Order Execution: This technique allows processors to execute instructions as resources become available rather than strictly in the order they appear. This reduces idle time and increases IPC.

- Branch Prediction: Accurate predictions reduce the number of pipeline stalls, further aiding in achieving higher IPC.

- Instruction Prefetching: This minimizes cache misses, ensuring a smoother flow of instruction execution, which can improve IPC.

Overall, optimizing IPC is crucial for achieving high performance in Cortex-A architectures.

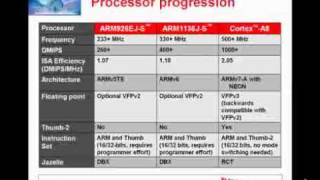

Youtube Videos

Audio Book

Dive deep into the subject with an immersive audiobook experience.

Definition of IPC

Chapter 1 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

● Instructions Per Cycle (IPC)

● Number of instructions completed in one clock cycle.

Detailed Explanation

IPC, or Instructions Per Cycle, is a key indicator of a processor's efficiency. It defines how many instructions the processor can complete in a single clock cycle. A higher IPC value means that the processor is effectively utilizing its execution units to handle multiple instructions simultaneously, thereby enhancing performance.

Examples & Analogies

Think of IPC like a factory assembly line. If each worker could produce one item per minute, the factory would have an IPC of 1. However, if some workers collaborate and manage to produce three items per minute by working together, the IPC rises to 3, demonstrating better efficiency and utilization of available resources.

Importance of IPC

Chapter 2 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

● Higher IPC shows better utilization of execution units.

Detailed Explanation

The importance of IPC lies in its ability to reflect how effectively a CPU is being used. A higher IPC indicates that the execution units (the parts of the CPU that perform operations) are working more efficiently, thus reducing idle time where the CPU might be waiting for instructions or data. This efficiency can lead to faster program execution and more responsive performance in applications.

Examples & Analogies

Imagine a restaurant kitchen where chefs have multiple tasks to manage. If each chef is busy preparing a dish simultaneously, the kitchen operates at a higher IPC. In contrast, if one chef finishes their task and waits idly while others are still working, the overall productivity drops. A well-organized kitchen with efficient task management would strive for a high IPC, just like a well-optimized processor.

Factors Influencing IPC

Chapter 3 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

N/A (implied context regarding factors affecting IPC).

Detailed Explanation

While not detailed in the provided text, several factors influence IPC, such as the microarchitecture design of the CPU, the presence of features like superscalar execution, out-of-order execution, and branch prediction. Each of these factors can contribute to how many instructions the CPU can handle within a single clock cycle. Efficient scheduling of instructions and minimized stalls also play a critical role in maximizing IPC.

Examples & Analogies

Consider a theater production. If the actors (instructions) are well-prepared and have clear direction (architecture and execution features), they can act out scenes with high fluidity and minimal downtime. However, if there are delays in preparation or confusion among the crew, the performance becomes less efficient, resulting in a lower IPC in terms of how quickly the play can be shown to the audience.

Key Concepts

-

Instructions Per Cycle (IPC): A crucial performance metric indicating efficiency of instruction execution.

-

Superscalar Design: Architecture allowing multiple instructions to be processed simultaneously.

-

Out-of-Order Execution: A method to increase utilization of processor resources, executing instructions as they become available.

Examples & Applications

Consider a Cortex-A processor that can execute 4 instructions per cycle. With a clock speed of 2 GHz, it can handle up to 8 billion instructions per second.

In an out-of-order execution scenario, a processor may complete instructions from a different order than they appear in the program to optimize resource usage and reduce wait times.

Memory Aids

Interactive tools to help you remember key concepts

Rhymes

During cycles, instructions fly, higher IPC means you’re reaching the sky.

Stories

Imagine a busy intersection where cars can come from different directions simultaneously. If the traffic light allows more than one lane to go at once—like a superscalar design—more cars can move efficiently, representing how IPC increases when more instructions flow at the same time.

Memory Tools

To remember IPC: 'Instructions Provide Capacity'—where capacity reflects the ability to execute more tasks per cycle.

Acronyms

IPC

'Instructions Per Cycle'—easy to recall fundamentally.

Flash Cards

Glossary

- Instructions Per Cycle (IPC)

A performance metric indicating the number of instructions that a processor can execute in one clock cycle.

- Superscalar Design

An architecture that allows multiple instructions to be issued and executed in a single clock cycle.

- OutofOrder Execution

A technique where instructions are processed based on resource availability rather than their original order.

- Branch Prediction

A method used to guess the outcome of conditional operations to avoid delays in instruction execution.

- Instruction Prefetching

The process of loading instructions from memory into cache in advance to minimize wait times.

Reference links

Supplementary resources to enhance your learning experience.