Branch Delay Slots

Enroll to start learning

You’ve not yet enrolled in this course. Please enroll for free to listen to audio lessons, classroom podcasts and take practice test.

Interactive Audio Lesson

Listen to a student-teacher conversation explaining the topic in a relatable way.

Introduction to Delay Slots

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Today, we're discussing branch delay slots, which help optimize performance in pipelined architectures. Can anyone tell me what a delay slot is?

Isn't it a space after a branch instruction where we can run another instruction?

Exactly! Delay slots occur after a branch instruction is executed. While the processor waits to determine the branch outcome, an independent instruction can be executed, minimizing idle time. We can remember this as the 'Delay is Our Friend' strategy!

But how do we decide which instruction to put in the delay slot?

Great question! Only instructions that don’t depend on the result of the branch should be used. Can anyone think of examples of such instructions?

Like a simple operation, such as adding two numbers that don't involve the branch?

Exactly! Simple, independent operations work well. To consolidate our understanding: delay slots keep the pipeline busy instead of letting it sit idle.

Limitations of Delay Slots

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Now that we've covered what delay slots are, let’s talk about their limitations. Can anyone guess why delay slots have become less popular?

Is it because not all instructions can be executed in those slots?

Correct! Not every instruction fits neatly into a delay slot, especially when dependencies come into play. This creates challenges for instruction scheduling.

So, modern processors have better ways of handling branches instead of relying on delay slots?

Right! Advanced techniques like dynamic branch prediction have taken over. Delay slots have largely become obsolete, as they can complicate the design. Summarizing: while delay slots optimize performance, they have their downsides.

Introduction & Overview

Read summaries of the section's main ideas at different levels of detail.

Quick Overview

Standard

This section discusses branch delay slots, which are empty slots in the instruction pipeline that can be utilized to execute instructions independently of the branch outcome. While this technique reduces performance penalties, its effectiveness is constrained by limitations, particularly as modern processors have moved toward more sophisticated branch prediction strategies.

Detailed

Branch Delay Slots

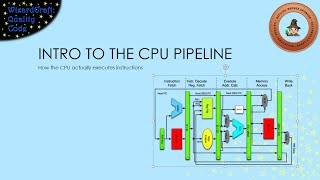

Branch delay slots are an optimization technique in pipelined architectures designed to alleviate the performance lost due to branch instructions. When a processor encounters a branch instruction, it must wait to know whether to take the branch, which can lead to idle time in the pipeline if not managed correctly. To address this, a delay slot refers to a location in the instruction pipeline immediately following a branch instruction. During this delay slot, the processor can execute an instruction that does not rely on the outcome of the branch decision, thus utilizing the time that would otherwise be wasted. This approach seeks to keep the pipeline flowing smoothly and improve overall performance.

However, there are limitations to filling delay slots. Not all instructions can be executed in this manner, and as control hazard management has advanced, many modern processors have phased out the reliance on delay slots in favor of more sophisticated branch prediction mechanisms. Despite this, understanding the concept of delay slots is essential for grasping how processors have evolved to manage the complexities of pipelining efficiently.

Youtube Videos

Audio Book

Dive deep into the subject with an immersive audiobook experience.

What is a Delay Slot?

Chapter 1 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

A delay slot is a slot in the pipeline after a branch instruction, where a useful instruction can be executed while the branch decision is being made.

Detailed Explanation

A delay slot refers to the space or cycle after a branch instruction is executed where the processor can still perform work. During this time, the processor is waiting to know whether the branch was taken or not. To make use of this waiting time, a useful instruction can be executed that does not depend on the outcome of the branch. This helps improve efficiency by not leaving the slot idle.

Examples & Analogies

Imagine a waiter in a restaurant who takes an order from a customer (the branch instruction) and then needs to check in the kitchen to see how long it will take to prepare the order (the branch decision). While they wait for the kitchen to respond, they move on to fill a drink order for another table (the useful instruction). This way, they effectively use their time instead of standing still, just waiting.

Filling Delay Slots

Chapter 2 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Instructions that can be executed without depending on the branch outcome (e.g., independent operations) are scheduled to fill the delay slot, minimizing the performance loss.

Detailed Explanation

To maximize efficiency, it's critical to fill the delay slots with instructions that aren't reliant on the decision of the branch that just occurred. These could be operations that the processor can perform without needing specific data from the branch decision. By scheduling these independent operations in the delay slots, processors aim to keep the pipeline moving smoothly and reduce the potential loss of performance that would occur if the delay slots were left unused.

Examples & Analogies

Think of a construction worker who has just finished laying a foundation (the branch instruction) and is waiting for concrete to set (the branch decision). Instead of doing nothing, the worker can start assembling the tools needed for the next part of the job (the independent operation). This way, when the concrete is ready, they can immediately start working, thus maximizing their productivity.

Limitations of Delay Slots

Chapter 3 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Not all instructions can be scheduled in the delay slot, and modern processors have largely moved away from this technique in favor of more advanced branch prediction mechanisms.

Detailed Explanation

While filling delay slots can improve efficiency, it has limitations. Not every instruction can be safely placed in a delay slot because some instructions may depend on the outcome of the conditional branch. Additionally, as processors have evolved, more advanced techniques such as dynamic branch prediction have emerged that better handle branching and lead to fewer inefficiencies. Consequently, the use of delay slots has declined in favor of these new methods that provide a more robust solution to managing branch penalties.

Examples & Analogies

Consider a chef preparing a meal. While they wait for water to boil (the branch decision), they could chop vegetables (the independent operation). However, if they need a specific vegetable that should only be chopped after the water is boiling (the dependent operation), they cannot do that in the meantime. As cooking techniques and tools evolve (modern processors), chefs increasingly rely on multitasking methods that allow for more efficient preparation, illustrating how delay slots are less frequently utilized in favor of better approaches.

Key Concepts

-

Branch Delay Slot: A place in the instruction pipeline where an independent instruction can be executed while waiting for branch resolution.

-

Independent Instructions: Instructions that do not rely on the results of conditional branches, suitable for delay slots.

Examples & Applications

An ADD instruction that doesn't depend on the outcome of the preceding branch can be placed in a delay slot after a conditional branch.

Using a NOP (No Operation) instruction can be a fallback in cases where no suitable independent instruction is available for delay slots.

Memory Aids

Interactive tools to help you remember key concepts

Rhymes

Delay the branch, fill it with cheer, execute an instruction that’s so clear!

Stories

Imagine a traffic light that pauses cars when changing colors. Instead of stopping completely, a car continues to move if the signal turns yellow, representing how a delay slot works while the branch decision is made.

Memory Tools

D.I.P (Delay Is productive) - Fill the delay slot with Independent operations.

Acronyms

D.S. (Delay Slot) reminds us of 'Deploying Speed' in filling execution gaps.

Flash Cards

Glossary

- Branch Delay Slot

A timing slot in the pipeline following a branch instruction where an independent instruction can be executed while the branch outcome is determined.

- Pipeline

A technique in computer architecture where multiple instruction phases are overlapped to improve instruction throughput.

- Control Hazard

A situation that arises in pipelined processors when the next instruction to be executed depends on the result of a branch instruction, causing potential delays.

- Instruction Scheduling

The process of arranging instructions for execution in a way that optimizes performance and reduces delays.

Reference links

Supplementary resources to enhance your learning experience.