Pipeline Depth and Power Consumption

Enroll to start learning

You’ve not yet enrolled in this course. Please enroll for free to listen to audio lessons, classroom podcasts and take practice test.

Interactive Audio Lesson

Listen to a student-teacher conversation explaining the topic in a relatable way.

Understanding Pipeline Depth

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Today we’re focusing on pipeline depth. Can anyone tell me what pipelining is?

It's a technique used in processors to improve instruction throughput by overlapping execution stages!

Correct! Now, what do you think happens as we increase the depth of the pipeline?

I guess we can process more instructions at once?

Exactly! But with increased depth, we also face challenges. Can anyone name a potential issue?

Maybe power consumption? I heard deeper pipelines use more power.

Great point! Deeper pipelines require more transitions of data, leading to higher power usage.

Does that mean there's a trade-off between depth and efficiency?

Absolutely! Increased depth can boost performance but at the cost of greater complexity and power consumption. To sum up, deeper pipelines can lead to increased efficiency but also present significant challenges.

Managing Pipeline Hazards

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Let's delve deeper into how pipeline hazards are influenced by depth. What do you remember about data hazards?

They occur when an instruction depends on the result of a previous instruction, right?

Correct! As the pipeline depth increases, so does the chance for these hazards to occur. Why do you think that is?

Because more instructions are in the pipeline, increasing the likelihood they’ll depend on each other?

Exactly! This interdependence makes managing pipeline hazards much more complex. Can anyone suggest a strategy to handle these hazards?

We could use techniques like 'stalling' to wait for data to be available?

Good strategy! But stalling also has its cost—leading us back to power consumption concerns. More stalls might mean more wasted cycles, which can affect performance.

So, it's almost like a balancing act between optimizing speed and keeping power use low.

Exactly! Managing this balance is vital when designing modern processors.

Power Consumption Implications

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Now, let’s explore the implications of higher power consumption in deeper pipelines. Why is this significant?

Higher power consumption can lead to overheating and other issues in hardware!

Correct! This creates a pressing need for cooling solutions and can also impact battery life in portable devices. How might this affect overall design choices?

Designers might opt for shorter pipelines to keep power use manageable?

Exactly! Balancing depth for performance with power consumption is a key consideration. Let's recap—what are the main points we've discussed today?

Deeper pipelines improve throughput but increase power usage and complexity, making it crucial to manage hazards effectively.

Well said! Sustainable design is essential in pipeline architecture.

Introduction & Overview

Read summaries of the section's main ideas at different levels of detail.

Quick Overview

Standard

As the depth of a pipeline increases, the challenges associated with managing pipeline hazards escalate, leading to greater power consumption and complexity. This section discusses these dynamics and their impact on processor performance.

Detailed

Pipeline Depth and Power Consumption

The performance of pipelined processors improves significantly by dividing instruction execution into distinct stages. However, with an increase in the depth of the pipeline, various challenges arise. Each additional stage can lead to increased power consumption due to the higher number of active components. Handling these added complexities requires sophisticated designs to manage control, data hazards, and pipeline stalls, which can further exacerbate the power use. As pipelines become deeper, the risk of inefficiencies also rises, which can offset the performance gains achieved through pipelining. This section emphasizes that while pipelining is beneficial for throughput, the trade-offs in power consumption and architectural complexity represent significant concerns in modern processor design.

Youtube Videos

Audio Book

Dive deep into the subject with an immersive audiobook experience.

Understanding Pipeline Depth

Chapter 1 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

The deeper the pipeline, the greater the power consumption and the higher the complexity of managing pipeline hazards.

Detailed Explanation

Pipeline depth refers to the number of stages that an instruction goes through from fetch to execution in a pipelined processor. A deeper pipeline has more stages, allowing for greater instruction throughput since more instructions can be in different phases of execution simultaneously. However, this increased depth also means that the processor uses more power, as it has more components activated at once. Additionally, managing these extra stages can lead to increased complexity, as the processor has to deal with potential hazards like data and control hazards more carefully.

Examples & Analogies

Imagine a fast food restaurant with multiple order stations (pipeline stages). If there are many stations (deep pipeline), the restaurant can serve more customers quickly. However, if one station has a problem (hazard), it can delay the whole process, making it more complex and energy-consuming, similar to how a deeper pipeline causes more challenges for a processor.

Power Consumption Consequences

Chapter 2 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

As pipelines get deeper, managing these risks becomes more difficult, and the benefits of pipelining are offset by higher power usage and complexity.

Detailed Explanation

With deeper pipelines, while achieving higher instruction throughput, the challenges of managing hazards increase. This increased complexity can lead to inefficiencies, as more power is consumed in handling potential stalls and delays caused by these hazards. Essentially, as you try to gain performance through a deeper pipeline, you face diminishing returns because more power is being used to manage those performance gains, leading to potential overheating and increased operational costs.

Examples & Analogies

Think of running a car engine at very high RPMs (like a deep pipeline). It can go faster, but it also consumes more fuel and puts more strain on the engine. Eventually, the extra fuel consumed (higher power usage) doesn't justify the little speed gain, just like the complexity and power costs in deeper pipelines may not always be worth the performance benefits.

Balancing Pipeline Design and Efficiency

Chapter 3 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Pipeline Stall and Complexity: In order to handle hazards, processors may introduce pipeline stalls (delays), which reduce the overall throughput of the system.

Detailed Explanation

To effectively manage hazards in a deep pipeline, processors often introduce stalls. A stall is a temporary halt in the pipeline to allow a specific instruction to complete before others can proceed. While this helps maintain order and correctness of execution, it reduces the overall throughput, since some stages won't be actively processing instructions. The challenge lies in finding a balance between having enough pipeline stages to gain performance and minimizing the stalls that offset those gains.

Examples & Analogies

Consider a relay race where one runner has to wait for the teammate ahead to hand off the baton before taking off. This waiting time (stall) means the team can't run the fastest it could if all runners were constantly moving. Similarly, in a pipeline, stalls slow down the overall performance.

Key Concepts

-

Pipeline Depth: Refers to the number of stages in the processor's pipelining process and affects instruction processing speed.

-

Power Consumption: Represents the electrical energy used by a processor and correlates with pipeline depth due to increased activity.

-

Pipeline Hazards: Issues that arise when the next instruction cannot proceed due to resource conflicts or dependencies.

Examples & Applications

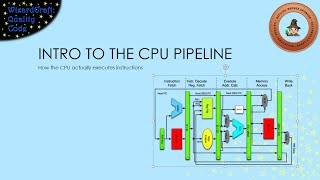

A 5-stage pipeline consists of fetch, decode, execute, memory access, and write back stages, improving fetching and execution speed.

In a deep pipeline, each increase in stage requires more power to manage transitions compared with a shallow pipeline.

Memory Aids

Interactive tools to help you remember key concepts

Rhymes

Pipeline deep, power's steep; the more you stack, the more you reap!

Stories

Picture a factory line where every added step brings in more machines, and each machine uses power. As the line grows, so does the bill!

Memory Tools

DDPP - Deeper designs produce power.

Acronyms

P-D-P - Pipeline Depth and Power Consumption.

Flash Cards

Glossary

- Pipeline Depth

The number of stages in a pipelined processor architecture, with each stage completing part of the instruction processing.

- Power Consumption

The amount of electrical power required by the processor for its operations, which can increase with pipeline depth.

- Pipeline Hazard

Situations that prevent the next instruction in the pipeline from executing in the intended cycle, including control and data hazards.

- Stalling

A technique where the pipeline is intentionally delayed to resolve a hazard, pausing the instruction flow.

Reference links

Supplementary resources to enhance your learning experience.