Pipeline Stall and Complexity

Enroll to start learning

You’ve not yet enrolled in this course. Please enroll for free to listen to audio lessons, classroom podcasts and take practice test.

Interactive Audio Lesson

Listen to a student-teacher conversation explaining the topic in a relatable way.

Understanding Pipeline Stalls

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Today we are discussing pipeline stalls in processors. Can anyone tell me what a pipeline stall is?

Are they the delays that happen during processing?

Exactly! A pipeline stall occurs when the processor must pause execution to manage hazards. Can someone give an example of when a stall might occur?

Maybe when there’s not enough resources available?

Great observation! That's a structural hazard. Structural hazards happen when resources required to execute an instruction are not available, leading to a stall.

So the complexity increases with multiple resources needed, right?

Precisely! As pipelines get more complex, the potential for these stalls increases, affecting throughput.

To remember these concepts, think of 'Stalling saves the day,' meaning sometimes pausing can prevent errors.

The Impact of Stalls on Throughput

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Now, let's talk about how these stalls impact throughput. What does throughput refer to?

Isn't it the number of instructions executed in a given time?

Exactly! When we introduce stalls, we reduce the number of instructions that can be executed in that timeframe. How do you think increasing stalls might affect overall performance?

It would slow everything down, right?

Correct! So there’s a trade-off in designing pipelined processors. The more complexity there is, the harder it becomes to avoid those stalls.

Remember, 'More Complexity, More Stalls.' It's a good rule of thumb.

Managing Complexity in Pipelining

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

To handle pipeline stalls, what could designers implement?

Maybe out-of-order execution?

That’s one method! Out-of-order execution allows instructions to run as resources become available rather than strictly following the original order. What else might help?

Using better branch prediction techniques?

Absolutely right! Effective prediction can minimize mispredictions and the stalls that come with them.

To sum up today's lesson, just remember 'Minimize Stalls, Maximize Flow' as a guiding mantra in pipeline design.

Introduction & Overview

Read summaries of the section's main ideas at different levels of detail.

Quick Overview

Standard

This section discusses how pipeline stalls are introduced in processors to manage hazards, which in turn adds complexity to the pipeline architecture. It emphasizes the trade-off between achieving optimal throughput and the challenges posed by complex pipeline management.

Detailed

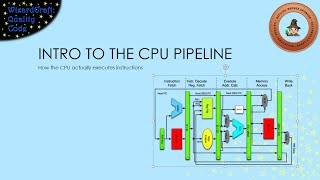

Pipeline Stall and Complexity

In modern pipelined processors, performance can often be hindered by pipeline stalls, which are deliberate delays introduced to manage hazards effectively. While pipelining boosts processing speed, these stalls are necessary to maintain instruction integrity across various stages of execution. The more complex the pipeline design, the more challenging it becomes to avoid stalls, as it requires intricate management of resource availability and timing. This section explores the intricate relationship between pipeline complexity, the introduction of stalls, and their cumulative impact on overall system throughput.

Youtube Videos

Audio Book

Dive deep into the subject with an immersive audiobook experience.

Introduction to Pipeline Stalls

Chapter 1 of 2

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

In order to handle hazards, processors may introduce pipeline stalls (delays), which reduce the overall throughput of the system.

Detailed Explanation

Pipeline stalls are intentional delays introduced in a pipelined processor to manage hazards. Hazards occur when two or more instructions cannot be executed in the expected sequence due to resource conflicts or data dependencies. When a stall is introduced, the processor pauses the flow of instructions to ensure that the correct instructions are executed, even if it means reducing the number of instructions that can be processed at one time.

Examples & Analogies

Imagine a busy intersection where several cars are waiting to enter but cannot proceed until the light turns green. The traffic light causes a delay, ensuring that vehicles only move when it is safe, even if that means not all cars are moving at once. Similarly, pipeline stalls ensure that instructions execute safely, even if it slows down the overall processing.

Effects of Complexity on Stalls

Chapter 2 of 2

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

The more complex the pipeline, the more difficult it is to manage and avoid stalls.

Detailed Explanation

As pipelines become more complex, with multiple instructions being processed simultaneously, the chances of hazards increase. This complexity requires more sophisticated mechanisms to detect and handle hazards effectively. Consequently, the risk of stalls rises, as managing the various dependencies and conflicts becomes challenging. When stalls occur, they impact overall performance, leading to a less efficient processor.

Examples & Analogies

Think of a multitasking chef in a busy restaurant kitchen. If there are too many dishes being prepared at once and not enough counter space, the chef may need to pause (stall) work on certain dishes to keep things organized. However, as the kitchen gets busier (more complex), it becomes harder for the chef to manage all the dishes without pausing, leading to longer wait times for customers (reduced overall throughput).

Key Concepts

-

Pipeline Stall: A temporary delay in execution caused by the need to resolve a hazard.

-

Throughput: The efficiency of instruction execution in a pipeline, critically affected by stalls.

-

Complexity Management: Techniques such as out-of-order execution and effective branch prediction help minimize stalls.

Examples & Applications

In a pipelined processor, if a data dependency exists between two consecutive instructions, a stall may occur as the pipeline waits for the data to be ready for execution.

When a memory access operation and an arithmetic operation occur simultaneously but require the same resource, a structural hazard can cause a stall in the pipeline.

Memory Aids

Interactive tools to help you remember key concepts

Rhymes

In a line of execution, wait for the right resolution; stalls may slow, but they help the flow.

Stories

Imagine a busy highway with many cars trying to merge; if they all rush at once, they create a blockage. Pipeline stalls work similarly, allowing cars to merge safely and maintain flow.

Memory Tools

Think 'S.T.A.L.L.': Survive the Traffic And Let Layers.

Acronyms

P.A.C.E. for Pipeline Action

Pause to Avoid Conflicts and Enhance throughput.

Flash Cards

Glossary

- Pipeline Stall

A delay in instruction execution that occurs when the processor must pause to resolve hazards.

- Throughput

The rate at which instructions are executed and completed in a processor in a given time period.

- Structural Hazard

A type of hazard that occurs when there are insufficient resources to execute all instructions in the pipeline concurrently.

- Hazard

Conditions that prevent the next instruction in the pipeline from executing during its designated clock cycle.

Reference links

Supplementary resources to enhance your learning experience.