Impact on Performance

Enroll to start learning

You’ve not yet enrolled in this course. Please enroll for free to listen to audio lessons, classroom podcasts and take practice test.

Interactive Audio Lesson

Listen to a student-teacher conversation explaining the topic in a relatable way.

Understanding Control Hazards

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Welcome class! Today, we are diving into the concept of control hazards, also known as branch hazards. Can anyone tell me what a control hazard is?

Is it when the pipeline has to wait because it doesn’t know what instruction comes next after a branch?

Exactly! Control hazards happen when the outcome of a branch instruction affects which instruction the processor fetches next. These hazards can lead to significant delays. Remember the acronym 'BRANCH' — 'Branch Results Affect Next Cycle Harvest.'

Why are these hazards such a big problem for performance?

Great question! The longer the delay from these branches, the worse the performance hits, especially in deeply pipelined architectures. If the pipeline has to frequently stall, it can’t process other instructions efficiently.

To summarize, control hazards delay instruction fetches due to uncertainty after branch instructions, greatly impacting processing efficiency.

Branch Decision Delay

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Now let’s explore branch decision delays. Can anyone explain how these delays affect the pipeline's performance?

Isn’t it like waiting for a green light before moving at a traffic signal? If it takes too long to change, everything behind has to stop.

That's a fantastic analogy! Just like cars waiting for a green light, the pipeline must wait for a branch decision before it can continue executing instructions. This leads to inefficiencies and reduces throughput.

So, if we have deeper pipelines, won’t the delays matter even more?

Exactly! In a deeper pipeline, the cumulative effect of these waiting periods can drastically decrease the overall CPU performance. Remember: 'Deeper pipelines mean deeper delays!' It’s essential to keep this in mind when designing computer architectures.

Performance Impact Summary

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Alright, let’s review what we’ve learned about the impact of control hazards on performance. What are your main takeaways?

Control hazards delay instruction fetching, negatively impacting performance.

The longer the delay, the more serious the performance issue, especially in deep pipelines.

Exactly! It’s crucial to address these hazards effectively to improve processing performance. Remember the key points: control hazards are the result of branch instructions and can seriously impact pipeline efficiency. Excellent work today, everyone!

Introduction & Overview

Read summaries of the section's main ideas at different levels of detail.

Quick Overview

Standard

Control hazards, which result from waiting for the outcome of branch instructions, can severely impact the performance of pipelined processors. Understanding these hazards is crucial for enhancing processing efficiency.

Detailed

Impact on Performance

Control hazards, also known as branch hazards, arise when a processor must complete a branch instruction before determining which instruction to execute next. This delay in decision-making negatively affects the overall performance of pipelined architectures. In particular, the deeper the pipeline, the greater the impact of these delays.

Branch instructions (e.g., conditional statements), when executed, necessitate the processor to pause instruction fetching until the result of the branch is known. If the delay is substantial, it leads to inefficient processing and wasted resources, as the pipeline cannot effectively utilize its potential. In modern processors with extensive pipelines, these control hazards represent a significant challenge, making their mitigation a key area of focus for improving performance.

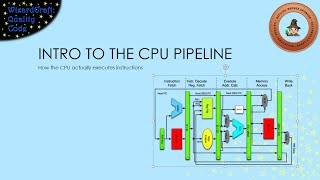

Youtube Videos

Audio Book

Dive deep into the subject with an immersive audiobook experience.

Understanding Performance Impact

Chapter 1 of 1

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

The longer the delay due to branching, the more performance is impacted, especially in processors with deep pipelines.

Detailed Explanation

In pipelined architectures, instructions are executed in stages, allowing multiple instructions to be processed simultaneously. However, when a branch instruction occurs, the pipeline may need to pause to understand which instruction to execute next. If this delay is prolonged, it can significantly lower the overall speed and efficiency of the processor, particularly in deep pipelines, where the number of stages is high. More stages mean more potential delays when a branch occurs, which negatively affects the performance of the processor.

Examples & Analogies

Imagine a factory assembly line. If one worker (like a branch instruction) needs to make a decision on what part to assemble next and takes a long time to decide, all the workers behind them have to stop working, which causes delays in the entire production process. This is similar to how a branch instruction can disrupt the flow of processing in a pipelined CPU.

Key Concepts

-

Control Hazards: Delays caused by waiting for branch outcomes, impacting the pipeline.

-

Branch Decision Delay: The time the pipeline must pause to know the next instruction.

-

Performance Impact: Delays significantly affect the efficiency of deeply pipelined architectures.

Examples & Applications

When a processor encounters an 'if' statement, it cannot fetch the next instruction until it knows whether the condition is true or false.

In a loop, each iteration involves a branch decision that can halt instruction fetching until resolved.

Memory Aids

Interactive tools to help you remember key concepts

Rhymes

Hazard hazard, what a sight, delays our branches, stop the flight.

Stories

Imagine being at a crossroads, you need a sign to decide whether to go left or right. Until you get the signal, you must wait, and everyone behind you is stalled. That's just like a processor waiting for a branch outcome.

Memory Tools

DIDDY: Delay In Decision Diminishes Yield - reminding us that delays in decision-making (like branches) can reduce processing output.

Acronyms

B.A.D

Branches Are Delays

highlighting that branches introduce delays in the pipelining process.

Flash Cards

Glossary

- Control Hazard

A situation in pipelined architecture where the processor must wait for the outcome of a branch instruction to proceed.

- Branch Instruction

An instruction used to change the flow of control in a program.

- Pipeline

A technique where multiple instruction phases are overlapped during execution to improve performance.

- Branch Decision Delay

The delay caused by waiting for the result of a branch instruction before fetching the next instruction.

Reference links

Supplementary resources to enhance your learning experience.