Superscalar Processors

Enroll to start learning

You’ve not yet enrolled in this course. Please enroll for free to listen to audio lessons, classroom podcasts and take practice test.

Interactive Audio Lesson

Listen to a student-teacher conversation explaining the topic in a relatable way.

Understanding Superscalar Architecture

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Today we'll dive into superscalar processors. Can anyone explain what 'superscalar' means?

I think it means that the processor can handle more than one instruction at a time, right?

Exactly! A superscalar processor can fetch and execute multiple instructions simultaneously. This contrasts with scalar processors, which handle just one instruction per cycle.

How does that improve performance?

Great question! With the capability to execute multiple instructions at once, superscalar processors significantly increase throughput, especially in tasks that require heavy computation.

What about the execution units?

Excellent point! Superscalar processors have multiple execution units, allowing them to handle different types of instructions simultaneously. This means not all units have to wait for the same data.

To summarize this session, superscalar processors can execute multiple instructions per cycle by utilizing several execution units, significantly improving performance.

Instruction Dispatch Mechanism

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Let's get into the instruction dispatch mechanism. Why do you think this is important in a superscalar processor?

Maybe because there are multiple instructions to manage?

Right! The instruction dispatch mechanism ensures that instructions are sent to the correct execution units efficiently. It determines which unit to use based on availability and dependency.

Are there challenges with that?

Definitely! One challenge is ensuring that dependent instructions are executed in the correct order. This is where techniques like out-of-order execution come into play, which we will discuss later.

So, out-of-order execution helps minimize delays?

Exactly! By allowing instructions to execute as their operands become available, we reduce idle times and increase overall throughput.

In summary, the instruction dispatch mechanism is critical for managing instruction flow and optimizing execution unit utilization in a superscalar processor.

Introduction & Overview

Read summaries of the section's main ideas at different levels of detail.

Quick Overview

Standard

This section discusses superscalar processors, which incorporate multiple pipelines to allow the simultaneous execution of several instructions. By mitigating issues associated with deep pipelining, these processors significantly enhance overall system performance and efficiency through advanced architectural techniques.

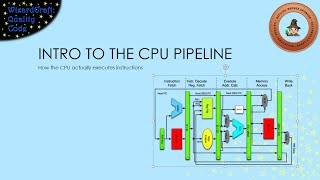

Youtube Videos

Audio Book

Dive deep into the subject with an immersive audiobook experience.

Introduction to Superscalar Processors

Chapter 1 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

• Superscalar Processors: These processors contain multiple pipelines, allowing them to execute several instructions simultaneously, which mitigates some of the issues of deep pipelining.

Detailed Explanation

Superscalar processors are a type of CPU architecture designed to enhance performance by allowing the execution of more than one instruction at a time. Unlike traditional scalar processors, which process one instruction per clock cycle, superscalar processors have multiple execution units (pipelines) that can handle several instructions concurrently. This parallel execution capability addresses the performance limitations of deep pipelining, which may stall due to resource contention or dependencies between instructions.

Examples & Analogies

Imagine a restaurant kitchen where a single chef can cook only one dish at a time. This setup may result in long waiting times. Now, if you have several chefs working in parallel, each one preparing a different dish at the same time, the kitchen can serve multiple customers much faster. Superscalar processors function similarly—they have multiple 'chefs' (execution units) working on different instructions simultaneously, leading to increased throughput and efficiency.

Execution of Instructions in Superscalar Processors

Chapter 2 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

• Instruction Issue: Superscalar processors fetch multiple instructions from memory and issue them to different execution units based on availability and dependencies.

Detailed Explanation

In a superscalar processor, the instruction issue stage is crucial because it allows multiple instructions to be fetched and dispatched at once. The processor analyzes the instruction dependencies to determine which instructions can be executed simultaneously. This means that it not only focuses on fetching instructions but also on intelligently breaking them down and distributing their execution across multiple units to maximize efficiency.

Examples & Analogies

Think of a factory assembly line where various tasks are performed simultaneously. Each worker specializes in a specific task: one assembles parts, another paints, while yet another performs quality checks. If one worker is delayed, others can continue their work without having to stop the entire production line. Superscalar architectures use this principle to manage instruction execution, reducing delays and improving overall performance.

Challenges with Superscalar Processors

Chapter 3 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

• Resource Management: Managing resources effectively becomes a key challenge in superscalar architectures to avoid stalls due to conflicts for execution units.

Detailed Explanation

While superscalar processors can execute multiple instructions simultaneously, they face the challenge of resource management. Conflicts can occur if multiple instructions demand access to the same execution unit or data. It requires sophisticated scheduling and out-of-order execution strategies to ensure that resources are allocated efficiently and no instruction stalls due to resource contention, thereby maintaining high performance.

Examples & Analogies

Imagine a busy intercity highway where multiple cars (instructions) want to access specific lanes (execution units) at the same time. If everyone tries to merge into the same lane, traffic jams occur. Effective traffic management systems (resource allocation strategies) are needed to keep the cars moving smoothly, ensuring that all available lanes are utilized without causing delays—just like how a superscalar processor must manage its execution units to avoid performance stalls.

Key Concepts

-

Superscalar Architecture: Allows multiple instructions to be executed in parallel, enhancing CPU performance.

-

Execution Units: Processor components dedicated to executing specific instruction types, optimizing parallel execution.

-

Instruction Dispatch Mechanism: The process of directing instructions to appropriate execution units.

-

Out-of-Order Execution: A method of executing instructions as soon as their required data is available, which minimizes delays.

Examples & Applications

A modern CPU like Intel's Core i7 can execute up to 8 instructions per clock cycle by utilizing multiple execution units.

Superscalar processors can run different types of operations such as integer arithmetic and floating-point calculations simultaneously.

Memory Aids

Interactive tools to help you remember key concepts

Rhymes

In a superscalar, instructions race, executing many at a rapid pace.

Stories

Imagine a factory with multiple assembly lines (execution units) handling different tasks (instructions) simultaneously, maximizing productivity without waiting.

Memory Tools

S-E-I-O: Superscalar - Execute - Instruction - Out-of-order to remember the essentials.

Acronyms

PES

Parallel Execution System

emphasizing the parallel processing capability of superscalar processors.

Flash Cards

Glossary

- Superscalar Processor

A type of CPU architecture that allows multiple instructions to be executed simultaneously within a single clock cycle.

- Execution Unit

A component of the CPU where actual instruction execution takes place, such as ALUs or floating-point units.

- Instruction Dispatch

The mechanism by which instructions are assigned to execution units based on their availability and dependence.

- OutofOrder Execution

A technique where the processor executes instructions as their operands are ready, rather than in strict program order.

Reference links

Supplementary resources to enhance your learning experience.