Exploiting Instruction-Level Parallelism

Enroll to start learning

You’ve not yet enrolled in this course. Please enroll for free to listen to audio lessons, classroom podcasts and take practice test.

Interactive Audio Lesson

Listen to a student-teacher conversation explaining the topic in a relatable way.

Understanding ILP

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Today, we will explore Instruction-Level Parallelism or ILP. Can anyone tell me what they think ILP means?

Is it about running multiple instructions at the same time?

Exactly! ILP is the ability of the processor to execute multiple independent instructions concurrently. This is crucial for improving performance without needing to increase clock speed.

So, does it help in reducing the time taken to execute a program?

Yes, that's right. By executing multiple instructions simultaneously, ILP can significantly reduce execution time. Remember, higher throughput with lower latency is what we aim for!

What’s the basic concept of ILP then?

ILP is enabled through two main methods: handling multiple instructions at the same time or by overlapping their execution phases using a technique called pipelining. Now, let’s summarize this session. ILP enhances performance by allowing concurrent instruction execution.

Performance Impact of ILP

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Now, why is ILP important for CPU performance? Can anyone guess?

Maybe it allows more tasks to be completed faster?

Good observation! ILP allows processors to execute more instructions per clock cycle. This means the execution time of a program can be greatly reduced. Let’s break it down: throughput and latency!

What’s throughput again?

Throughput is essentially the total number of instructions completed per unit time. And latency is the time it takes for one instruction to complete. Can someone tell me how these two are related in the context of ILP?

By improving throughput, we can still keep latency low, right?

Exactly! That’s the beauty of ILP. Just remember, however, that the effectiveness of ILP can vary depending on the program and hardware capabilities!

Techniques to Exploit ILP

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Let’s explore the techniques we can use to exploit ILP. Who remembers any techniques?

Pipelining?

Correct! Pipelining is one technique. It allows different stages of multiple instructions to execute simultaneously in different parts of the processor. Can anyone name another?

Dynamic Scheduling?

Yes! Dynamic scheduling helps by allowing instructions to execute as soon as their operands are ready, rather than in a strict order. What about the benefit of Out-of-Order Execution?

It allows instructions to be processed as their data is ready instead of their order?

Exactly! Now let's summarize what we've covered: techniques like pipelining, dynamic scheduling, and out-of-order execution play a critical role in leveraging ILP for better performance.

Managing Data Hazards

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

What issues might arise when trying to exploit ILP? Anyone have an idea?

Data hazards?

Right! Data hazards occur when instructions are dependent on data from each other. What are the three types of data hazards we should be aware of?

RAW, WAR, and WAW?

Excellent! RAW stands for Read-After-Write, WAR stands for Write-After-Read, and WAW is Write-After-Write. Can anyone suggest how to resolve these hazards?

By using forwarding, stalls, or register renaming?

Correct! Forwarding sends data directly to where it's needed, stalls introduce delays, and register renaming helps eliminate certain hazards. Let’s conclude this session: Data hazards impact ILP and can be managed through various techniques.

Control Hazards and Their Management

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Moving on, let’s talk about control hazards, especially as they relate to branch instructions. What is a control hazard?

It's when the pipeline has to wait to see where to go after a branch instruction?

Exactly right! If the processor doesn’t know the branch direction, it can’t fetch the next instructions. So, how can we address this?

Branch prediction?

Yes, branch prediction anticipates the outcomes of branches to minimize delays! What is a branch target buffer?

Is it a cache for storing branch target addresses?

Absolutely! It allows the processor to continue fetching without waiting for the branch decision. To wrap up, control hazards can indeed impact ILP, but techniques like prediction and buffers help manage these challenges.

Introduction & Overview

Read summaries of the section's main ideas at different levels of detail.

Quick Overview

Standard

Instruction-Level Parallelism (ILP) is crucial for improving processor efficiency by allowing multiple independent instructions to be executed simultaneously. This section outlines the importance of ILP, its effects on performance, various techniques for its exploitation, and challenges like data and control hazards.

Detailed

Detailed Summary of Exploiting Instruction-Level Parallelism

Youtube Videos

Audio Book

Dive deep into the subject with an immersive audiobook experience.

Introduction to Instruction-Level Parallelism (ILP)

Chapter 1 of 4

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Instruction-Level Parallelism (ILP) refers to the ability of a processor to execute multiple instructions concurrently, leveraging the inherent parallelism in a program’s instruction stream.

● Definition of ILP: ILP is the parallel execution of independent instructions in a program.

● Importance of ILP: By exploiting ILP, modern processors can achieve higher performance without increasing the clock speed.

● Basic Concept: ILP is enabled when multiple instructions can be executed simultaneously, either in parallel or by overlapping their execution phases in a pipeline.

Detailed Explanation

Instruction-Level Parallelism (ILP) allows processors to execute several instructions at the same time instead of waiting for each instruction to finish before starting the next.

1. Definition: ILP means that independent instructions in a program can run in parallel. Independent instructions are those that do not rely on the results of one another.

2. Importance: ILP is crucial because it enhances the performance of modern processors by ensuring tasks are completed faster without needing to increase the clock speed, which can make the processor run hotter and consume more power.

3. Basic Concept: The basic logic of ILP is that multiple instructions can be executed simultaneously or their execution phases can overlap in a pipelining manner, which means after one instruction begins its execution, the next can start even while the first one is still processing.

Examples & Analogies

Think of a kitchen preparing a meal with multiple chefs: Each chef is responsible for a different dish. While Chef A is boiling water, Chef B can chop vegetables. Instead of one chef waiting for another to finish before starting their task, they all work concurrently, similar to how ILP allows multiple instructions to run at the same time.

Impact on Processor Performance

Chapter 2 of 4

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

ILP has a significant impact on processor performance, particularly in how many instructions can be executed per clock cycle.

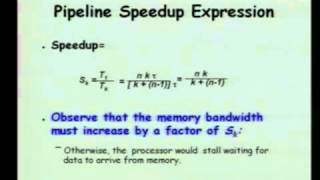

● Speedup through ILP: By executing multiple instructions concurrently, the total execution time of a program can be reduced.

● Throughput and Latency: ILP can improve throughput (instructions per unit time) without significantly increasing latency (the time for a single instruction to complete).

● Limitations of ILP: The potential for exploiting ILP depends on the nature of the program and the hardware’s ability to manage parallel execution.

Detailed Explanation

The exploitation of ILP directly enhances how quickly a processor can execute commands:

1. Speedup through ILP: By running multiple instructions at once, programs can finish their execution faster, which is crucial in applications requiring quick responses, such as video games or real-time data processing.

2. Throughput and Latency: Throughput refers to how many instructions are executed per second. ILP increases this number, improving overall system performance, while latency measures how long it takes to complete one instruction. Ideally, ILP raises throughput without significantly increasing latency, offering both speed and efficiency.

3. Limitations: However, the ability to utilize ILP effectively is limited by the type of programs being run and how well the hardware can handle and allocate resources for parallel execution.

Examples & Analogies

Imagine a busy restaurant with many orders coming in. If several chefs can work on different meals simultaneously, the restaurant can serve food faster, enhancing customer satisfaction (speedup and throughput). If one chef can only make a salad while the others wait for him to finish, this could slow down service (latency), highlighting that not all tasks can be parallelized effectively.

Techniques for Exploiting ILP

Chapter 3 of 4

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Several techniques have been developed to exploit ILP, from simple pipelining to more sophisticated hardware mechanisms.

● Pipelining: Already covered in earlier chapters, pipelining helps exploit ILP by allowing multiple stages of instructions to execute simultaneously.

● Superscalar Architecture: Superscalar processors have multiple pipelines, allowing them to issue multiple instructions per cycle.

● Dynamic Scheduling: Hardware dynamically schedules instructions to execute as soon as the required operands are available, optimizing ILP.

● Out-of-Order Execution: Instructions are executed as their operands become available, not necessarily in the order they appear in the program, which helps improve ILP.

● Register Renaming: Avoids data hazards by dynamically assigning registers to hold intermediate results, allowing instructions to proceed without waiting for previous instructions to complete.

Detailed Explanation

Here are several techniques to maximize ILP in processors:

1. Pipelining: This technique breaks instruction execution into different stages, enabling the overlap of instruction processing, which speeds up execution.

2. Superscalar Architecture: This allows multiple instructions to be processed simultaneously, using several pipelines to maximize efficiency.

3. Dynamic Scheduling: This method allows the processor to decide the execution order based on data availability, ensuring that instructions are executed as soon as their required information is ready, minimizing idle time.

4. Out-of-Order Execution: In this technique, processors do not focus on the original order of instructions but instead execute them based on when the data they need is available, which enhances throughput and ILP.

5. Register Renaming: This feature helps to eliminate conflicts between instructions, enabling smoother execution without waiting for other instructions to finish writing to registers.

Examples & Analogies

Think of a factory assembly line: Pipelining is like dividing the assembly process into multiple stations (each doing only part of the work). Superscalar architecture is like having several lines operating at the same time, building different products. Dynamic scheduling is akin to rearranging tasks among workers based on what materials are available, while out-of-order execution is like allowing workers to complete their tasks in any order. Register renaming is like ensuring that different employees have access to different tools to avoid delays, maintaining a steady workflow.

Addressing Data Hazards

Chapter 4 of 4

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

To efficiently exploit ILP, data hazards need to be addressed. Data hazards occur when instructions depend on the results of previous instructions.

● Types of Data Hazards:

○ RAW (Read-After-Write): Occurs when an instruction tries to read a register before the previous instruction writes to it.

○ WAR (Write-After-Read): Occurs when an instruction tries to write to a register before another instruction reads it.

○ WAW (Write-After-Write): Occurs when two instructions try to write to the same register in the wrong order.

● Hazard Resolution Techniques:

○ Forwarding (Data Bypassing): Data from one pipeline stage is sent directly to another stage without waiting for it to be written to the register file.

○ Stall Cycles: When forwarding is not possible, a stall is introduced to delay the dependent instruction until the hazard is resolved.

○ Register Renaming: Used to eliminate WAR and WAW hazards by dynamically allocating new registers.

Detailed Explanation

Data hazards pose significant challenges for ILP, as they can stall instruction execution:

1. Types of Data Hazards: There are three main categories of hazards:

- RAW: This happens when an instruction needs data that hasn’t been written yet because another instruction is still writing it.

- WAR: This occurs if an instruction writes data before another one has had a chance to read it.

- WAW: This happens when two instructions attempt to write to the same register in the wrong sequence.

2. Hazard Resolution Techniques: To handle these hazards, processors use several methods:

- Forwarding: This method allows data to bypass the normal write process, sending it directly to where it is needed next.

- Stall Cycles: Sometimes, the processor has to wait, introducing a pause until the necessary data becomes available.

- Register Renaming: This technique dynamically assigns new registers to eliminate write conflicts, maintaining smooth execution.

Examples & Analogies

Imagine a relay race, where runners must pass a baton (data) to the next runner (instruction). A RAW hazard is like needing the baton back from the previous runner who hasn’t completed their part yet. A WAR hazard would be if a runner tried to grab the baton before the previous one has passed it. If two runners tried to grab the baton at the same time, that reflects a WAW hazard. To resolve these issues, one runner might wait (stall cycles), while another may use a different track for ease (register renaming).

Key Concepts

-

Parallel Execution: The ability to process multiple instructions at once.

-

Data Hazards: Conditions that arise when instructions depend on other instructions' results.

-

Control Hazards: Delays in pipeline processing due to branch instructions.

Examples & Applications

An example of ILP can be found in modern processors like Intel’s, which use superscalar architecture to issue multiple instructions per cycle.

Dynamic scheduling is utilized in ARM processors, which allows for more flexible execution of instructions based on operand availability.

Memory Aids

Interactive tools to help you remember key concepts

Rhymes

ILP is great, it helps instructions relate, executing in parallel, it elevates!

Stories

Imagine a busy server room where multiple tasks can run at the same time, speeding up project completion without waiting.

Memory Tools

For data hazards, remember RAW, WAR, WAW – it’s the order that counts.

Acronyms

ILP = Instruction Level Parallelism. Think ILP for efficient instruction handling.

Flash Cards

Glossary

- InstructionLevel Parallelism (ILP)

The parallel execution of independent instructions in a program.

- Throughput

The number of instructions completed per unit time.

- Latency

The time taken for a single instruction to complete.

- Pipeline

A technique where multiple instruction stages are processed simultaneously.

- Dynamic Scheduling

A method that schedules instructions based on the availability of operands.

Reference links

Supplementary resources to enhance your learning experience.