Techniques for Exploiting ILP

Enroll to start learning

You’ve not yet enrolled in this course. Please enroll for free to listen to audio lessons, classroom podcasts and take practice test.

Interactive Audio Lesson

Listen to a student-teacher conversation explaining the topic in a relatable way.

Understanding Pipelining

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Today, we are going to discuss pipelining, a fundamental technique for exploiting ILP. Pipelining allows different stages of instruction execution to overlap.

Can you explain how pipelining actually works?

Absolutely! Think of pipelining as an assembly line in a factory. Just as different workers perform different tasks simultaneously in an assembly line, different stages of instruction processing occur at the same time in pipelining.

So, it helps in speeding up the execution?

That's right! By allowing instructions to move through different stages at once, pipelining increases the overall instruction throughput. Just remember the acronym 'PES' for Pipelining's Efficiency through Stages.

What are the stages in a typical pipeline?

Great question! The stages usually include instruction fetch, decode, execute, memory access, and write back. Each instruction is at a different stage, maximizing resource use.

Why is it not always perfect? Are there any drawbacks?

Indeed! Pipeline hazards can occur like data hazards and control hazards, which we will explore later. But for now, remember that pipelining significantly enhances ILP by increasing concurrency.

In summary, pipelining allows instructions to be processed simultaneously in multiple stages, boosting execution efficiency. Keep the 'PES' acronym in mind!

Exploring Superscalar Architecture

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Moving on to another key technique, let's explore superscalar architecture. Can anyone tell me what they expect this involves?

Does it have to do with executing multiple instructions at the same time?

Exactly! Superscalar architecture allows processors to issue multiple instructions per clock cycle by having multiple execution units. It’s like having multiple lanes on a highway.

How does that happen in practice?

Well, the CPU can independently execute different instructions in parallel, which boosts overall throughput. A key term here is 'issue width', which refers to how many instructions can be processed simultaneously.

Are there challenges associated with this architecture?

Definitely! Instruction dependencies can be a major hurdle, as some instructions depend on the outcomes of others. That's why we also need effective scheduling mechanisms.

In summary, superscalar architecture leverages multiple execution units to greatly enhance instruction throughput, but comes with challenges that we need to address.

Dynamic Scheduling

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Next, let's talk about dynamic scheduling. Why do you think we need it?

To make sure we can execute instructions efficiently?

Yes! It's all about optimizing the execution flow. Dynamic scheduling allows the processor to decide the best order to execute instructions based on the availability of operands.

That sounds like it would help with delaying problems, right?

Exactly! It makes the best decision on the fly. Now combine that with out-of-order execution, which executes instructions as operands become available regardless of their order in the program. This can really boost ILP.

How do we know which instructions can be executed out-of-order?

The CPU uses mechanisms that track dependency information. It’s all about maximizing efficiency by utilizing all available resources optimally.

So in summary, dynamic scheduling and out-of-order execution work together to enhance ILP by allowing instructions to be processed in the most efficient order.

Register Renaming

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Finally, let’s wrap up with register renaming. Can anyone tell me why register renaming is needed?

To prevent data hazards?

Correct! Register renaming helps avoid data hazards by dynamically allocating registers for intermediate results. This allows instructions to proceed without waiting for previous instructions to complete.

How does it help if the current instruction is waiting?

It allows the processor to keep executing other instructions instead of being stalled. Essentially, it increases parallelism and the effective use of available registers.

Are there any drawbacks?

While it benefits performance, register renaming increases complexity in the hardware design and necessitates additional management overhead.

In summary, register renaming is a key technique for effectively managing data hazards, facilitating smoother instruction execution and greater exploitation of ILP.

Introduction & Overview

Read summaries of the section's main ideas at different levels of detail.

Quick Overview

Standard

Various techniques have been developed to effectively exploit ILP, including advanced concepts like superscalar architecture, dynamic scheduling, out-of-order execution, and register renaming. These allow processors to execute multiple instructions concurrently, significantly improving performance.

Detailed

Techniques for Exploiting ILP

This section discusses the various techniques designed to exploit Instruction-Level Parallelism (ILP) in modern processors, which is crucial for enhancing performance without solely relying on clock speed increases. The main techniques include:

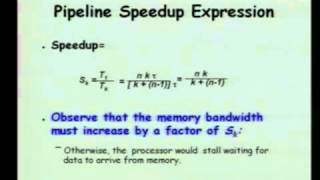

- Pipelining: A fundamental technique that allows different stages of instruction execution to proceed simultaneously, increasing concurrency.

- Superscalar Architecture: This architecture supports multiple pipelines, enabling the processor to issue several instructions per cycle, thus amplifying ILP.

- Dynamic Scheduling: Hardware components dynamically decide the order of instruction execution based on operand availability, ensuring efficient use of available resources.

- Out-of-Order Execution: This allows for the execution of instructions as their operands are ready rather than the order they appear in the program, enhancing parallel processing capabilities.

- Register Renaming: To mitigate data hazards that can stall instruction execution, register renaming dynamically assigns registers for intermediate results, allowing smoother instruction flow.

Each of these techniques contributes to higher throughput and reduced execution time in processing complex instruction streams.

Youtube Videos

Audio Book

Dive deep into the subject with an immersive audiobook experience.

Pipelining

Chapter 1 of 5

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Pipelining: Already covered in earlier chapters, pipelining helps exploit ILP by allowing multiple stages of instructions to execute simultaneously.

Detailed Explanation

Pipelining is a technique that allows multiple instruction stages to work at the same time. Imagine you are assembling a product on an assembly line. Each worker is responsible for a specific step in the process. While one worker is assembling a product, another can be preparing the next product. In computing, this means that while one instruction is being decoded, another can be executed, and a third can be fetched from memory. This overlapping increases the number of instructions processed in a given period, enhancing performance.

Examples & Analogies

Think about a restaurant kitchen. While one chef is cooking an entrée, another can be preparing a salad and a third can be setting the table. Each person is working on a different task, but together, they are speeding up the meal preparation process. Similarly, pipelining allows the processor to work on multiple parts of different instructions simultaneously.

Superscalar Architecture

Chapter 2 of 5

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Superscalar Architecture: Superscalar processors have multiple pipelines, allowing them to issue multiple instructions per cycle.

Detailed Explanation

In a superscalar architecture, the processor has multiple pipelines. This means that it can execute several instructions at the same time in a single clock cycle. To visualize this, consider a multi-lane highway where multiple cars can travel side by side. Each car represents an instruction, and just as several cars can move together at once, several instructions can also be processed simultaneously in the processor. This technique maximizes the instruction throughput, enabling a faster processing rate.

Examples & Analogies

Picture a race with multiple runners. If there are only a few lanes, only a limited number of runners can race at once; however, if there are multiple lanes available, many runners can compete simultaneously, speeding up the overall race time. Similarly, superscalar processors allow multiple instructions to run at the same time, improving efficiency.

Dynamic Scheduling

Chapter 3 of 5

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Dynamic Scheduling: Hardware dynamically schedules instructions to execute as soon as the required operands are available, optimizing ILP.

Detailed Explanation

Dynamic scheduling is a process where the hardware manages which instructions to run at any given time based on the availability of the required data (operands). This is similar to organizing tasks at a project worksite where tasks are completed as resources become available rather than waiting for a strict order. In dynamic scheduling, if an instruction is ready to execute but is waiting for prior instructions to finish, the hardware may choose to execute another instruction that can proceed. This flexibility allows for more efficient utilization of processing resources.

Examples & Analogies

Think about a construction site where workers can start on different tasks as soon as materials become available. If a bricklayer is waiting for bricks to arrive, but the plumber has everything needed to install pipes, the plumber will go ahead and start working. In a similar way, dynamic scheduling allows a CPU to adapt to resource availability, leading to smoother instruction execution.

Out-of-Order Execution

Chapter 4 of 5

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Out-of-Order Execution: Instructions are executed as their operands become available, not necessarily in the order they appear in the program, which helps improve ILP.

Detailed Explanation

Out-of-order execution means that instead of executing instructions strictly in the order they are written, the processor executes instructions based on the availability of their operands. This is beneficial because, often, certain instructions can be completed quicker than others, and waiting for earlier instructions can waste processing cycles. This capability allows the processor to optimize its performance by keeping its execution units busy with whatever can be executed next.

Examples & Analogies

Consider a student taking a set of exams. Instead of taking the exams in the order they are scheduled, if one exam is delayed due to a scheduling conflict but another can be taken right away, the student will take the second exam first. This approach ensures that the student maximizes their time and avoids idle waiting. Likewise, out-of-order execution helps the processor make efficient use of its resources.

Register Renaming

Chapter 5 of 5

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Register Renaming: Avoids data hazards by dynamically assigning registers to hold intermediate results, allowing instructions to proceed without waiting for previous instructions to complete.

Detailed Explanation

Register renaming is a technique used to avoid data hazards by assigning different registers for the results of operations dynamically. When instructions depend on each other (for example, one instruction uses the result of a previous instruction), it can lead to delays. Register renaming allows the processor to use different registers for intermediate values instead of waiting for the previous instruction to complete, thus speeding up the instruction execution.

Examples & Analogies

Imagine you are organizing a group project where group members need to present their portions of a project in a specific order. If one member's work isn't ready, the whole project stalls. However, if instead of waiting, other members can share their parts using different versions or copies of their work, the project can continue moving forward. Register renaming allows a CPU to handle instructions more flexibly and efficiently, avoiding unnecessary delays.

Key Concepts

-

Pipelining: A technique to execute multiple instructions simultaneously through overlapping stages.

-

Superscalar Architecture: An architecture allowing multiple instructions per clock cycle using multiple execution units.

-

Dynamic Scheduling: Execution order modification based on operand availability to optimize performance.

-

Out-of-Order Execution: Execution of instructions as data becomes available, increasing parallelism.

-

Register Renaming: Prevents data hazards by dynamically assigning registers for intermediate results.

Examples & Applications

Pipelining can be visualized like an assembly line where different workers handle different parts of a task at the same time.

Dynamic scheduling optimizes the order of instruction execution based on the state of data dependencies.

Memory Aids

Interactive tools to help you remember key concepts

Rhymes

In the pipeline, stages flow, / Faster processors we bestow!

Stories

Imagine a team building a car where one person is welding while another is painting; this is like pipelining, enabling multiple tasks at once.

Memory Tools

PEOD - Remember Pippin's Excellent Out-Door activities: Pipelining, Execution, Out-of-order, Dynamic scheduling.

Acronyms

SPEED - Superscalar Processors Enhance Execution Dynamically.

Flash Cards

Glossary

- Pipelining

A technique that allows multiple stages of instruction execution to occur simultaneously, improving throughput.

- Superscalar Architecture

An architectural design that enables multiple instruction issue per clock cycle by utilizing multiple execution units.

- Dynamic Scheduling

A method that allows the CPU to determine the optimal order of instruction execution based on operand availability.

- OutofOrder Execution

A technique where instructions are executed as their operands become ready, rather than in the original order.

- Register Renaming

A method to allocate different registers for intermediate results to minimize data hazards.

Reference links

Supplementary resources to enhance your learning experience.