Superscalar Processors

Enroll to start learning

You’ve not yet enrolled in this course. Please enroll for free to listen to audio lessons, classroom podcasts and take practice test.

Interactive Audio Lesson

Listen to a student-teacher conversation explaining the topic in a relatable way.

Introduction to Superscalar Processors

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Today we're going to discuss superscalar processors, which are designed to issue multiple instructions per clock cycle. Can anyone tell me what that might mean for performance?

It means they can handle more tasks at the same time, right?

Exactly! More tasks can lead to faster processing times. This is done using multiple pipelines. Can anyone guess what 'issue width' means?

Is it the number of instructions a processor can issue in a cycle?

That's right! The issue width can vary; modern processors can issue 2, 4, or more instructions at once. This is a game-changer for performance!

Challenges in Superscalar Architecture

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Let's discuss the challenges that come with superscalar processors. One major challenge is the dependence on instruction type. Can someone think of an example of an instruction that might be tough to parallelize?

Maybe memory operations, since they can cause delays?

Exactly! Memory operations can slow things down due to access times. What about instruction scheduling, why is that important?

To prevent conflicts and make sure the processor knows which instructions can run together?

Exactly! Dynamic scheduling helps maximize ILP by managing instruction execution order effectively. Can anyone summarize what we learned today?

We learned that superscalar processors can execute multiple instructions at once, but they must handle challenges like instruction dependencies and scheduling.

Introduction & Overview

Read summaries of the section's main ideas at different levels of detail.

Quick Overview

Standard

This section delves into the architecture of superscalar processors and their ability to issue multiple instructions simultaneously. It highlights the concept of issue width and addresses challenges encountered in effectively exploiting ILP.

Detailed

Superscalar Processors

Superscalar processors are a pivotal advancement in CPU architecture aimed at maximizing Instruction-Level Parallelism (ILP). Unlike scalar processors, which issue a single instruction per cycle, superscalar processors can issue and execute several instructions simultaneously due to their multiple execution units and pipelines.

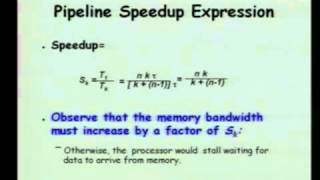

Multiple Pipelines

A key feature of superscalar architecture is the presence of multiple execution pipelines. This allows a processor to handle more than one instruction during each clock cycle, leading to improved performance and throughput. The

Issue Width

The 'issue width' of a processor is a critical metric, referring to the number of instructions that it can issue and/or execute in a single cycle. Modern superscalar processors typically have issue widths of 2, 4, or even more instructions, which allows them to exploit the inherent parallelism in instruction streams.

Challenges in Superscalar Processors

Despite their advantages, superscalar processors face challenges in realizing ILP:

- Dependence on Instruction Type: Certain instructions (especially memory operations or control instructions) may present difficulties in parallel execution.

- Instruction Scheduling: Effective scheduling is crucial; the hardware must dynamically manage the order of instruction execution to avoid resource conflicts and maximize ILP.

In summary, superscalar processors embody a vital approach towards enhancing processor efficiency through ILP exploitation, albeit with certain challenges that require sophisticated handling.

Youtube Videos

Audio Book

Dive deep into the subject with an immersive audiobook experience.

Definition and Purpose of Superscalar Processors

Chapter 1 of 4

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Superscalar processors are designed to exploit ILP by using multiple execution units to issue and execute several instructions per clock cycle.

Detailed Explanation

Superscalar processors enhance processing power by allowing multiple instructions to be executed simultaneously. Unlike traditional scalar processors, which can only execute one instruction at a time, superscalar processors have multiple execution units. This design allows them to issue several instructions within the same clock cycle, effectively increasing the throughput of instructions and improving the performance of executing programs.

Examples & Analogies

Think of a superscalar processor like a busy restaurant with multiple chefs in the kitchen. Instead of just one chef preparing orders sequentially, several chefs can work on different dishes at the same time. This means more meals can be prepared and served to customers in the same amount of time, just as multiple instructions are processed in parallel by a superscalar processor.

Multiple Pipelines and Execution

Chapter 2 of 4

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

● Multiple Pipelines: A superscalar processor has multiple execution pipelines, which allow more than one instruction to be processed per cycle.

Detailed Explanation

The key feature of superscalar processors is their ability to have multiple pipelines. Each pipeline can handle one instruction at a time through various stages of processing like fetching, decoding, executing, and writing back results. This parallelism significantly boosts instruction throughput because while one pipeline is processing an instruction, others can simultaneously handle additional instructions.

Examples & Analogies

Imagine a manufacturing assembly line with multiple conveyor belts. Each belt is responsible for assembling a part of the product—while one belt assembles wheels, another one assembles the engine. This setup ensures that multiple components of a car are manufactured simultaneously, similar to how multiple pipelines in a superscalar processor enable it to process several instructions at once.

Issue Width and Its Importance

Chapter 3 of 4

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

● Issue Width: The number of instructions that can be issued per cycle is called the issue width. Modern processors may have issue widths of 2, 4, or more instructions per cycle.

Detailed Explanation

The issue width is a critical metric for understanding a processor's performance capabilities. It refers to how many instructions can be initiated or executed in one clock cycle. A larger issue width means that a processor can handle more instructions at once, effectively leveraging instruction-level parallelism (ILP) to improve overall efficiency and speed. For instance, a processor with a width of 4 can start four instructions at the same time, significantly enhancing throughput compared to a scalar processor.

Examples & Analogies

Consider a team of builders working on different aspects of a house. If you have a wider team (higher issue width), they can work on the roof, the walls, the plumbing, and the electrical systems all at the same time. This teamwork allows for much faster completion than if only one worker could handle one task at a time.

Challenges Faced by Superscalar Processors

Chapter 4 of 4

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

● Challenges in Superscalar Processors:

○ Dependence on Instruction Type: Some instructions are more difficult to parallelize than others (e.g., memory operations, control instructions).

○ Instruction Scheduling: The hardware must dynamically schedule instructions to avoid resource conflicts and maximize ILP.

Detailed Explanation

Despite their advantages, superscalar processors face challenges in maximizing ILP. One major challenge is the dependence on the type of instruction being executed. Certain operations, like memory accesses or branching instructions, are inherently less parallelizable. Moreover, effective instruction scheduling is necessary to ensure that instructions do not conflict for resources like execution units, which can limit their efficiency. This scheduling must be managed dynamically as the processor executes code, which can add complexity to the design and operation of superscalar processors.

Examples & Analogies

Think of a large project management team planning a construction project. If certain tasks depend on the completion of previous ones, not all workers can proceed at the same time, leading to delays. Moreover, if too many workers are assigned to the same part without coordination, chaos ensues. This is akin to instruction conflicts in a superscalar processor where not all instructions can run in parallel due to dependencies.

Key Concepts

-

Superscalar Processors: Processors that can handle multiple instructions per clock cycle.

-

Issue Width: The number of simultaneous instructions a processor can issue during one cycle.

-

Instruction Scheduling: The dynamic arrangement of instruction execution to optimize performance.

Examples & Applications

In a video game processor, superscalar architecture allows multiple actions (like moving and shooting) to be processed simultaneously, resulting in smoother gameplay.

A CPU that can execute four instructions in a clock cycle can effectively double the throughput compared to one that only issues two.

Memory Aids

Interactive tools to help you remember key concepts

Rhymes

Superscalar might sound bizarre, / But it helps CPUs race, and go far!

Stories

Imagine a factory where workers can handle multiple tasks at once. Some workers focus on assembling parts, while others finish them at the same time. This factory is like a superscalar processor, maximizing output!

Memory Tools

PICS - Pipelining, Issue width, Complexity in scheduling – key concepts of superscalar processors.

Acronyms

SPEE - Superscalar Processors Enable Enhanced Execution.

Flash Cards

Glossary

- Superscalar

A processor architecture that can execute more than one instruction during a single clock cycle.

- Issue Width

The number of instructions a processor can issue in one clock cycle.

- Pipelines

Multiple execution paths in a superscalar processor that allow for parallel instruction execution.

Reference links

Supplementary resources to enhance your learning experience.