Limits to Exploiting ILP

Enroll to start learning

You’ve not yet enrolled in this course. Please enroll for free to listen to audio lessons, classroom podcasts and take practice test.

Interactive Audio Lesson

Listen to a student-teacher conversation explaining the topic in a relatable way.

Instruction Dependency

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Let's begin by talking about instruction dependency. What do we mean when we say that many programs are inherently sequential?

I guess it means that some instructions can't be executed simultaneously because they rely on the result of previous instructions?

Exactly! This kind of dependency can slow down the overall execution. Anyone knows a specific type of dependency that arises from this?

I think it's called 'data dependency,' right?

Correct! To remember this concept, think of 'D' for Data Dependency. This limits ILP because as long as one instruction depends on the output of another, they can't run in parallel. Can someone give an example?

If I have an instruction that adds two numbers and another one that multiplies the result with a third number. The multiplication can't happen until the addition is done.

Great example! So to recap, instruction dependency can severely impact the effectiveness of ILP in enhancing performance.

Memory Latency

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Now, let’s move on to memory latency. Why do you think memory latency poses a challenge for ILP?

Because even if we can execute instructions in parallel, if data isn't ready from memory, we have to wait.

Exactly! The wait for data from memory can cause what we call pipeline stalls. Can anyone tell me how this might affect overall program performance?

The overall performance would drop since some phases of the instruction execution will just be waiting instead of processing.

Exactly! Think of a traffic jam where cars are ready to go, but the road is blocked. So, always remember that high memory latency undermines the potential of ILP.

Control Dependency

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Let’s examine control dependency. What happens when we have branch instructions in our code?

The processor has to decide what path to take in the code, so it can't execute the next instructions until it knows the branch outcome.

Right! This delay can hinder ILP because it disrupts the flow of instruction execution. Can anyone suggest a method to minimize control dependency issues?

Maybe using branch prediction could help?

Exactly, that’s a good strategy! But remember that even with branch prediction, there's still uncertainty involved. So, we have to manage expectations regarding ILP.

Power Consumption

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Lastly, let’s talk about power consumption. Why is this a concern when we aim for high ILP?

Because as we try to execute more instructions in parallel, it can lead to higher power usage.

Correct! And this can be especially problematic for mobile devices and technology where power efficiency is key. Does anyone remember a specific architecture that might struggle with this issue?

I think superscalar architectures can because they're designed to exploit ILP but can consume more power in doing so.

Great point! To remember, think of 'P' for Power Consumption and how it puts a cap on the feasibility of ILP in many applications.

Introduction & Overview

Read summaries of the section's main ideas at different levels of detail.

Quick Overview

Standard

The section examines various factors that limit the exploitation of Instruction-Level Parallelism, including instruction dependencies, memory latency, control dependencies from branch instructions, and issues related to power consumption. These limitations present challenges that must be addressed to effectively utilize ILP.

Detailed

Limits to Exploiting ILP

Despite substantial advancements in the field of Instruction-Level Parallelism (ILP), several inherent limits hinder its full exploitation in modern processors:

- Instruction Dependency: Many programs contain inherent sequential elements that restrict parallelization opportunities. This means that not all types of instructions can be executed simultaneously, leading to potential stalled execution.

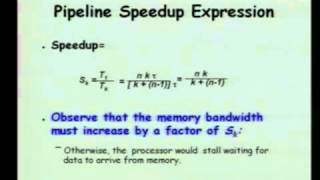

- Memory Latency: While instructions may be capable of running in parallel, they frequently depend on data retrieval from memory. High memory latency can introduce delays, causing pipeline stalls that compromise the efficiency of ILP and ultimately reduce performance.

- Control Dependency: Branch instructions introduce control dependencies, forcing a processor to wait for the outcome of a branch before proceeding with subsequent instruction execution. This can significantly curb the parallelism that can be exploited within a program.

- Power Consumption: Finally, an increase in the levels of ILP utilization—especially with deeper pipelines and superscalar architectures—can lead to increased power consumption. This is a critical challenge for many power-sensitive applications, making high levels of ILP less feasible in certain contexts.

Youtube Videos

Audio Book

Dive deep into the subject with an immersive audiobook experience.

Instruction Dependency

Chapter 1 of 4

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Many programs are inherently sequential and cannot be easily parallelized.

Detailed Explanation

Instruction dependency refers to the fact that some programs need to execute instructions in a specific order. If one instruction depends on the result of another, the first must finish its execution before the second can begin. This situation presents a fundamental limitation to ILP because it prevents multiple instructions from being executed at the same time; a sequence of dependent instructions must be completed one after the other, restricting the potential for parallelism.

Examples & Analogies

Imagine a factory assembly line where workers must perform tasks in a particular order. If Worker A must finish before Worker B can start their job, then Worker B can't start working until Worker A is done, even if there are other tasks that could be done simultaneously. This is similar to how instruction dependency limits parallel execution in programming.

Memory Latency

Chapter 2 of 4

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Even if instructions can be executed in parallel, waiting for data from memory can limit ILP. High memory latency can cause pipeline stalls and reduce overall performance.

Detailed Explanation

Memory latency refers to the delay in accessing data stored in memory. When a processor needs data to execute instructions but has to wait for that data to be retrieved from memory, it can create pauses in execution, known as pipeline stalls. These stalls occur because various parts of the processor may be unable to continue working until the necessary data arrives, thus hindering the exploitation of ILP. Even with the ability to run instructions in parallel, excessive waiting times can significantly diminish performance.

Examples & Analogies

Consider a restaurant kitchen where chefs can't proceed with cooking until ingredients are delivered. If the supplier is slow and doesn't deliver the materials on time, chefs will have to stop and wait, even if they have other dishes they could prepare in the meantime. This waiting reflects how memory latency can stall a processor's pipeline.

Control Dependency

Chapter 3 of 4

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Branch instructions create control dependencies that limit ILP, as the pipeline must wait for the outcome of branches.

Detailed Explanation

Control dependency arises from branch instructions that direct the flow of execution based on certain conditions. When a program encounters a branch, it may have to decide which set of instructions to execute next. If the processor doesn't know the outcome of the branch, it cannot proceed with executing subsequent instructions. This indecision can stall the pipeline, ultimately reducing the potential for simultaneously executing other instructions, thereby imposing another limit on ILP.

Examples & Analogies

Think of a traffic intersection with a stoplight. Cars must wait until the light turns green (the outcome of the control) before they can proceed. If the light is red, they cannot move, even if other cars are waiting to go in different directions. This demonstrates how control dependency can hold up instruction execution in a processor.

Power Consumption

Chapter 4 of 4

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Exploiting higher levels of ILP, especially with deep pipelines or superscalar architectures, can increase power consumption, making it less feasible in power-sensitive applications.

Detailed Explanation

As processors strive to exploit more ILP, they often implement deeper pipelines and superscalar architectures, which can lead to greater power consumption. Each stage in a deep pipeline requires energy, and when multiple instructions are processed simultaneously (as in superscalar CPU designs), the power draws increase. This makes it challenging to implement such technologies in environments where power efficiency is crucial, such as mobile devices or battery-powered systems. Therefore, while advanced architectures can capture higher ILP, they also raise concerns about energy costs, which can limit their practical use.

Examples & Analogies

Consider a high-performance sports car that consumes a lot of fuel to achieve top speed. The faster you want to go (the higher the ILP), the more fuel (power) you need, which might not be practical if you're trying to be economical or environmentally friendly. This analogy reflects the tension between maximizing performance and managing power consumption in modern processors.

Key Concepts

-

Instruction Dependency: The reliance of instructions on each other, limiting their parallel execution.

-

Memory Latency: The time delay in accessing data from memory, leading to potential stalls.

-

Control Dependency: The uncertainty in instruction flow due to branch instructions.

-

Pipeline Stalls: Delays caused by dependencies, hindering performance in parallel execution.

-

Power Consumption: Increased power usage associated with deep pipelines and superscalar architectures.

Examples & Applications

If instruction A produces a result that instruction B needs, instruction B cannot run until A has completed, demonstrating instruction dependency.

In a situation where a program fetches data from a slow memory source, if an instruction waits for this data, it leads to memory latency affecting throughput.

Memory Aids

Interactive tools to help you remember key concepts

Rhymes

When data's slow and can't be fetched, / Our ILP performance gets stretched!

Stories

Imagine a race between runners, one always waiting for a signal from the other. This race represents how instruction dependencies can slow down the overall pace of execution.

Memory Tools

P-M-C-D: Think 'Performance,' 'Memory Latency,' 'Control Dependency,' and 'Pipeline Stalls' — all factors that limit how much we can exploit ILP.

Acronyms

IPC

Instruction

Power

Control. Remember these when considering factors limiting ILP execution.

Flash Cards

Glossary

- Instruction Dependency

A situation where certain instructions cannot be executed simultaneously because one relies on the result of another.

- Memory Latency

The delay between the request for data from memory and the availability of that data for execution.

- Control Dependency

A situation in which the execution of subsequent instructions is contingent on the outcome of branch instructions.

- Pipeline Stalls

Delays in instruction execution caused by various dependencies, causing subsequent instructions to wait.

- Power Consumption

The amount of electrical power used by a processor when executing instructions, which can increase with higher levels of ILP.

Reference links

Supplementary resources to enhance your learning experience.