Data Hazards and ILP

Enroll to start learning

You’ve not yet enrolled in this course. Please enroll for free to listen to audio lessons, classroom podcasts and take practice test.

Interactive Audio Lesson

Listen to a student-teacher conversation explaining the topic in a relatable way.

Understanding Data Hazards

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Today, we're going to talk about data hazards, which can impede Instruction-Level Parallelism. Can anyone tell me what they think a data hazard is?

Is it something that happens when one instruction depends on another?

Exactly! Data hazards occur when instructions are interdependent. There are three main types: RAW, WAR, and WAW. Let's break these down one by one.

What do each of those abbreviations mean?

Great question! RAW stands for Read-After-Write, where an instruction can't read data until it's written. WAR means Write-After-Read, and WAW stands for Write-After-Write. Can anyone give me an example?

For RAW, if instruction one writes to a register and instruction two tries to read from it before it's updated?

Exactly right! Excellent example. Let's summarize—data hazards are critical to understanding how processors can execute instructions concurrently.

Hazard Resolution Techniques

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Now, let's explore how we resolve these hazards. Can anyone think of a technique that can help?

Maybe forwarding?

Exactly! Forwarding, or data bypassing, sends data directly from one pipeline stage to another. What happens if forwarding isn’t possible?

Then you would have to stall the pipeline, right?

Correct! Introducing stall cycles means delaying the dependent instruction until the hazard is resolved. What else can we do to deal with hazards like WAR and WAW?

Register renaming could help by giving each instruction its own register!

Exactly! Register renaming prevents conflicts by using additional registers. To summarize: we can use forwarding, stall cycles, or register renaming to handle data hazards effectively.

Introduction & Overview

Read summaries of the section's main ideas at different levels of detail.

Quick Overview

Standard

The section covers various types of data hazards, including Read-After-Write (RAW), Write-After-Read (WAR), and Write-After-Write (WAW). It explains how these hazards can affect instruction execution and details hazard resolution techniques like forwarding, stall cycles, and register renaming to mitigate their impact on ILP.

Detailed

Data Hazards and Instruction-Level Parallelism (ILP)

In the pursuit of maximizing Instruction-Level Parallelism (ILP), data hazards present significant challenges. Data hazards occur when the execution of instructions is interrupted because they depend on the results of prior instructions. This can hinder the processor's ability to execute multiple instructions simultaneously, ultimately affecting performance.

Types of Data Hazards

- RAW (Read-After-Write): This hazard arises when an instruction attempts to read a register before another instruction has updated it.

- WAR (Write-After-Read): This occurs when an instruction attempts to write to a register before another instruction has read from it.

- WAW (Write-After-Write): This happens when two instructions try to write to the same register in a conflicting order.

Hazard Resolution Techniques

To counter these hazards, various techniques have been developed:

- Forwarding (Data Bypassing): This method allows data from one pipeline stage to be sent directly to another stage, eliminating the need to write it back to the register file first.

- Stall Cycles: When forwarding isn’t possible, the processor introduces a stall, deferring the execution of dependent instructions until the hazard is cleared.

- Register Renaming: This technique dynamically allocates additional registers to resolve WAR and WAW hazards, allowing the execution of instructions without dependencies causing conflicts.

Understanding these concepts is essential for any study of modern processors that exploit ILP effectively.

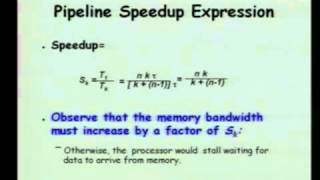

Youtube Videos

Audio Book

Dive deep into the subject with an immersive audiobook experience.

Understanding Data Hazards

Chapter 1 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

To efficiently exploit ILP, data hazards need to be addressed. Data hazards occur when instructions depend on the results of previous instructions.

Detailed Explanation

Data hazards are situations in computer programming where one instruction relies on the result of another instruction. This dependence can create a problem for processors trying to execute multiple instructions simultaneously, as they might start executing without having the needed data available. To effectively utilize instruction-level parallelism (ILP), we need to identify and manage these hazards.

Examples & Analogies

Think of a relay race where one runner can only start once the previous runner has passed the baton. If the next runner starts too soon, they won't have the baton and will be unable to continue, just as a computer can't proceed with an instruction without the right data.

Types of Data Hazards

Chapter 2 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

● Types of Data Hazards:

○ RAW (Read-After-Write): Occurs when an instruction tries to read a register before the previous instruction writes to it.

○ WAR (Write-After-Read): Occurs when an instruction tries to write to a register before another instruction reads it.

○ WAW (Write-After-Write): Occurs when two instructions try to write to the same register in the wrong order.

Detailed Explanation

There are three primary types of data hazards that can occur:

1. RAW (Read-After-Write): This happens when an instruction needs to read data that hasn't been written yet, causing a delay.

2. WAR (Write-After-Read): This occurs if an instruction writes to a data location before another instruction has had the chance to read it.

3. WAW (Write-After-Write): This happens when two instructions attempt to write to the same location, and the order of writing matters.

Examples & Analogies

Imagine a kitchen where you need to prepare a dish. If one chef is instructed to add salt before another chef has tasted the dish, you could end up with an overly salty meal (RAW). If the second chef tries to taste the dish after being told to add salt but hasn't yet tasted it, they won't know how much salt's already there (WAR). Finally, if two chefs try to season the dish simultaneously without knowing who did what first, the outcome could be confusing and inconsistent (WAW).

Hazard Resolution Techniques

Chapter 3 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

● Hazard Resolution Techniques:

○ Forwarding (Data Bypassing): Data from one pipeline stage is sent directly to another stage without waiting for it to be written to the register file.

○ Stall Cycles: When forwarding is not possible, a stall is introduced to delay the dependent instruction until the hazard is resolved.

○ Register Renaming: Used to eliminate WAR and WAW hazards by dynamically allocating new registers.

Detailed Explanation

To manage data hazards, several techniques can be employed:

1. Forwarding: This method allows a processor to send the data directly from one stage of execution to another without waiting to write it back into memory first.

2. Stall Cycles: If forwarding isn't possible, the processor may pause (stall) the dependent instruction, waiting for the needed data to be ready.

3. Register Renaming: This technique involves using different registers to avoid conflicts from WAR and WAW situations. By dynamically allocating new registers, instructions can execute without waiting.

Examples & Analogies

Consider a school where students must wait for one teacher to finish a lesson before another teacher can start with information that builds on it. Forwarding would be like allowing the second teacher to use the notes directly from the first teacher before they are officially recorded. Stall cycles are like postponing the second lesson until the first one is completely finished. Register renaming is akin to giving each student their own notebook instead of trying to share one, preventing the mix-up of notes.

Key Concepts

-

Data Hazard: A situation that prevents concurrent instruction execution due to dependencies.

-

RAW: A hazard that occurs when an instruction reads before a write is completed.

-

WAR: A hazard where an instruction writes before another has read.

-

WAW: A conflict where two writes happen in the wrong order.

-

Forwarding: A method to directly transmit data between pipeline stages.

-

Stall Cycle: A delay intentionally introduced in the pipeline to resolve dependencies.

-

Register Renaming: A technique used to manage and avoid write conflicts.

Examples & Applications

For a RAW hazard, consider instruction 1 that writes to register R1, followed by instruction 2 attempting to read from R1 before instruction 1 has completed.

An example of a WAR hazard could be instruction 1 reading register R2, while instruction 2 tries to write to R2 before instruction 1's read is finished.

Memory Aids

Interactive tools to help you remember key concepts

Rhymes

If you write then read in the wrong order you see, that's RAW, oh me, oh my, it's a data hazard that mustn't be!

Stories

Imagine two clueless programmers battling over the same variable. If one writes before the other reads, chaos ensues! Prevent this by managing their order!

Memory Tools

R-War-Waw: Remember 'Real Write' comes first, ‘Write’ before you ‘Read’, and ‘Wordwise’ order matters!

Acronyms

FW = Forwarding Wins – Recall that forwarding helps eliminate delays from hazards.

Flash Cards

Glossary

- Data Hazard

A situation in which instructions fail to execute correctly due to dependencies on the results of previous instructions.

- RAW (ReadAfterWrite)

A type of data hazard that occurs when an instruction attempts to read a register before it has been updated by a preceding instruction.

- WAR (WriteAfterRead)

A type of data hazard that occurs when an instruction attempts to write to a register before it has been read by a preceding instruction.

- WAW (WriteAfterWrite)

A type of data hazard that occurs when two instructions attempt to write to the same register in conflicting orders.

- Forwarding

A method of resolving data hazards by sending data directly from one pipeline stage to another.

- Stall Cycle

A delay introduced in the instruction pipeline to resolve data hazards.

- Register Renaming

A technique that eliminates WAR and WAW hazards by dynamically allocating new registers.

Reference links

Supplementary resources to enhance your learning experience.