Case Study: ILP in Modern Processors

Enroll to start learning

You’ve not yet enrolled in this course. Please enroll for free to listen to audio lessons, classroom podcasts and take practice test.

Interactive Audio Lesson

Listen to a student-teacher conversation explaining the topic in a relatable way.

Intel's Superscalar Architecture

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Today we're talking about how Intel utilizes Instruction-Level Parallelism in its processors, particularly through its superscalar architecture.

What exactly is a superscalar architecture?

Great question! In a superscalar architecture, a processor can issue multiple instructions per clock cycle, which is a key feature that allows for better utilization of available execution units.

And how does this help with performance?

By issuing multiple instructions at once, the processor can complete tasks faster, reducing overall execution time. You can think of it as having several workers in a warehouse, all completing different tasks simultaneously.

What about hyper-threading? How does that fit in?

Hyper-threading allows multiple threads to be handled by each core, effectively turning one physical core into two logical units. This further increases the parallelism and resource utilization.

So, it's like having two workers sharing the same toolbox?

Exactly! It maximizes productivity without physical expansion of resources. Overall, Intel's architecture showcases a significant advancement in leveraging ILP.

ARM's ILP Implementation

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Now, let’s discuss how ARM processors implement ILP and why energy efficiency is a major focus for them.

I’ve heard ARM is known for their battery efficiency. How does that relate to ILP?

That's correct! ARM designs prioritize minimal power consumption, and they achieve this through dynamic scheduling and out-of-order execution.

What’s dynamic scheduling?

Dynamic scheduling allows the processor to decide the order of instructions based on operand availability rather than a strict sequence. This means that if certain data is ready to be processed, ARM can execute those instructions immediately, improving efficiency.

And out-of-order execution?

Out-of-order execution means that instructions can be processed as their operands become available, providing even more flexibility. This helps ARM sustain high performance levels while still being energy efficient.

So, they balance power and performance?

Precisely! ARM’s method exemplifies how effective ILP implementation can lead to powerful and efficient processors.

Introduction & Overview

Read summaries of the section's main ideas at different levels of detail.

Quick Overview

Standard

The section provides an overview of how modern processors like Intel and ARM leverage ILP through various architectural features, including Intel's superscalar design and hyper-threading, and ARM's focus on energy efficiency and dynamic scheduling, thereby optimizing performance and efficiency in executing instructions.

Detailed

Case Study: ILP in Modern Processors

In this section, we explore the implementation of Instruction-Level Parallelism (ILP) in contemporary processors from leading manufacturers like Intel and ARM.

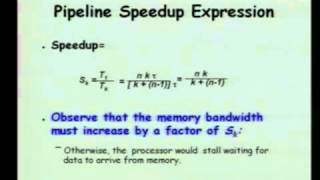

- Intel's Superscalar Architecture: Intel processors utilize a superscalar architecture that allows multiple instructions to be issued and executed within the same clock cycle. This architecture is enhanced by hyper-threading technology, which enables several threads to run concurrently on each core. This combination facilitates a significant increase in processing power without needing to increase the clock speed, leading to improved throughput and reduced execution times.

- ARM's ILP Practices: ARM processors adopt a different approach by focusing on energy efficiency alongside their performance. ILP is engaged through dynamic scheduling and out-of-order execution methods. These practices allow ARM processors to maintain high performance while managing power consumption effectively. By optimizing when instructions are executed based on operand availability, ARM maximizes performance without compromising energy efficiency.

The insights gathered from these implementations illustrate the innovative uses of ILP in modern computing, showing a shift towards more efficient and powerful processing units.

Youtube Videos

Audio Book

Dive deep into the subject with an immersive audiobook experience.

Intel’s Superscalar and Hyper-Threading

Chapter 1 of 2

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Intel processors use superscalar architecture to issue multiple instructions per cycle and hyper-threading to run multiple threads concurrently on each core.

Detailed Explanation

Intel's processors take advantage of Instruction-Level Parallelism (ILP) through two main technologies: superscalar architecture and hyper-threading. Superscalar architecture enables the processor to issue and execute multiple instructions at once during each clock cycle, enhancing performance without requiring higher clock speeds. Hyper-threading allows a single processor core to simulate two separate threads by scheduling tasks from both threads simultaneously, effectively improving the utilization of processor resources and increasing overall performance. This combined approach helps Intel processors increase throughput and responsiveness.

Examples & Analogies

Think of Intel's approach like a restaurant with multiple cooks (cores) working at the same time, each preparing several dishes (instructions) concurrently. Additionally, it's as if two cooks (threads) can share the same cooking space, allowing faster service (processing) without needing to build more kitchens (cores) for each task.

ARM’s ILP Implementation

Chapter 2 of 2

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

ARM processors implement ILP through dynamic scheduling and out-of-order execution, focusing on energy efficiency while maintaining high performance.

Detailed Explanation

ARM processors utilize two advanced techniques to implement ILP: dynamic scheduling and out-of-order execution. Dynamic scheduling allows the processor to rearrange the order of instruction execution based on the availability of data, enabling instructions to proceed as soon as their operands are ready. This flexibility helps optimize the instruction pipeline. Out-of-order execution improves performance further by allowing instructions that do not depend on each other to be executed in any order, rather than strictly following their original sequence. ARM emphasizes energy efficiency through these techniques, making their processors particularly suited for mobile and embedded devices.

Examples & Analogies

Imagine a library where patrons (instructions) are allowed to read books (data) as soon as they arrive, rather than waiting in line for a specific book. Dynamic scheduling is like rearranging the reading order to make sure everyone reads promptly without delay. Out-of-order execution is akin to letting capable readers grab books that interest them, regardless of when their reservation says they should pick them up. This approach helps the library (processor) operate smoothly and quickly while using fewer resources.

Key Concepts

-

Superscalar Architecture: Allows multiple instructions to be issued per clock cycle enhancing performance.

-

Hyper-Threading: Intel's method for improving throughput by running multiple threads per core.

-

Dynamic Scheduling: Helps instruction execution order to be optimized based on operand availability.

-

Out-of-Order Execution: Improves efficiency by executing instructions as soon as resources become available.

Examples & Applications

In Intel's processors, the ability to issue four instructions in one clock cycle allows for rapid processing of complex applications.

ARM's approach to dynamic scheduling can lead to executing instructions even when they are not in the original program order, improving overall performance.

Memory Aids

Interactive tools to help you remember key concepts

Rhymes

In processors sleek and fast, ILP's power unsurpassed; executing many near, speeding up our gear!

Stories

Imagine a factory where numerous tasks can be done at once. Each worker represents an instruction, and by organizing them better, they finish the work quicker—this is how ILP functions in modern processors.

Memory Tools

SHEEP: Superscalar, Hyper-threading, Energy-efficient, Execution, Performance.

Acronyms

SIPED - Superscalar Instruction Parallel Execution Dynamic, representing techniques used in modern processors.

Flash Cards

Glossary

- InstructionLevel Parallelism (ILP)

The ability of a processor to execute multiple instructions simultaneously by exploiting the parallelism inherent in instruction streams.

- Superscalar Architecture

A processor design that allows multiple instructions to be issued per clock cycle, increasing instruction throughput.

- HyperThreading

Intel's technology that allows multiple threads to be executed simultaneously on a single physical core.

- Dynamic Scheduling

A technique that allows the CPU to select the order of instruction execution based on operand availability rather than a fixed sequence.

- OutofOrder Execution

A method allowing instructions to be executed as soon as their operands are available, rather than strictly in the order they appear.

Reference links

Supplementary resources to enhance your learning experience.