Control Hazards and ILP

Enroll to start learning

You’ve not yet enrolled in this course. Please enroll for free to listen to audio lessons, classroom podcasts and take practice test.

Interactive Audio Lesson

Listen to a student-teacher conversation explaining the topic in a relatable way.

Control Hazards

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Isn't it when a processor has to wait because it doesn't know the next instruction due to a branch?

If there's an 'if' statement in the code, the processor needs to know if it's 'true' or 'false' to decide which instruction to fetch next?

Right, and while it's waiting for this decision, no new instructions can be executed. This is what hinders our ability to exploit ILP effectively.

Summary of Concepts

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Branch prediction, BTB, and delayed branching!

I think understanding these concepts really helps see how processors boost performance!

Exactly! Great job, everyone!

Introduction & Overview

Read summaries of the section's main ideas at different levels of detail.

Quick Overview

Standard

Control hazards, primarily resulting from branch instructions, can stall pipelined processors by making it difficult to predict the next instruction to execute. This section discusses strategies such as branch prediction, the use of a Branch Target Buffer (BTB), and delayed branching to minimize the negative impact of control hazards on ILP, thereby enhancing processor efficiency.

Detailed

Control Hazards and ILP

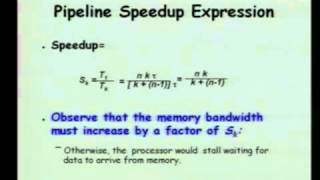

Control hazards are a significant concern in the realm of Instruction-Level Parallelism (ILP) because they arise from conditional branch instructions that can disrupt the instruction fetching process within a pipelined architecture. When a branch instruction is encountered, it may not be immediately clear which instruction to fetch next, resulting in a stall in the pipeline.

Understanding Control Hazards

Control hazards become problematic when the processor continues to fetch instructions irrespective of whether the branch will be taken. If a misprediction occurs, it can lead to wasted cycles and decreased performance.

Mitigation Strategies

- Branch Prediction: This technique anticipates the direction of the branch to help the processor continue executing instructions without waiting for confirmation of the branch outcome. Accurate prediction is essential for maintaining ILP efficiency.

- Branch Target Buffer (BTB): This caching system helps store the target addresses of branches, allowing the processor to fetch instructions ahead of the branch decision, thereby continuing to fill the pipeline with useful work even in the face of potential control hazards.

- Delayed Branching: In delayed branching, instructions are rearranged so that useful work can be performed in the slot immediately following a branch. This helps minimize the performance penalty associated with mispredicted branches.

These strategies collectively enhance the pipeline efficiency and allow for better exploitation of ILP by reducing the stalls and delays brought about by control hazards.

Youtube Videos

Audio Book

Dive deep into the subject with an immersive audiobook experience.

Understanding Control Hazards

Chapter 1 of 4

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Control hazards, caused by branch instructions, can prevent ILP exploitation, as the pipeline needs to know the branch direction before continuing execution.

Detailed Explanation

Control hazards occur when the processor encounters branch instructions that change the flow of execution based on specific conditions. When the processor needs to decide which instruction to execute next (whether to follow a branch or not), it requires additional information about the branch direction. If this information is not known in advance, it can disrupt the smooth flow of instruction execution, thus limiting the ability to take full advantage of parallel instruction execution - a key benefit of instruction-level parallelism (ILP).

Examples & Analogies

Imagine a driver at a fork in the road. If they don’t know whether to go left or right, they might have to stop and think, slowing down traffic behind them. Similarly, if a processor faces a branch instruction and isn’t sure where to go next, it could halt instruction processing until it makes a decision.

Branch Prediction

Chapter 2 of 4

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Accurate branch prediction helps avoid control hazards by guessing the outcome of branches and continuing execution based on the prediction.

Detailed Explanation

Branch prediction is a technique used to enhance the efficiency of instruction execution by making educated guesses about the outcome of branch instructions. When the processor predicts the direction of a branch correctly, it can continue fetching and executing subsequent instructions without waiting for the actual branch outcome. This minimizes delays, thus allowing for better utilization of the CPU and improved performance.

Examples & Analogies

Think of a coach observing runners and predicting which runner will take the lead in a race. By anticipating the runner’s decision, the coach can prepare strategies in advance. Similarly, processors use branch prediction to anticipate where the execution flow will go next, ideally reducing the need to stop and wait.

Branch Target Buffer (BTB)

Chapter 3 of 4

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

A cache used to store the target addresses of branches, helping the processor continue fetching instructions while waiting for the branch decision.

Detailed Explanation

A Branch Target Buffer (BTB) is a specialized cache that stores the destination addresses of branch instructions. When a branch instruction is encountered, the processor can quickly access the BTB to find out where to continue executing instructions. This capability allows it to continue fetching instructions without having to wait for the outcome of the branch decision itself, thus mitigating control hazards and enhancing performance.

Examples & Analogies

Imagine a traffic navigator who remembers common routes for a city's intersections. Instead of needing to analyze all conditions at each intersection every time, the navigator quickly pulls up known routes, making travel smoother and faster. The BTB serves a similar purpose by storing known branch targets for quick reference.

Delayed Branching

Chapter 4 of 4

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

By rearranging instructions, processors can fill delay slots after a branch to minimize the penalty of branch mispredictions.

Detailed Explanation

Delayed branching is a technique where the processor rearranges the execution order of instructions, particularly those following a branch instruction. By filling what are known as 'delay slots' with useful work, the processor is less impacted by mispredictions. If the branch is taken, the rearranged instructions will execute without impacting performance. If the branch is not taken, the processor still benefits from executing other instructions rather than stalling.

Examples & Analogies

Think of a waiter who has to pause at a busy restaurant to decide on the next order. Instead of just standing still, the waiter takes the opportunity to serve drinks or clear tables while waiting to confirm the next action. This keeps the flow of work uninterrupted, similar to how delayed branching keeps instruction flow steady.