VHDL Basic Structure

Enroll to start learning

You’ve not yet enrolled in this course. Please enroll for free to listen to audio lessons, classroom podcasts and take practice test.

Interactive Audio Lesson

Listen to a student-teacher conversation explaining the topic in a relatable way.

Understanding Entity

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Let's start by discussing the Entity in a VHDL program. The Entity defines the interface to the circuit, detailing all the input and output ports. Can anyone give me an example of what an entity might look like?

Would it be something like defining an `AND_GATE`?

Exactly! The Entity for an AND_GATE might look like this: `ENTITY AND_GATE IS PORT ( A : IN BIT; B : IN BIT; Y : OUT BIT ); END ENTITY;`. What do we understand by 'IN' and 'OUT' here?

IN means the signal is coming into the entity, while OUT means it's an output signal from the entity.

Correct! IN ports receive signals, and OUT ports send signals out. Remember it as I-O for input-output. Now, why is defining the Entity important?

It sets the stage for how the circuit interacts with other components.

Right! So, to summarize this session: the Entity defines the interface, listing Input and Output ports essential for circuit functionality.

Exploring Architecture

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Next, we delve into the Architecture. This is where the internal behavior of the circuit is defined. Could someone explain how this might look for the `AND_GATE`?

It would describe how the outputs are generated based on the inputs, right?

"Yes! The architecture specifies internal operations. For instance:

Learning Configuration

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Lastly, let’s discuss Configuration. This part is optional but allows binding an entity to a specific architecture. Why do you think this flexibility is important?

It lets us use various architectures with the same entity, making designs modular.

Exactly! This capability enables reuse and adaptability in circuit design. While we often focus on Entity and Architecture, remember that a good design can utilize configurations effectively to enhance modularity. So how would you summarize these three parts?

They define how the circuit interfaces with others, how it processes inputs, and allows for architectural flexibility!

Correct! The Entity defines the interface, the Architecture describes behavior, and the Configuration links them. Excellent work, everyone!

Introduction & Overview

Read summaries of the section's main ideas at different levels of detail.

Quick Overview

Standard

This section delves into the essential components of a VHDL program, specifically the Entity, which defines interfaces; the Architecture, which outlines circuit operations; and optional Configuration, which binds entities to architectures, providing a foundational understanding for digital circuit design using VHDL.

Detailed

VHDL Basic Structure

This section discusses the core components that form the basic structure of any VHDL program. A typical VHDL program consists of three primary parts:

- Entity: Determines the interface of the circuit. It specifies the various input and output ports needed for the component to interact with other components in a design. For example, an

AND_GATEentity defines two input ports, A and B, and one output port Y.

- Architecture: Details the internal workings of the circuit. This part describes how the inputs are manipulated to produce the desired outputs. The architecture defines the behavior of the circuit as illustrated in the following example:

- Configuration: This optional section links an entity to a specific architecture, allowing for flexibility and modular design.

Understanding this basic structure is crucial in developing and simulating digital circuits using VHDL, forming the basis for advancing towards more complex designs.

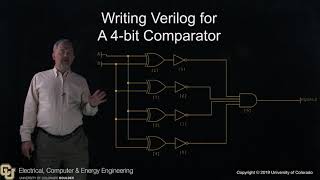

Youtube Videos

Audio Book

Dive deep into the subject with an immersive audiobook experience.

Entity: Defining Circuit Interfaces

Chapter 1 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

A typical VHDL program consists of three key parts:

1. Entity: The entity defines the interface to the circuit, specifying the input and output ports.

Example:

ENTITY AND_GATE IS PORT ( A : IN BIT; B : IN BIT; Y : OUT BIT ); END ENTITY;

Detailed Explanation

In a VHDL program, the entity acts as a blueprint for the circuit's interface. It defines what inputs and outputs the circuit will have. In the example provided, we have an AND gate that takes two inputs (A and B) and produces one output (Y). The inputs are specified as 'IN BIT', meaning they will receive data, while the output 'OUT BIT' signifies that it will send out data after processing the inputs.

Examples & Analogies

Think of the entity as the front door of a house. It tells visitors what they can expect on entering and what they can give or receive, similarly to how the entity describes the inputs (visitors) and outputs (the result of their interactions) of a circuit.

Architecture: The Internal Logic

Chapter 2 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

- Architecture: The architecture describes the internal workings of the circuit. It defines how the inputs are processed to produce the outputs.

Example:

ARCHITECTURE behavior OF AND_GATE IS BEGIN Y <= A AND B; END ARCHITECTURE;

Detailed Explanation

The architecture section details how the circuit functions internally. This is where the actual logic of processing the inputs to produce outputs is described. In the example, the architecture of the AND gate illustrates that the output Y will be the result of the logical AND operation on inputs A and B. This means if both A and B are true (or 1), then the output Y will also be true (or 1).

Examples & Analogies

Imagine the architecture as the layout of a restaurant's kitchen. Just as a kitchen's design dictates how chefs prepare food (inputs being the ingredients and outputs the dishes served), the architecture describes how data moves and changes within the circuit to deliver a result.

Configuration: Binding Entities to Architectures

Chapter 3 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

- Configuration: This part binds an entity to a specific architecture and is optional in most cases.

Detailed Explanation

Configuration in VHDL is used to link an entity with an architecture, indicating which architecture to use for a given entity. This step is often optional because in many cases, there is a direct and default association between an entity and an architecture. However, configurations become particularly useful when using the same entity with different architectures in different parts of a design.

Examples & Analogies

Think of configuration like a menu at a restaurant that lets patrons choose from various meals. Just as a diner may want to pair a specific dish (entity) with various sides (architectures), a designer can select different architectural approaches to implement the same functionality in VHDL.

Key Concepts

-

Entity: Defines the inputs and outputs of a circuit in VHDL.

-

Architecture: Details how inputs are processed internally.

-

Configuration: Optionally binds entities to architectures, enhancing modularity.

Examples & Applications

An AND_GATE entity specifying two input ports (A, B) and an output port (Y).

An architecture detailing the internal operation with the assignment statement Y <= A AND B.

Memory Aids

Interactive tools to help you remember key concepts

Rhymes

Entity sets the stage, define inputs, and outputs are all the rage.

Stories

Imagine a conductor (Entity) leading an orchestra (Architecture), guiding all instruments (internals) to play their parts in harmony.

Memory Tools

Remember 'EAC' - Entity, Architecture, Configuration - the core parts of VHDL.

Acronyms

Use 'EAC' to recall

Entity (interface)

Architecture (behavior)

Configuration (links).

Flash Cards

Glossary

- Entity

The part of a VHDL program that defines the interface to a circuit, outlining its input and output ports.

- Architecture

This describes the internal workings of a digital circuit in VHDL, detailing how inputs are processed to produce outputs.

- Configuration

An optional section in VHDL that links an entity with a specific architecture, facilitating modular design.

Reference links

Supplementary resources to enhance your learning experience.