VHDL Programming Language

Enroll to start learning

You’ve not yet enrolled in this course. Please enroll for free to listen to audio lessons, classroom podcasts and take practice test.

Interactive Audio Lesson

Listen to a student-teacher conversation explaining the topic in a relatable way.

Introduction to VHDL

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Welcome class! Today, we're diving into VHDL, which stands for VHSIC Hardware Description Language. Can anyone tell me why VHDL is significant in digital design?

Isn't it used for modeling digital circuits?

Exactly! It allows us to describe the behavior and structure of digital circuits. VHDL was developed for the U.S. Department of Defense, making it quite sophisticated.

What does 'strongly typed' mean?

Great question! In a strongly typed language like VHDL, you must declare the data types of signals, preventing type errors during compilation. Remember, 'Typed means defined!'

In summary, VHDL is crucial for digital designs, especially on FPGAs.

Basic Structure of VHDL

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Now let's delve into the basic structure of a VHDL program. Can anyone name the three key parts?

I think it's the entity, architecture, and configuration!

Correct! The **entity** defines the interface. A quick memory tip: 'Entity = External Interface.' Let's look at a quick example of an AND gate.

Can you show us?

"Certainly! Here’s a basic entity definition:

Data Types and Operators

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

We’ve covered structure; now, let’s discuss data types and operators. Who can list some data types in VHDL?

How about BIT and INTEGER?

Great! VHDL supports BIT, INTEGER, BOOLEAN, SIGNED, and UNSIGNED. Remember this mnemonic: 'BIS B-U-S' for BIT, INTEGER, SIGNED, BOOLEAN, UNSIGNED.

And what about operators?

We have logical operators like AND, OR; arithmetic operators like +, -, and relational operators like =, <, >. It's important to be familiar with these as they define circuit behavior.

In summary, we have vital data types and operators that allow for rich circuit modeling.

Example: Simple AND Gate

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Let’s apply what we've learned with a practical example—the simple AND gate. Can someone explain what an AND gate does?

It outputs true only if both inputs are true!

"Exactly! Here’s how we model it in VHDL:

Introduction & Overview

Read summaries of the section's main ideas at different levels of detail.

Quick Overview

Standard

The section introduces VHDL, detailing its basic structure, including entities, architectures, and configurations. It also discusses data types, operators, and provides an example of a simple AND gate implementation.

Detailed

VHDL Programming Language

VHDL (VHSIC Hardware Description Language) is an essential tool for modeling digital circuits, particularly in FPGA programming. Initially developed for the U.S. Department of Defense, VHDL has become a standard HDL used to design complex digital systems. Known for its strong typing and verbosity, VHDL excels in simulation-driven designs and offers a high level of abstraction.

Key Components of VHDL

A typical VHDL program is structured into three main elements:

1. Entity: Defines the input and output interface. For example:

- Architecture: Describes the internal workings, such as how inputs are processed, illustrated as follows:

- Configuration: Binds the entity to a specific architecture; it is optional in many cases.

VHDL Data Types and Operators

VHDL supports various data types including BIT, INTEGER, BOOLEAN, SIGNED, and UNSIGNED. It also features multiple operators for logical, arithmetic, and relational operations.

Example: Simple AND Gate

An example using VHDL to model a simple AND gate is provided:

This example highlights the process of defining inputs A and B, alongside an output Y, with a simple internal logic implementation.

In summary, VHDL serves as a foundational language for defining and implementing digital systems, enabling designers to effectively describe complex architectures.

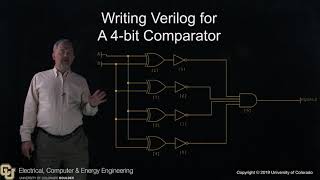

Youtube Videos

Audio Book

Dive deep into the subject with an immersive audiobook experience.

Introduction to VHDL

Chapter 1 of 4

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

VHDL is a strongly typed, verbose language used to model the behavior of digital circuits. It was originally developed for the U.S. Department of Defense’s VHSIC (Very High-Speed Integrated Circuit) program and has since become the standard HDL for designing complex digital systems. VHDL is known for its high level of abstraction and strong support for simulation and testing.

Detailed Explanation

VHDL, or VHSIC Hardware Description Language, is designed specifically for the modeling of digital circuit behavior. Being a 'strongly typed' language means that the data types used must be explicitly declared, reducing programming errors. Its verbosity allows for comprehensive descriptions of functions but can make writing code more extensive compared to other programming languages. Originating from a U.S. military program, it has become the go-to language in the industry for developing complex digital circuits. A highlight of VHDL is its capability to effectively simulate and test the behaviors of circuits before they are built, ensuring reliability in designs.

Examples & Analogies

Think of VHDL as a detailed blueprint for constructing a building. Just like a blueprint provides explicit details on dimensions and materials, VHDL precisely specifies the functions and connections of digital circuits, allowing engineers to visualize the final product before any physical work begins.

VHDL Basic Structure

Chapter 2 of 4

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

A typical VHDL program consists of three key parts:

1. Entity: The entity defines the interface to the circuit, specifying the input and output ports.

Example:

ENTITY AND_GATE IS

PORT (

A : IN BIT;

B : IN BIT;

Y : OUT BIT

);

END ENTITY;

2. Architecture: The architecture describes the internal workings of the circuit. It defines how the inputs are processed to produce the outputs.

Example:

ARCHITECTURE behavior OF AND_GATE IS

BEGIN

Y <= A AND B;

END ARCHITECTURE;

3. Configuration: This part binds an entity to a specific architecture and is optional in most cases.

Detailed Explanation

A typical VHDL program is structured in three main components: 1) The Entity, which acts like a public interface where you define what goes into and comes out of your circuit. 2) The Architecture, which explains how those inputs (data) are utilized to get the desired outputs, essentially detailing the 'logic' of the circuit. In our example of an AND gate, it shows how two inputs are processed to yield the output. 3) The Configuration, which is less commonly used, this defines how different entities and architectures link together, though in many situations, important configurations can be clarified through the entity and architecture themselves.

Examples & Analogies

Consider a recipe as an analogy for this structure. The Entity is like the title of the recipe and the list of ingredients (inputs), while the Architecture is the step-by-step instructions on how to combine those ingredients to create the meal (outputs). The Configuration is similar to choosing which recipe version to follow if there are multiple variants available.

VHDL Data Types and Operators

Chapter 3 of 4

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

● Data Types: VHDL supports several data types, including BIT, INTEGER, BOOLEAN, SIGNED, and UNSIGNED.

● Operators: VHDL supports a range of operators such as logical (AND, OR), arithmetic (+, -, *), and relational (=, <, >) operators.

Detailed Explanation

VHDL offers a rich set of data types which cater to different requirements in digital circuit design. Data types like BIT are used for binary data, INTEGER is for whole numbers, BOOLEAN is for true/false states, while SIGNED and UNSIGNED are specifically used for representing numeric values with and without a sign, respectively. Moreover, VHDL provides operators that allow users to perform operations on these data types. Logical operators like AND and OR are essential for controlling circuit logic, arithmetic operators manage numerical computations, and relational operators help in comparing values.

Examples & Analogies

Think of data types as different tools in a toolbox. Just as you'd select a hammer for nails and a screwdriver for screws, you'd choose BIT for binary signals and INTEGER for counting. Similarly, operators are akin to the actions you can perform with your tools—hammering, screwing, or measuring, facilitating the creation and manipulation of your digital design.

Example: Simple AND Gate

Chapter 4 of 4

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

ENTITY AND_GATE IS

PORT (

A : IN STD_LOGIC;

B : IN STD_LOGIC;

Y : OUT STD_LOGIC

);

END ENTITY AND_GATE;

ARCHITECTURE behavior OF AND_GATE IS

BEGIN

Y <= A AND B;

END ARCHITECTURE behavior;

Detailed Explanation

This VHDL code illustrates a simple design for an AND gate. It starts by including a library (ieee) that contains standard logic types, ensuring compatibility and reliability. The ENTITY section defines the interface of the AND_GATE, specifying two input ports (A and B) and one output port (Y). The ARCHITECTURE section then reveals how the input values are processed—here, the output Y is the logical AND of inputs A and B. This example demonstrates how VHDL clearly expresses the function of a circuit in a structured manner, following the established program structure.

Examples & Analogies

Imagine constructing a simple electronic device that requires a switch (the AND gate). Just like following a clear instruction manual that tells you how to connect your input sources (A and B) to the switch to produce an output (Y), this VHDL code serves as the instruction manual for the AND gate circuit, dictating how to effectively manage the signals involved.

Key Concepts

-

Strongly Typed: VHDL checks variable types strictly, preventing type mismatch errors during compilation.

-

Entity: The building block of a VHDL design, defining input and output interfaces.

-

Architecture: The logical structure for how the entity's inputs are processed to produce outputs.

-

Data Types: Different types of data VHDL can handle such as BIT, INTEGER, and BOOLEAN.

-

Operators: Symbols that dictate operations, central to manipulating data types in VHDL code.

Examples & Applications

Creating an entity for an AND_GATE including input/output definitions.

Writing an architecture for the AND_GATE that implements the AND logic.

Defining data types like STD_LOGIC for improved signal handling.

Memory Aids

Interactive tools to help you remember key concepts

Rhymes

For VHDL, just be bold, entities tell us where to hold, architecture is where logic molds!

Stories

Imagine VHDL as a construction site. The entity is the blueprint, guiding how inputs and outputs connect, while the architecture details how each component builds the end project—like walls and roofs fitting together!

Memory Tools

Remember: E-A-C for VHDL structure: Entity, Architecture, Configuration.

Acronyms

BIS B-U-S for data types

BIT

INTEGER

SIGNED

BOOLEAN

UNSIGNED.

Flash Cards

Glossary

- VHDL

A hardware description language used to model the behavior of digital circuits.

- Entity

Defines the interface in a VHDL program including input/output ports.

- Architecture

Describes the internal workings of the circuit in a VHDL program.

- Configuration

Binds an entity to a specific architecture, usually optional in VHDL.

- Data Types

Define the type of values signals can hold, such as BIT or INTEGER.

- Operators

Symbols that specify operations performed on variables, such as logical and arithmetic operations.

Reference links

Supplementary resources to enhance your learning experience.