Example: Simple AND Gate - 2.2.4

Enroll to start learning

You’ve not yet enrolled in this course. Please enroll for free to listen to audio lessons, classroom podcasts and take practice test.

Interactive Audio Lesson

Listen to a student-teacher conversation explaining the topic in a relatable way.

Understanding the Entity

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Let's start with the entity of our AND gate. The entity defines the interface—can anyone explain what that means?

Does that mean it specifies what inputs and outputs our circuit has?

Exactly! In this case, we have two inputs, A and B, and one output, Y. The syntax helps in understanding what the external world sees. Can anyone recall the data types we used for our inputs and outputs?

They are all of type STD_LOGIC!

Correct! Remember, we're using STD_LOGIC for digital signals because it allows us to represent more than just binary values. Let's summarize: the entity defines the input/output structure, and we use specific data types for clarity.

Exploring the Architecture

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Next, let’s look at the architecture. What is the purpose of defining the architecture for our AND gate?

It describes how the circuit behaves based on the inputs?

Right! The architecture tells us how the inputs produce an output. In our case, we use the assignment statement to define that Y is the result of A AND B. Can anyone tell me the significance of using <= in that statement?

I think it signifies a signal assignment, right?

Exactly! The `<=` operator in VHDL is used for signal assignments, which is different from variable assignments using :=. Let’s emphasize that distinction: `<=` for signals, `:=` for variables.

Implementation and Simulation

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Now that we have our entity and architecture, how can we simulate the AND gate?

We need to create a testbench for it, right?

That's correct! A testbench will provide the necessary input stimuli and observe outputs. Who can remind us what makes a good testbench?

It should cover all possible input combinations to ensure the AND gate functions properly!

Excellent! So, remember to validate all input scenarios in your testbench to verify functionality.

Introduction & Overview

Read summaries of the section's main ideas at different levels of detail.

Quick Overview

Standard

The example illustrates the structure of VHDL code for a simple AND gate, demonstrating the entity and architecture components necessary to simulate the gate's functionality.

Detailed

Example: Simple AND Gate

In this section, we examine how to create a simple AND gate in VHDL. The example showcases the basic components of a VHDL program, which includes the entity and architecture.

VHDL Code Structure

The VHDL code for an AND gate consists of two primary parts:

- ENTITY: The entity named

AND_GATEdefines the circuit interface, specifying two input ports (AandBof typeSTD_LOGIC) and one output port (Y, also of typeSTD_LOGIC).

- ARCHITECTURE: The architecture section, named

behavior, describes how the inputs are processed to produce the output using the AND operation. The assignment statementY <= A AND B;executes the logic operation between inputs A and B.

This example serves as a foundational template for creating more complex VHDL programs, demonstrating the straightforward nature of logic design using the language.

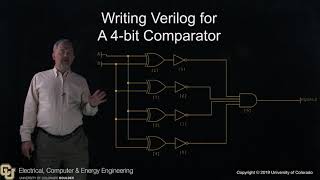

Youtube Videos

Audio Book

Dive deep into the subject with an immersive audiobook experience.

Entity Declaration

Chapter 1 of 2

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

LIBRARY ieee; USE ieee.std_logic_1164.ALL; ENTITY AND_GATE IS PORT ( A : IN STD_LOGIC; B : IN STD_LOGIC; Y : OUT STD_LOGIC ); END ENTITY AND_GATE;

Detailed Explanation

In this chunk, we have the entity declaration for an AND gate in VHDL. The libraries and standard logic types are first included with LIBRARY ieee; and USE ieee.std_logic_1164.ALL;. The ENTITY AND_GATE IS part defines a new entity called AND_GATE. Under this entity, we specify the PORT, which outlines the inputs and outputs of the gate.

Here, we have two inputs, A and B, both of type STD_LOGIC. This means they can hold binary values (0, 1, and others like high impedance). We also have one output, Y, which will be the result of the AND operation performed on inputs A and B.

Examples & Analogies

You can think of the entity like a product listing on an online store. The product (AND_GATE) has specific features (inputs A and B) and a final outcome (the output Y), which lets customers (users of the circuit) know what they can expect when they interact with it.

Architecture Definition

Chapter 2 of 2

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

ARCHITECTURE behavior OF AND_GATE IS BEGIN Y <= A AND B; END ARCHITECTURE behavior;

Detailed Explanation

This chunk defines the architecture of the AND_GATE entity. The keyword ARCHITECTURE signifies that we are describing the internal workings of the AND gate. In this architecture, we define a block called behavior which is responsible for processing the inputs to produce the output.

The line Y <= A AND B; executes the logical AND operation on inputs A and B. The <= operator indicates a signal assignment, meaning that the value of Y will reflect the result of A AND B. This structure makes it clear that if both A and B are 1 (true), then Y will also be 1; otherwise, Y will be 0.

Examples & Analogies

Imagine that the architecture is like a recipe for baking a cake. The inputs (A and B) are the ingredients, and the output (Y) is the final cake. The architecture (recipe) outlines what needs to be done with the ingredients (what combinations of A and B are mixed together) to ensure that the right cake (Y) is created.

Key Concepts

-

Entity: Defines the I/O interface of the circuit.

-

Architecture: Describes the internal behavior of the circuit.

-

STD_LOGIC: Allows more versatile binary signal representation.

Examples & Applications

The provided VHDL code for an AND gate demonstrates both entity and architecture components.

Memory Aids

Interactive tools to help you remember key concepts

Rhymes

Entity's our gate to the outside, with inputs and outputs we can't hide.

Stories

Imagine you have a factory (the architecture), which only works when specific parts (inputs) fit together to create a final product (output). Each assembly line is a signal assignment, constantly running to keep the production alive.

Memory Tools

E.A.S.Y - Entity, Architecture, Signal Assignment, Y output to remember the structure of AND gate in VHDL.

Acronyms

EAP - Entity, Architecture, Port for understanding VHDL Building blocks.

Flash Cards

Glossary

- Entity

A modular component in VHDL that defines the interface of a circuit, including inputs and outputs.

- Architecture

The body of a VHDL design that describes the internal workings and behavior of a circuit.

- STD_LOGIC

A data type in VHDL representing a singular binary signal which can take more than just binary values (e.g., '0', '1', 'Z', 'X').

- Signal Assignment

An operation in VHDL using the

<=operator to update the value of a signal.

Reference links

Supplementary resources to enhance your learning experience.