Verilog Basic Structure

Enroll to start learning

You’ve not yet enrolled in this course. Please enroll for free to listen to audio lessons, classroom podcasts and take practice test.

Interactive Audio Lesson

Listen to a student-teacher conversation explaining the topic in a relatable way.

Understanding Modules

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Today, we'll explore the fundamental building block of Verilog programming: the module. Can anyone tell me what a module is?

Isn't it like a container for inputs and outputs?

"Exactly! A module defines the inputs and outputs as well as the internal behavior of the circuit. For example, a simple AND gate can be defined as follows:

Use of Always Blocks

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Next, let’s discuss the always block. Who can explain what an always block does?

Is it used to perform continuous execution?

"Yes! The always block defines behavior that executes continuously, responding to changes in input signals. Here’s an example:

Combining Modules and Always Blocks

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Now, let’s talk about how we can combine modules and always blocks. Why do you think this combination is important?

It probably allows for more complex interactions among different modules.

Exactly! By integrating always blocks within modules, you can create sophisticated behaviors. Let’s consider an advanced example of a sequential circuit that employs both concepts.

Could that lead to problems if it’s not designed properly?

Yes! Proper design is crucial to avoid issues like race conditions. Always remember: 'Modules define, always blocks drive!' Would you like to explore a more intricate design together?

Introduction & Overview

Read summaries of the section's main ideas at different levels of detail.

Quick Overview

Standard

In this section, we explore the fundamental structure of Verilog, which includes the definition of modules and the use of always blocks. Examples of creating a simple AND gate demonstrate the concise syntax and functionality of Verilog.

Detailed

Detailed Summary

In Verilog programming, understanding the basic structure is crucial for designing digital circuits. A typical Verilog program comprises key elements, namely the Module and the Always Block.

Module

The module serves as the basic design building block in Verilog. It delineates the inputs, outputs, and internal behavior of the circuit. For example:

In this example, the AND_GATE module takes two inputs, A and B, and outputs Y based on the AND operation performed on A and B.

Always Block

The always block further defines the circuit's behavior by executing continuously as input signals change. An example of an always block is:

In this instance, the code states that whenever inputs A or B change, the output Y will update accordingly. This dynamic behavior is essential for synthesizing responsive digital systems.

By grasping these foundational elements, designers can utilize Verilog effectively to produce sophisticated digital designs, paving the way for advanced circuit simulation and implementation.

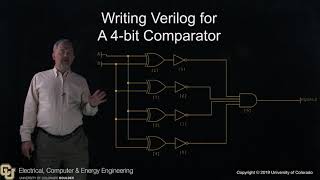

Youtube Videos

Audio Book

Dive deep into the subject with an immersive audiobook experience.

Module Definition

Chapter 1 of 2

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

A Verilog program typically consists of the following elements:

1. Module: The module is the basic unit of design in Verilog. It defines the inputs, outputs, and the internal behavior of the circuit.

Example:

module AND_GATE (input A, input B, output Y); assign Y = A & B; endmodule

Detailed Explanation

In Verilog, the module is a fundamental building block. It encapsulates all necessary elements for creating a digital circuit, including its inputs, outputs, and internal operations. For example, the provided AND_GATE module illustrates how two inputs, A and B, are defined along with an output Y. The operation performed within this module is specified by the assign statement, where the output Y is assigned the result of the logical AND operation between A and B.

Examples & Analogies

Think of a module like a kitchen in a restaurant. The kitchen is where all the cooking happens. Just like a kitchen has specific entrances (inputs), exits (outputs), and a defined way of preparing meals (internal behavior), a Verilog module defines how data enters, how it leaves, and how it processes that data internally.

Always Block

Chapter 2 of 2

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

- Always Block: The always block is used to define behavior that executes continuously whenever the input signals change.

Example:

always @ (A or B) begin Y = A & B; end

Detailed Explanation

The always block is a crucial construct in Verilog that specifies actions that should be triggered in response to changes in input signals. It continuously monitors the specified signals—in this case, A and B. Whenever either signal changes, the block executes the behavior defined within it, updating the output Y accordingly. This is essential for modeling dynamic behavior in digital circuits, ensuring outputs respond instantaneously to any input changes.

Examples & Analogies

Imagine a traffic light controlled by sensors that detect cars. When no cars are detected, the light stays green. However, once a car is detected (the input signal changes), the light immediately turns red to stop traffic. Similarly, the always block in Verilog reacts promptly to changes in input signals, adjusting outputs like a responsive traffic light.

Key Concepts

-

Module: The primary building block in Verilog that defines inputs, outputs, and behaviors.

-

Always Block: A construct in Verilog that allows for continuous monitoring of input changes and executing corresponding actions.

Examples & Applications

A simple AND gate defined as:

module AND_GATE (input A, input B, output Y);

assign Y = A & B;

endmodule

An always block defined for dynamic output:

always @ (A or B) begin

Y = A & B;

end

Memory Aids

Interactive tools to help you remember key concepts

Rhymes

In Verilog, the module stands tall, defining inputs for all.

Stories

Imagine a factory where modules are machines, each responsible for a part of production, activating when input arrives.

Memory Tools

M.A.D. - Module, Assign, Dynamic - key concepts of Verilog structure.

Acronyms

M.A.D. helps you remember

Modules Assign and are Dynamic.

Flash Cards

Glossary

- Module

A basic structure in Verilog that encapsulates a design's inputs, outputs, and behavior.

- Always Block

A construct in Verilog that specifies behavior that continuously executes when inputs change.

- Assign Statement

An operation within a module that assigns a value to an output based on inputs.

Reference links

Supplementary resources to enhance your learning experience.