Example: Simple AND Gate - 2.3.4

Enroll to start learning

You’ve not yet enrolled in this course. Please enroll for free to listen to audio lessons, classroom podcasts and take practice test.

Interactive Audio Lesson

Listen to a student-teacher conversation explaining the topic in a relatable way.

Introduction to the AND Gate

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Today, we will explore the concept of logic gates, starting with the AND gate, which outputs true only when all its inputs are true. Can anyone give me an example of how we might represent this in Verilog?

I think we use a module to define the AND gate and specify the inputs and outputs.

Exactly! The module is our main building block in Verilog. Let's look at the basic syntax for defining an AND gate.

Code Structure of AND Gate

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Here is the code snippet for the AND gate: `module AND_GATE (input A, input B, output Y); assign Y = A & B; endmodule`. What are the different parts of this code?

We have the module definition, the inputs `A` and `B`, and the output `Y`. The `assign` statement shows how `Y` is calculated.

Is `Y = A & B;` the same as saying 'Y is true if both A and B are true'?

Exactly, it implements the AND logic. Let's remember this as 'Output is TRUE when ALL Inputs are TRUE' – a clear way to recall AND gate functionality!

Understanding Input and Output in Verilog

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

In Verilog, inputs and outputs must be defined clearly. We used the keywords `input` and `output`. Why do you think this is important?

It defines how our module interacts with other modules or components, right?

Exactly, it establishes the interface! Always remember, clear interfaces lead to better designs.

Practical Implementation and Testing

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Once we have our AND gate implemented, what could be the next steps for using it in a larger system?

We might simulate it with different input combinations to test its functionality.

And we can use it as part of more complex circuits later on!

Exactly! This simple component can be a building block for more complex designs. Don't forget to think about how each part fits into the whole design.

Introduction & Overview

Read summaries of the section's main ideas at different levels of detail.

Quick Overview

Standard

In this section, a Verilog implementation of a simple AND gate is demonstrated, emphasizing the structure and syntax used to define modules, inputs, outputs, and the assignment of values.

Detailed

Example: Simple AND Gate

In this section, we explore the implementation of a simple AND gate using Verilog, a widely used hardware description language for FPGA designs. The provided example showcases how to define a module, specify inputs and outputs, and perform the logical AND operation.

Key Code Components:

- Module Definition: The structure begins with the

modulekeyword that encapsulates the entire design. - Input and Output Specification: Inside the module,

inputandoutputkeywords define the external signals interacting with the logic. - Behavioral Assignment: The

assignstatement is critical in Verilog, where we compute the output from the inputs using the AND operator (&).

This example serves as a foundational demonstration for students learning to write Verilog code for essential digital circuits.

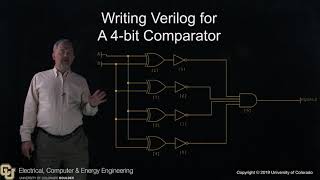

Youtube Videos

Audio Book

Dive deep into the subject with an immersive audiobook experience.

Defining the Module

Chapter 1 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

module AND_GATE (input A, input B, output Y);

Detailed Explanation

In Verilog, a hardware design usually starts with defining a 'module'. A module serves as the basic building block of your design. In this case, we are defining an 'AND_GATE' module that takes two inputs, A and B, and produces an output, Y. The inputs are specified with the 'input' keyword, while the output is denoted by 'output'. This structure sets up the basic interface for our AND gate.

Examples & Analogies

Think of a module like a light switch. The inputs A and B are like two different switches - when both are turned ON (or set to HIGH), the light (output Y) will illuminate. Just as each switch works together to control the light, the inputs combined determine the module's output.

Implementing the AND Operation

Chapter 2 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

assign Y = A & B;

Detailed Explanation

After defining the module, we implement its behavior using an 'assign' statement. Here, 'Y = A & B;' uses the '&' operator, which performs a bitwise AND operation. This means that the output Y will be HIGH only when both inputs A and B are also HIGH. It’s a simple logic operation where two inputs are checked, and their conjunction determines the output state.

Examples & Analogies

Imagine a secure door that only unlocks when BOTH the main key (input A) and a backup key (input B) are used simultaneously. The door (output Y) remains locked if either key is not inserted. This analogy illustrates how the AND gate functions: it requires both inputs to be 'active' for the output to be 'active'.

Ending the Module

Chapter 3 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

endmodule

Detailed Explanation

Every module defined in Verilog must be properly terminated with an 'endmodule' statement. This signals the end of the module’s definition. It's important for the compiler to know where the module's code ends so it can interpret and evaluate the design correctly. Every module can contain different logic or connections but always needs this closing part.

Examples & Analogies

Imagine writing a letter - you start with a greeting (the module definition), write the body (the implementation of the logic), and finally end it with 'Sincerely' (the 'endmodule' statement). Just like a letter needs a clear ending, a Verilog module must be clearly closed to ensure proper understanding of its limits and definitions.

Key Concepts

-

Module: A design unit in Verilog that includes inputs, outputs, and internal functionality.

-

AND Gate: A digital logic gate that outputs true (1) only when all inputs are true (1).

-

Assign Statement: A statement used in Verilog to assign a value to a signal.

Examples & Applications

A simple AND gate in Verilog can be written as follows:

module AND_GATE (input A, input B, output Y);

assign Y = A & B;

endmodule

This code illustrates the structure of a Verilog module that defines an AND gate, showing how A and B can be combined to determine Y.

Memory Aids

Interactive tools to help you remember key concepts

Rhymes

An AND gate's a team of two, only together, they pull through.

Stories

Think of two friends playing a game where both need to agree to win; only when both say ‘yes’ do they achieve their goal - this is like the AND gate!

Memory Tools

Remember A+ B = C means both must be alive for the goal to thrive!

Acronyms

AND

All Needed to Determine!

Flash Cards

Glossary

- Module

A fundamental building block in Verilog representing a design unit that may contain inputs, outputs, and internal logic.

- Assignment Statement

A statement that assigns values to signals in Verilog, often using the

assignkeyword.

- Logic Gate

A physical device that implements Boolean functions; in this case, the AND gate produces an output that is true only when all inputs are true.

Reference links

Supplementary resources to enhance your learning experience.