Power Management and Optimization in CMOS and FinFETs

Enroll to start learning

You’ve not yet enrolled in this course. Please enroll for free to listen to audio lessons, classroom podcasts and take practice test.

Interactive Audio Lesson

Listen to a student-teacher conversation explaining the topic in a relatable way.

Power Management Principles

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Today, we'll start understanding power management principles. Can someone tell me what they think power management involves?

Does it mean managing how much energy the chip uses?

Exactly! It's all about reducing energy consumption without compromising performance. One way we do this is through 'Active vs. Idle Power Control.'

What does that mean?

It means reducing dynamic power during active periods while eliminating leakage power when the device is idle. This leads to significant energy savings!

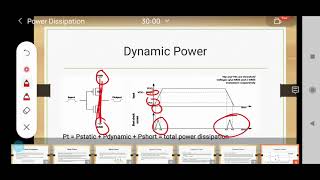

So, what's dynamic power?

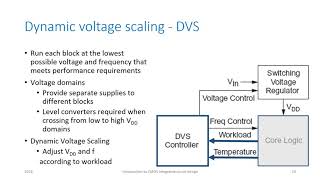

Great question! Dynamic power is the power consumed during active operation, related to voltage and frequency. This leads us to 'Dynamic Voltage and Frequency Scaling' or DVFS.

Can you summarize that for us?

Of course! We manage power by controlling dynamic power in active states and eliminating leakage when idle, primarily utilizing DVFS technology.

Power Optimization Techniques in CMOS

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Next, let's dive into power optimization techniques in CMOS technology. Why do you think it's crucial to focus on optimizing CMOS?

Because it's widely used in many devices, right?

Exactly! For minimizing dynamic power, lowering the supply voltage (Vdd) using DVFS is critical. What other methods can we use to reduce power?

I've heard of power gating?

Yes! Power gating involves cutting off power to inactive blocks, which minimizes leakage. Coupled with techniques like multi-Vt to manage leakage more efficiently, we can achieve great results.

I'm curious about low-capacitance interconnects. How does that help?

Low-capacitance interconnects reduce the energy needed for switching, which is essential for power efficiency. Remember, every little reduction counts!

Can you summarize this?

Sure! We optimize power in CMOS by lowering supply voltages, using power gating, low-capacitance materials, and multi-Vt techniques for better leakage control.

Power Optimization Techniques in FinFETs

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Let's transition to optimization in FinFET technologies. Who can tell me how FinFETs compares to CMOS in terms of leakage?

FinFETs have better leakage control, right?

Correct! FinFETs significantly reduce leakage, and we still have techniques like ultra-low voltage operation, which allows them to maintain performance even below 0.6V.

What’s back biasing?

Back biasing is a dynamic method for shifting the threshold voltage which balances performance and leakage. It’s a crucial technique in enhancing FinFET efficiency.

Any real-time applications?

Yes, near-threshold computing is great for always-on and sensor processing. It ensures power efficiency while maintaining essential operations.

Summarize these steps for us?

Absolutely! FinFETs optimize power using ultra-low voltages, back biasing, near-threshold computing, and dynamic adaptive scaling to enhance efficiency while managing leakage effectively.

Architectural Level Power Management

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Now let’s discuss architectural-level power management strategies. Why is it necessary to manage power at this level?

It allows optimization over larger systems and improves efficiency!

Exactly right! Adaptive workload management predicts system demands. Can someone explain how it helps?

It adjusts power states based on workload, right?

Correct! We also utilize real-time hardware monitors that can trigger changes like DVFS to manage power effectively. When thermal issues arise, how can we mitigate that?

By employing thermal-aware scheduling to prevent overheating!

Spot on! Utilizing idle-state management through firmware control of sleep transitions is another method in managing overall power capabilities.

Quick summary, please?

In summary, architectural level power management includes adaptive workload management, real-time monitoring, thermal-aware scheduling, and effective idle-state management to enhance power efficiency across systems.

Design Trade-Offs

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Finally, let’s discuss design trade-offs in power management. What do we mean by trade-offs?

It means balancing the benefits with the downsides of a design choice?

Exactly! For instance, lowering voltage saves power but may impact performance. Can someone provide another example?

Power gating reduces leakage but can cause longer wake-up times?

Exactly right! And multi-Vt design helps control leakage but can complicate timing closure. Best practices often involve combining several strategies like DVFS, clock gating, and power gating.

So, there’s always a choice to make in design?

Precisely! The goal is to find the optimal balance tailored to your application’s needs, focusing on performance, power, and reliability.

Introduction & Overview

Read summaries of the section's main ideas at different levels of detail.

Quick Overview

Standard

The section highlights the importance of effective power management in modern semiconductor designs, presenting various strategies including voltage and frequency scaling, power gating, and architectural-level optimizations. Techniques specific to both CMOS and FinFET technologies are elaborated to illustrate how power density and leakage issues can be managed.

Detailed

Power Management and Optimization in CMOS and FinFETs

This chapter presents essential principles of power management and optimization specifically tailored for modern CMOS and FinFET technologies, emphasizing their importance in energy-efficient designs. With the rising power density of semiconductor devices, particularly in applications such as mobile devices, IoT, and data centers, innovative power control strategies are vital.

Key Points:

- Challenges in Power Management: Modern ICs grapple with increased power density, high standby leakage, and complexities in managing multiple power states, necessitating robust strategies that ensure performance and reliability.

- Active vs. Idle Power Control: Mitigating power consumption involves strategies such as reducing dynamic power during active states and eliminating leakage when idle, employing techniques like Dynamic Voltage and Frequency Scaling (DVFS).

- CMOS Optimization: For CMOS technology, key strategies include reducing supply voltage, employing low-capacitance materials, and implementing multi-Vt and power gating techniques to lower leakage.

- FinFET Optimization: FinFETs provide better leakage control compared to CMOS and allow for ultra-low voltage operations. Techniques such as back biasing and dynamic adaptive scaling optimally manage power.

- Architectural Techniques: Implementations involving adaptive workload management, hardware monitors, and comprehensive thermal-aware scheduling can significantly enhance power management.

- Design Trade-Offs: There are inherent trade-offs in implementing power strategies, where aspects like performance, complexity, and latency requirements must be balanced.

Ultimately, aligning power optimization with application needs is crucial for developing efficient chips.

Youtube Videos

Audio Book

Dive deep into the subject with an immersive audiobook experience.

Introduction to Power Management

Chapter 1 of 9

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

This chapter explores the principles of power management and optimization strategies essential for energy-efficient CMOS and FinFET-based designs. As semiconductor technologies evolve, effective power management is crucial to balancing performance, reliability, and thermal constraints, especially in power-sensitive applications like mobile, IoT, and data centers. We focus on hardware-level power control, architectural-level optimizations, and system-wide strategies tailored to the unique characteristics of CMOS and FinFET technologies.

Detailed Explanation

This chunk introduces the concept of power management in semiconductor devices, specifically CMOS and FinFET technologies. It emphasizes the importance of power management for achieving efficiency in energy use while maintaining high performance and reliability. As technology progresses, managing power effectively becomes even more vital in areas such as mobile devices, IoT (Internet of Things), and data centers, where energy efficiency has a significant impact on system operation and cost.

Examples & Analogies

Think of a smartphone. Just like how a user needs to balance between battery life and performance (screen brightness for gaming vs. saving battery for calls), semiconductor technologies must balance power consumption and efficiency to ensure long-lasting and effective device performance.

Challenges in Modern Integrated Circuits

Chapter 2 of 9

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Modern integrated circuits face growing challenges:

● Increased power density from transistor scaling

● High standby leakage in CMOS

● Complex multi-core and mixed-domain power behavior in FinFETs

The design challenge is to minimize power at every abstraction layer while ensuring predictable performance and reliability. Without robust power management, system integrity and user experience suffer.

Detailed Explanation

This chunk outlines the key challenges faced by modern integrated circuits due to the increased power density as transistors shrink in size, which leads to higher power consumption. Standby leakage in CMOS transistors creates inefficiencies when the device is idle. Additionally, the complex power behaviors seen in multi-core processors and mixed-domain applications with FinFETs add to the difficulty of managing power effectively. The main goal is to minimize power usage while maintaining consistent performance and reliability; failing to do so can negatively impact the user experience and overall system integrity.

Examples & Analogies

Imagine a busy highway filled with cars (representing transistor scaling). As more cars (transistors) fill the highway, traffic jams (power density) increase, making it harder for everyone to move smoothly (efficient performance). Additionally, some cars may be idling, wasting fuel (standby leakage), which affects overall traffic flow (power management).

Principles of Power Management

Chapter 3 of 9

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

- Active vs. Idle Power Control:

○ Reduce dynamic power during active periods.

○ Eliminate leakage power during idle periods. - Voltage and Frequency Scaling:

○ Dynamic Voltage and Frequency Scaling (DVFS) allows the system to lower voltage and clock rates under lighter workloads. - Multiple Power Domains:

○ Different SoC blocks operate at independent voltages or power states. - Sleep Modes and Power Gating:

○ Power gating cuts off power to idle blocks, reducing leakage to near-zero. - Clock Management:

○ Clock gating stops switching activity in inactive modules.

Detailed Explanation

This chunk details the various principles used in power management. Active power control aims to minimize power usage when the device is busy, while idle power control focuses on preventing energy waste when the device is not in use. Voltage and frequency scaling helps adjust resource usage dynamically based on workload demands. Multiple power domains allow different parts of a system-on-chip (SoC) to have customized power levels based on their needs. Sleep modes and power gating are crucial for stopping power to non-essential components to avert leakage. Finally, clock management techniques, like clock gating, ensure inactive modules don't consume unnecessary power.

Examples & Analogies

Consider a smart home. When you're awake and using the lights (active power), your power usage is high. When you leave a room, you can turn off the lights (idle control) or dim them (voltage and frequency scaling) to save energy, just as different appliances can turn off or go into low power modes. In this way, managing when devices are on (active) or off (idle) maximizes efficiency.

Power Optimization in CMOS Technology

Chapter 4 of 9

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

- Dynamic Power Reduction in CMOS:

○ Lower Vdd through DVFS.

○ Use low-capacitance interconnects and logic gates.

○ Apply clock gating extensively. - Leakage Power Optimization:

○ Multi-Vt technology: high-Vt for non-critical paths.

○ Power gating using high-Vt sleep transistors.

○ Reverse body biasing to increase threshold voltage in idle mode. - Subsystem-Level Control:

○ Fine-grained power control over ALUs, caches, memory interfaces.

○ Deep-sleep modes with state retention flip-flops.

Detailed Explanation

This chunk focuses on specific strategies for optimizing power in CMOS technology. First, dynamic power can be reduced by lowering the supply voltage (Vdd) and using energy-efficient components. Second, leakage can be managed through advanced technologies such as Multi-Vt, which applies different threshold voltages selectively. Power gating and reverse body biasing provide further ways to minimize leakage when components are not in use. Finally, subsystem-level control aims for precise power management across various parts of a chip, making adjustments based on specific needs.

Examples & Analogies

Think of a car where you can adjust the engine settings for fuel efficiency (lower Vdd) and use lighter materials to reduce weight (low-capacitance components). When the car is parked, turning off unnecessary systems (power gating) keeps it from draining fuel. Also, the car can switch gears based on driving conditions (subsystem control) to optimize its performance and reduce waste.

Power Optimization in FinFET-Based Designs

Chapter 5 of 9

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

- Ultra-Low Voltage Operation:

○ FinFETs maintain switching performance even below 0.6V. - Back Biasing (Body Bias):

○ Used to dynamically shift threshold voltage, balancing performance and leakage. - Near-Threshold Computing:

○ Effective for always-on and sensor processing subsystems. - Dynamic Adaptive Scaling:

○ Real-time power tuning based on process, temperature, and workload. - Fine-Grained Clock and Power Domains:

○ Implemented with hierarchical power rails and clock islands.

Detailed Explanation

This chunk elaborates on optimization techniques specifically for FinFET technology. Ultra-low voltage operation allows FinFETs to function efficiently at lower voltage levels, which can save energy. Back biasing provides a method to adjust the operating threshold as needed to optimize performance without increasing leakage. Near-threshold computing is beneficial for devices that need to maintain basic functionality at very low power levels. Dynamic adaptive scaling allows real-time adjustments to power based on conditions, while fine-grained power and clock domains improve energy management across different system parts.

Examples & Analogies

Imagine a thermostat in your home that adjusts the heating or cooling based on the outside temperature (dynamic adaptive scaling). When it’s cooler outside, the system can minimize power use while still keeping your home comfortable (near-threshold computing). Just like a smart home system can react to when rooms are used (fine-grained clock domains), ensuring comfort without wasting energy, FinFET designs adapt to demands, using power efficiently.

Architectural and System-Level Power Management

Chapter 6 of 9

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

- Adaptive Workload Management:

○ Software predicts workload and shifts system between power states. - Hardware Monitors and Feedback Loops:

○ Sensors monitor voltage, current, and temperature in real time.

○ Feedback circuits trigger DVFS or shutdown logic. - Thermal-Aware Scheduling:

○ Workload scheduling prevents local overheating and throttling. - Idle-State Management:

○ OS and firmware control sleep transitions (e.g., C-states in CPUs). - Power-Aware Design Flow (EDA):

○ Static and dynamic power analysis during RTL and layout stages.

○ Insertion of clock/power gating cells through synthesis.

Detailed Explanation

Here, we explore architectural and system-level approaches to power management. Adaptive workload management predicts periods of high and low activity, allowing the system to transition to appropriate power states accordingly. Hardware monitors provide crucial data on voltage, current, and temperature, enabling timely adjustments through feedback mechanisms. Thermal-aware scheduling helps in managing workloads to avoid overheating, and effective idle-state management ensures systems transition properly into low-power states. Additionally, power-aware design methodologies enable careful power consideration during the design stages of semiconductor chips.

Examples & Analogies

Consider a busy restaurant. The staff adjusts service levels based on customer flow (adaptive workload management). When it's hot in the kitchen, they could adjust cooking methods to avoid overheating (thermal-aware scheduling). The restaurant also prep itself for busy hours but cuts down on staff (idle-state management) when it's quiet, ensuring resource efficiency throughout the day.

Design Trade-Offs and Best Practices

Chapter 7 of 9

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Strategy Benefit Trade-Offs

Lower Vdd Saves dynamic power May reduce performance (DVFS)

Power Gating Eliminates leakage in idle Wake-up latency and routing

Clock Gating Cuts dynamic switching Added logic and power verification

Multi-Vt Design Controls leakage Timing closure complexity selectively

Fine-Grain Maximize flexibility Increases design/test overhead

Best practice: Combine DVFS + clock gating + power gating at different layers (block, core, chip) for optimal results.

Detailed Explanation

This chunk presents various strategies for power management, their benefits, and potential trade-offs. Lowering supply voltage can significantly reduce dynamic power consumption but may impact performance (DVFS). Power gating effectively eliminates leakage but can introduce delays when waking up inactive components. Clock gating helps reduce dynamic switching power but adds complexity in verification. Multi-Vt allows for selective leakage control but complicates timing. Fine-grain power management maximizes flexibility, yet this approach can require more extensive design and testing resources. The best practice is to integrate multiple strategies across different system levels for optimal efficiency.

Examples & Analogies

Think of a multi-tasking employee. Lowering work hours (lowering Vdd) can save the company on payroll (reducing dynamic power) but might slow down project completions (performance). Cutting back on unnecessary meetings (power gating) helps focus on essential work, even if it means some delays in communicating with remote team members (wake-up latency). Combining various strategies, like adjusting hours and meetings based on skillsets, can maximize overall productivity.

Real-World Example: Power Management in Mobile SoCs

Chapter 8 of 9

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

● Application Processor (FinFET-based):

○ CPU cores with DVFS

○ GPU in separate voltage island

○ Always-on domain with subthreshold logic

○ Audio/Voice Processing Unit with near-threshold voltage

● Power Controller:

○ Real-time power state manager

○ Manages transitions and retention registers

○ Interfaces with OS for sleep/wake signals

Result:

● Delivers full performance during intensive tasks.

● Achieves <1 mW idle power for always-on features.

● Enables day-long usage on a single battery charge.

Detailed Explanation

This chunk presents a real-world case study of power management in mobile System-on-Chips (SoCs). In this case, a FinFET-based application processor utilizes dynamic voltage and frequency scaling (DVFS) to optimize performance. The GPU operates in a separate voltage domain, which helps manage power effectively. There’s also an always-on domain that uses minimal power logic to maintain functionality even during low power consumption states. The power controller is crucial in managing real-time conditions, ensuring the device can switch effectively between power states. This results in the SoC achieving extremely low power usage while maintaining optimal performance conditions.

Examples & Analogies

Envision how a high-performance sports car can switch gears to optimize both speed and fuel efficiency. The mobile SoC, much like this car, can adjust its operational modes (performance and low power) based on the demand, enabling users to enjoy full functionality while extending battery life significantly, akin to how reconfigurable driving modes can enhance the performance of a vehicle.

Conclusion on Power Management

Chapter 9 of 9

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Effective power management in CMOS and FinFET technologies is essential for building scalable, reliable, and energy-efficient systems. While CMOS offers mature techniques for dynamic and static power control, FinFET enhances efficiency further with better leakage suppression and subthreshold behavior.

Key takeaways:

● Combine multiple power strategies (DVFS, clock/power gating, multi-Vt).

● Leverage architecture-level partitioning and hardware-software co-design.

● Tailor techniques to application needs: performance-critical vs ultra-low-power.

Detailed Explanation

The conclusion emphasizes the importance of effective power management to create systems that remain scalable and efficient. CMOS technologies already have established methods for controlling power use, while FinFET designs provide even further improvements, particularly in minimizing leakage and improving efficiency in low-energy operations. Key takeaways encourage the integration of various power management strategies, focusing on system architecture and cooperation between software and hardware. It also stresses customizing approaches to meet the specific requirements of applications, whether those are high-performance or focused on ultra-low-power consumption.

Examples & Analogies

Imagine a company that customizes its products for different market needs. Just like tailoring a marketing strategy for a high-budget campaign versus a cost-effective community approach, power management techniques must align with the specific demands of varied applications. Combining strategies for different needs ensures that products perform optimally while conserving resources efficiently.

Key Concepts

-

Power Management: Strategies to reduce power consumption in semiconductor devices.

-

Dynamic Voltage and Frequency Scaling (DVFS): A technique to optimize voltage and frequency based on workload.

-

Power Gating: Cutting off power to inactive parts of a circuit to save energy.

-

FinFET Technology: A transistor technology that enhances performance and reduces leakage.

Examples & Applications

Using DVFS, a microcontroller reduces supply voltage during low workload periods to conserve energy.

A FinFET-based chip can operate effectively at lower voltages, improving power efficiency compared to traditional CMOS.

Memory Aids

Interactive tools to help you remember key concepts

Rhymes

When the power's low and devices sleep, power gating cuts the leakage deep.

Stories

Imagine a busy highway; when cars slow down, traffic eases. Similarly, DVFS reduces voltage when workloads are light, allowing sustainable traffic flow through chips.

Memory Tools

Remember 'AGILE' for power management: Active vs. Idle, Gear down voltage, Idle management, Leakage reduction, Efficiency.

Acronyms

PACES for best practices

Power Gating

Adaptive Scaling

Clock Gating

Efficiency strategies

Standards compliance.

Flash Cards

Glossary

- Active Power Control

Management of power during a device’s active operational state.

- Idle Power Control

Techniques used to eliminate power consumption when the device is not in use.

- Dynamic Voltage and Frequency Scaling (DVFS)

A technique to adjust voltage and frequency according to workload demands.

- Power Gating

A method to cut power to inactive blocks within a circuit.

- FinFET

A type of transistor offering improved electrostatics and leakage control.

- ThermalAware Scheduling

A technique that manages workload scheduling to mitigate overheating.

- MultiVt Technology

A design technique using transistors with different threshold voltages to manage leakage.

Reference links

Supplementary resources to enhance your learning experience.