Step 2: Power Optimization in CMOS Technology

Enroll to start learning

You’ve not yet enrolled in this course. Please enroll for free to listen to audio lessons, classroom podcasts and take practice test.

Interactive Audio Lesson

Listen to a student-teacher conversation explaining the topic in a relatable way.

Dynamic Power Reduction

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Today we’re going to discuss dynamic power reduction in CMOS. What do you think is one of the biggest contributors to dynamic power consumption?

Is it the supply voltage?

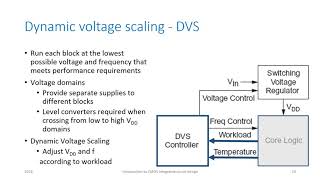

Exactly! Lowering the supply voltage, or Vdd, is key. This is often achieved through Dynamic Voltage and Frequency Scaling, or DVFS. Can anyone explain DVFS?

I think it adjusts the voltage and clock frequency based on the workload.

Correct! By reducing voltage and frequency during lighter workloads, we can significantly reduce dynamic power. Remember, power scales with the square of the voltage!

How about clock gating? How does that help?

Great question! Clock gating turns off the clock signal to inactive components, preventing unnecessary switching activity. This method also saves power. Let's recap: DVFS lowers voltage and frequency under light loads, and clock gating stops inactive modules from consuming power.

Leakage Power Optimization

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Now let’s shift our focus to leakage power optimization. What do you think is one major technique for tackling leakage?

Using high-Vt transistors for non-critical paths?

Exactly! This approach is often part of what's known as multi-Vt technology. It helps in controlling leakage effectively. Can anyone mention another technique?

What about power gating using high-Vt sleep transistors?

Great point! Power gating allows us to cut off power from blocks that are not in use, minimizing leakage to near-zero. Remember, less power in idle states means more efficiency overall.

Could reverse body biasing help too?

Yes! Reverse body biasing increases the threshold voltage during idle times, which further reduces leakage. So, we've learned multi-Vt, power gating, and reverse body biasing as effective strategies.

Subsystem-Level Control

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Let's discuss subsystem-level control for power management. Why do you think this is important?

It allows targeted power management over specific components.

Exactly! This ensures that only the necessary components are powered. Can anyone share an example of such control in action?

CMOS-based microcontrollers use different power modes, right?

Spot on! These microcontrollers can operate in up to five different power modes, balancing between current draw and response time. This level of control makes systems much more energy-efficient.

What are some methods used to retain states in these deep-sleep modes?

Great question! Specialized state retention flip-flops are commonly used in this scenario. So, to summarize, subsystem-level control optimizes power usage through targeted management and innovative state retention mechanisms.

Introduction & Overview

Read summaries of the section's main ideas at different levels of detail.

Quick Overview

Standard

Power optimization in CMOS technology focuses on reducing dynamic and leakage power through techniques such as dynamic voltage scaling, power gating, and subsystem-level control. This ensures energy-efficient designs while maintaining system performance and reliability.

Detailed

Power Optimization in CMOS Technology

Power optimization is a critical concern in the design of CMOS circuits, particularly as technology scales down to smaller nodes. Key strategies include:

- Dynamic Power Reduction: This involves lowering the supply voltage (Vdd) through techniques like Dynamic Voltage and Frequency Scaling (DVFS), utilizing low-capacitance interconnects and logic gates, and extensively applying clock gating to minimize dynamic power during operation.

- Leakage Power Optimization: Addressing leakage power is vital, especially with the advent of smaller technology nodes. Techniques include employing multi-Vt technology, where higher threshold voltages are used for non-critical paths, utilizing power gating with high-Vt sleep transistors, and reverse body biasing to increase the threshold voltage in idle states, thereby minimizing leakage when circuits are inactive.

- Subsystem-Level Control: This technique allows for fine-grained control over subsystems such as ALUs, caches, and memory interfaces. Deep-sleep modes can be implemented while retaining the state through specialized flip-flops, enabling different power modes - such as in CMOS-based microcontrollers which may have up to five optimized power modes to balance current draw and response time.

These strategies collectively enhance the energy efficiency of CMOS designs, essential for applications ranging from mobile devices to large data centers.

Youtube Videos

Audio Book

Dive deep into the subject with an immersive audiobook experience.

Dynamic Power Reduction in CMOS

Chapter 1 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

- Dynamic Power Reduction in CMOS:

- Lower Vdd through DVFS.

- Use low-capacitance interconnects and logic gates.

- Apply clock gating extensively.

Detailed Explanation

Dynamic power reduction in CMOS refers to the techniques used to minimize the power consumed when the circuit is active. One effective method is Dynamic Voltage and Frequency Scaling (DVFS), which allows the adjustment of supply voltage (Vdd) and clock frequency based on the active workload. Lowering the Vdd reduces the overall power consumed because power is proportional to the square of the voltage. Furthermore, using low-capacitance interconnects and logic gates helps decrease the amount of energy needed for switching, as less energy is dissipated when these components operate. Lastly, clock gating is a technique where the clock signal is turned off to portions of the circuit that are not in use, effectively reducing dynamic power consumption during idle periods.

Examples & Analogies

Think of dynamic power reduction like a car that can adjust its engine performance based on how fast it's going. If the car is driving slowly in a parking lot, it doesn't need to use as much power, and it can go easy on the gas—like lowering Vdd in a CMOS circuit. Similarly, just as a car can turn off some systems (like air conditioning) while idling, clock gating allows parts of the circuit to shut off their clock when they're not needed, saving energy.

Leakage Power Optimization

Chapter 2 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

- Leakage Power Optimization:

- Multi-Vt technology: high-Vt for non-critical paths.

- Power gating using high-Vt sleep transistors.

- Reverse body biasing to increase threshold voltage in idle mode.

Detailed Explanation

Leakage power optimization addresses the issue of power loss in circuits when they are idle. Multi-Vt technology involves using transistors with different threshold voltages (Vt) to strategically manage leakage; high-Vt transistors are used in paths that are not critical to performance, effectively cutting down the leakage in those areas. Power gating is a method that utilizes high-Vt sleep transistors to disconnect power from parts of the circuit that are not in use, nearly eliminating leakage. Additionally, reverse body biasing can be employed to increase the threshold voltage during idle periods, further reducing leakage current when the circuit is not active.

Examples & Analogies

Imagine a light switch in your home that you turn off in rooms that are not in use. This is similar to power gating: by turning off power to certain parts of the circuit, leakage is minimized. Using high-Vt technologies is like using special light bulbs that consume less energy when they're off. Reverse body biasing is akin to putting a dimmer on your lights, so they use less energy when you don't need bright light.

Subsystem-Level Control

Chapter 3 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

- Subsystem-Level Control:

- Fine-grained power control over ALUs, caches, memory interfaces.

- Deep-sleep modes with state retention flip-flops.

Example: CMOS-based microcontrollers use up to 5 different power modes, each optimized for current draw and response time.

Detailed Explanation

Subsystem-level control refers to the ability to manage power at a more detailed level within a chip. This involves having fine-grained control over different components such as Arithmetic Logic Units (ALUs), caches, and memory interfaces, allowing them to operate in power-saving modes when not in full use. Implementing deep-sleep modes means that these components can retain their states while using very little power, which is achievable with special memory elements known as state retention flip-flops. For example, some CMOS-based microcontrollers can adaptively switch between up to five different power modes, each tailored to minimize current draw while maintaining an appropriate response time for any given task.

Examples & Analogies

Think of a smart home that can adjust energy usage according to different times and activities. Some rooms might be in 'night mode' when you're sleeping, using less energy for lights and heating—this is like deep-sleep modes for circuits. The microcontroller is like the manager of the house, making sure each room (or component) only uses as much energy as it needs.

Key Concepts

-

Dynamic Power Reduction: Techniques to lower power during active operation.

-

Leakage Power Optimization: Methods to minimize power during idle states.

-

Subsystem-Level Control: Fine-grained power management at the component level.

Examples & Applications

A CMOS-based microcontroller can operate in different modes, optimizing power usage based on the required performance.

Using multiple Vt transistors allows a circuit to maintain efficiency while minimizing leakage in non-critical paths.

Memory Aids

Interactive tools to help you remember key concepts

Rhymes

To save power, we set the clock, while voltage drops to save the shock.

Stories

Imagine a busy street with cars stopping at red lights. When the light is green, they drive fast (high voltage); when red, they stop (low voltage). This is like DVFS managing voltage for efficiency.

Memory Tools

DPS - Dynamic Power Strategies: DVFS, Power Gating, Subsystem Control.

Acronyms

LCP - Leakage Control Plan

use Multi-Vt

Power Gating

and Reverse Body Biasing.

Flash Cards

Glossary

- Dynamic Voltage and Frequency Scaling (DVFS)

A technique that allows the adjustment of voltage and frequency based on workload, reducing dynamic power consumption.

- Leakage Power

The static power consumed by a transistor even when it is not switching.

- MultiVt Technology

Using transistors with different threshold voltages in a circuit to minimize leakage power in non-critical paths.

- Power Gating

The technique of cutting off power to inactive blocks to reduce leakage.

- Clock Gating

Stopping the clock signal to inactive parts of a circuit to prevent power consumption due to switching.

- State Retention FlipFlops

Specialized flip-flops that retain their state during low-power modes.

Reference links

Supplementary resources to enhance your learning experience.