Step 1: Principles of Power Management

Enroll to start learning

You’ve not yet enrolled in this course. Please enroll for free to listen to audio lessons, classroom podcasts and take practice test.

Interactive Audio Lesson

Listen to a student-teacher conversation explaining the topic in a relatable way.

Active vs. Idle Power Control

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Let's start discussing the principles of power management by understanding the difference between active and idle power control. Can anyone tell me why it's important to reduce dynamic power during active periods?

It helps save battery life and keeps the device cooler.

Exactly! And what about idle periods? Why is eliminating leakage power so crucial?

Because it can drain the battery even when the device is not in use.

Good points! Remember this with the acronym AID—Active Idle Dynamic!

AID for Active Idle Dynamic sounds easy to remember!

Yes, it encapsulates our key focus areas! In summary, managing dynamic power during active use and eliminating leakage during idle states is pivotal for energy efficiency.

Voltage and Frequency Scaling

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Now let's explore Dynamic Voltage and Frequency Scaling, or DVFS. What advantages do you think this system might provide?

It allows your device to operate more efficiently based on the current workload.

Correct! By reducing the voltage and clock rates under lighter workloads, we minimize power consumption. Can anyone explain how this relates to performance?

Lowering these values can improve battery life without significantly affecting performance.

Exactly! I want you to remember DVFS like 'Dynamic Volts, Flexible Speed'. Now, what does that imply about overall device performance?

It means we’ve got a balance; we can adjust our performance needs dynamically.

Exactly! In summary, DVFS provides flexibility to adapt to workloads while maintaining power efficiency.

Multiple Power Domains

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Next, we will discuss multiple power domains in System on Chip designs. Why do you think separating power domains is beneficial?

It allows different parts of the chip to manage their power needs independently.

Correct! Each SoC block can operate at independent voltages or states, which enhances energy efficiency. How does this relate to overall system performance?

It means power isn’t wasted on parts that aren't in use.

Exactly! This modular approach can lead to significant power savings. Remember this concept as MPD—Modular Power Domains. Let’s summarize: Multiple power domains enhance efficiency by allowing independent power management across SoC blocks.

Sleep Modes and Power Gating

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Let's talk about sleep modes and power gating. Why are these techniques so significant in power management?

They can cut off power to parts of the circuit that aren't needed, which greatly reduces leakage.

Yes! Power gating effectively minimizes the leakage power to near-zero levels during inactivity. Does anyone know a mnemonic to remember this concept?

Maybe something like SLEEP—Shut off Leakage Energy Efficiently, Power?

Great mnemonic! SLEEP captures the essence beautifully! In summary, implementing sleep modes and power gating contributes greatly to power reduction in SoCs.

Clock Management

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Now let's wrap up our discussion with clock management. What role does clock gating play in power management?

It stops switching activity in inactive modules, so no energy is wasted there!

Correct! By halting signal transitions in idle parts, we can significantly lower unnecessary power consumption. Any suggestions for an acronym to remember this?

How about CG—Clock Gating?

Perfect! CG can help reinforce this critical concept. To summarize, clock management, particularly clock gating, is essential for minimizing energy use effectively in inactive areas.

Introduction & Overview

Read summaries of the section's main ideas at different levels of detail.

Quick Overview

Standard

The section presents several essential techniques for power management, covering concepts like active vs. idle power control, voltage and frequency scaling, the use of multiple power domains, sleep modes, power gating, and clock management. These strategies are vital for enhancing the efficiency of integrated circuits, especially in power-sensitive applications.

Detailed

Step 1: Principles of Power Management

This section delves into critical techniques for power management within integrated circuits, particularly focusing on CMOS and FinFET technologies. As power consumption becomes increasingly vital in device performance, understanding how to effectively manage power is essential.

Key Concepts:

- Active vs. Idle Power Control: During active periods, it’s crucial to reduce dynamic power consumption, while during idle states, eliminating leakage power is necessary for efficiency.

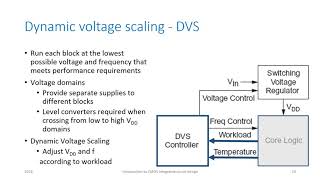

- Voltage and Frequency Scaling: Dynamic Voltage and Frequency Scaling (DVFS) adjusts the voltage and clock rates based on workload. This flexibility allows for significant power savings during lighter workloads.

- Multiple Power Domains: Different blocks within a System on Chip (SoC) can operate at varying voltages and power states, optimizing power usage based on specific operational needs.

- Sleep Modes and Power Gating: Implementing sleep modes where power is cut off to inactive blocks drastically reduces leakage power to near-zero levels. This is crucial for conserving energy during inactivity.

- Clock Management: Techniques like clock gating can halt signal transitions in inactive units, preventing unnecessary power consumption during these periods.

Together, these principles form a foundational understanding of how to manage and optimize power usage in modern semiconductor designs.

Youtube Videos

Audio Book

Dive deep into the subject with an immersive audiobook experience.

Active vs. Idle Power Control

Chapter 1 of 5

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

- Active vs. Idle Power Control:

- Reduce dynamic power during active periods.

- Eliminate leakage power during idle periods.

Detailed Explanation

Power control can be categorized into two main modes: active and idle. When a device is actively processing data (active mode), it consumes dynamic power, which is power used for performing calculations and processing tasks. The aim is to minimize this dynamic power consumption by optimizing operations and perhaps adjusting voltage levels. On the other hand, when the device is not in use (idle mode), it can exhibit leakage power—this is power that a device consumes even when it is not actively processing any data. The goal in idle mode is to eliminate or drastically reduce leakage power to conserve energy.

Examples & Analogies

Consider a light bulb in a room. When someone is in the room and the light is on, it's like the device being active. The energy used by the light bulb represents dynamic power. When the room is empty, the bulb is turned off to save energy, akin to reducing leakage power during idle periods. Just like you wouldn't leave the light on when no one is there, minimizing power when a device is not in use is key.

Voltage and Frequency Scaling

Chapter 2 of 5

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

- Voltage and Frequency Scaling:

- Dynamic Voltage and Frequency Scaling (DVFS) allows the system to lower voltage and clock rates under lighter workloads.

Detailed Explanation

Dynamic Voltage and Frequency Scaling (DVFS) is a technique that adjusts the voltage and frequency of a processor based on the workload demand. When a device is handling a lighter workload, it can lower both the voltage and the clock speed. This decrease significantly reduces power consumption while still maintaining the necessary performance levels for less demanding tasks. Conversely, during heavy computational tasks, the system can ramp up the voltage and frequency to provide the needed performance.

Examples & Analogies

Think of a car driving on a highway. At full speed (high load), the engine uses more fuel (like high voltage and frequency). However, in a slower, stop-and-go traffic situation (light load), the driver can ease off the accelerator (lower frequency) and still progress at an acceptable pace while using less fuel (lower voltage).

Multiple Power Domains

Chapter 3 of 5

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

- Multiple Power Domains:

- Different SoC blocks operate at independent voltages or power states.

Detailed Explanation

In a System on Chip (SoC), different components can operate at their own voltages or power states. This method uses multiple power domains, allowing each block (like processors, memory, and I/O interfaces) to function independently regarding power requirements. For instance, if one part of the chip is active while another is not, the inactive part can be set to a lower voltage or turned off altogether, effectively managing power more efficiently across the system.

Examples & Analogies

Imagine a multi-room house that has different heating zones. Each room can have its heating adjusted based on usage. If you're not using a bedroom, you can lower the heat there while keeping the living room warm for your activities. This approach helps save energy and maintain comfort, similar to how power domains in an SoC manage energy use across different blocks.

Sleep Modes and Power Gating

Chapter 4 of 5

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

- Sleep Modes and Power Gating:

- Power gating cuts off power to idle blocks, reducing leakage to near-zero.

Detailed Explanation

Sleep modes allow parts of a device to enter a low-power state when they are not in active use. Power gating is a more aggressive approach that involves disconnecting power to certain circuit blocks entirely to eliminate leakage current. In this way, the components can be brought back online quickly when needed, while leakage is minimized to almost non-existent levels, which is crucial for energy efficiency in modern devices.

Examples & Analogies

Imagine a sleeping phone that is completely turned off versus one that is on stand-by but still draws a small charge. When the phone is powered down completely (like power gating), it uses almost no battery compared to being on stand-by where it consumes more. This analogy highlights how devices can be more energy-efficient by cutting off power completely when not in active use.

Clock Management

Chapter 5 of 5

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

- Clock Management:

- Clock gating stops switching activity in inactive modules.

Detailed Explanation

Clock management focuses on reducing power consumption by controlling signal switching in circuits. Clock gating is a technique used to disable the clock signal to parts of a circuit that are not in active use. By doing so, it prevents unnecessary power consumption since the inactive components do not perform any switching activities or barring state changes, leading to significant energy savings.

Examples & Analogies

Think of a classroom with lights in each section. If no students are in one section, turning the lights off in that section prevents energy waste. In digital circuits, clock gating works similarly by turning off the 'lights' (clock signals) to sections that aren’t currently doing any work, thereby saving energy.

Key Concepts

-

Active vs. Idle Power Control: During active periods, it’s crucial to reduce dynamic power consumption, while during idle states, eliminating leakage power is necessary for efficiency.

-

Voltage and Frequency Scaling: Dynamic Voltage and Frequency Scaling (DVFS) adjusts the voltage and clock rates based on workload. This flexibility allows for significant power savings during lighter workloads.

-

Multiple Power Domains: Different blocks within a System on Chip (SoC) can operate at varying voltages and power states, optimizing power usage based on specific operational needs.

-

Sleep Modes and Power Gating: Implementing sleep modes where power is cut off to inactive blocks drastically reduces leakage power to near-zero levels. This is crucial for conserving energy during inactivity.

-

Clock Management: Techniques like clock gating can halt signal transitions in inactive units, preventing unnecessary power consumption during these periods.

-

Together, these principles form a foundational understanding of how to manage and optimize power usage in modern semiconductor designs.

Examples & Applications

Active vs. Idle Power Control enhances battery performance in devices like smartphones by dynamically adjusting power requirements.

Using DVFS allows a computer to lower its power draw during simple tasks like web browsing, increasing battery life significantly.

Multiple power domains in a mobile SoC enable individual management of power for the CPU, GPU, and other components, optimizing overall system efficiency.

Power gating in microcontrollers can stop power of non-critical peripherals when not in use, effectively reducing leakage power.

Clock gating in data centers can significantly lower power usage during nighttime when load is reduced.

Memory Aids

Interactive tools to help you remember key concepts

Rhymes

When the circuit is light, keep power out of sight; during rest, reduce the quest!

Stories

Imagine a house where every room has its own light switch; you only turn on the lights when using the room—that’s managing your energy!

Memory Tools

Think of DVFS as 'Dynamic Volts for Flexible Speed' to remember its function.

Acronyms

AID

Active Idle Dynamic helps us remember the focus on both active and idle power control.

Flash Cards

Glossary

- Dynamic Voltage and Frequency Scaling (DVFS)

A power management technique that adjusts the voltage and frequency according to the current workload.

- Power Gating

A technique that cuts off power to idle blocks to minimize leakage power.

- Clock Gating

A power-saving technique that stops clock signals to inactive modules to prevent unnecessary power consumption.

- Multiple Power Domains

A design approach allowing different blocks in a circuit to operate at varying power states or voltages.

- Active Power Control

The management of dynamic power consumption during active operation.

- Idle Power Control

The strategy to eliminate leakage power during idle states of operation.

Reference links

Supplementary resources to enhance your learning experience.