Step 4: Design Trade-Offs and Best Practices

Enroll to start learning

You’ve not yet enrolled in this course. Please enroll for free to listen to audio lessons, classroom podcasts and take practice test.

Interactive Audio Lesson

Listen to a student-teacher conversation explaining the topic in a relatable way.

Lower Vdd (DVFS)

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Let's start by discussing the concept of lowering the supply voltage using Dynamic Voltage and Frequency Scaling or DVFS. Does anyone know what DVFS stands for?

Dynamic Voltage and Frequency Scaling! It helps save power, right?

Exactly! Lowering the voltage can significantly decrease dynamic power consumption, but what do we need to consider when we lower Vdd?

It might affect the performance, especially under high workload!

That's spot on! Balancing power savings with performance is crucial. Think of it as a seesaw—too much weight on one side affects the other.

So, we must ensure the system operates effectively while managing power!

Precisely! Recap: DVFS helps save power by reducing Vdd but may decrease performance during high-demand tasks. How do we remember this?

Maybe think of DVFS as a dimmer switch—lowering the voltage dims the performance!

Great analogy! So, remembering DVFS as the dimmer switch of power management can help us frame our understanding.

Power Gating

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Now, let's explore power gating. Who can tell me what its purpose is?

It eliminates leakage power in idle components!

Exactly! But what do you think are some potential downsides of using power gating?

There might be latency when waking components back up.

Yes! Wake-up latency is a significant factor to consider. And what about the routing complexity—what's the concern there?

That it can complicate the design and verification processes.

Spot on! The benefits of eliminating leakage are weighed against complexity and latency. Can anyone suggest a mnemonic to help remember power gating's trade-offs?

Maybe something like 'Power Gone, Wait Long'?

Fantastic! So, keep in mind: while power gating reduces leakage, it may come with wait time!

Clock Gating

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Moving on to clock gating! What does this technique aim to achieve?

It cuts down dynamic switching power by stopping clocks for inactive modules!

Exactly! But what about the implications? Any trade-offs to discuss?

I think adding logic for clock gating can increase design complexity including verification tasks!

Right! While it reduces power, it complicates the design process. How might we remember this trade-off?

Maybe 'Less Power, More Time'?

Perfect! A simplified way to recall the benefit and cost of clock gating.

So it’s about finding that balance between power savings and maintaining efficiency in design effort!

Exactly! Balancing these factors is key to effective power management strategies.

Multi-Vt Design

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Let’s now discuss multi-Vt design. What are the main benefits of this approach?

It allows control of leakage selectively across circuit paths!

Correct! Now, what trade-off does it introduce?

It complicates timing closure!

Absolutely! It brings added complexity to synchronization across the circuit. Any creative ways to remember it?

Maybe 'Select Vt, Complicate the Net'? It rhymes and captures the essence.

Excellent memory aid! The balance in multi-Vt design showcases both efficiency and complexity.

So we trade off some design simplicity for better leakage control!

Exactly! Each design decision requires careful consideration of these trade-offs.

Best Practices

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

To wrap up, let’s talk about best practices. What strategy do we recommend?

Combining DVFS, clock gating, and power gating!

Right! Why is it advantageous to combine these approaches?

It allows us to approach power management from different architectural layers!

Exactly! So how do we remember the importance of a combined approach?

Maybe something like 'Layered Power Saves' to emphasize stacking strategies.

Great mnemonic! The strategic combination promotes energy efficiency without sacrificing performance. Can anyone summarize our discussion?

We learned to balance power savings with performance trade-offs through various techniques!

Perfect summary! This understanding of design trade-offs positions you for success in power management.

Introduction & Overview

Read summaries of the section's main ideas at different levels of detail.

Quick Overview

Standard

Design trade-offs in power management highlight the need for optimized strategies that balance performance with energy efficiency in CMOS and FinFET designs. Techniques such as DVFS, power gating, clock gating, and multi-Vt design can significantly reduce power consumption but may introduce challenges like increased latency and complexity. The best practice recommends combining these approaches across different architectural layers for maximum effectiveness.

Detailed

Design Trade-Offs and Best Practices

This section addresses the crucial design trade-offs in power management specific to CMOS and FinFET technologies.

Key Strategies and Their Trade-Offs

- Lower Vdd (DVFS):

- Benefit: Saves dynamic power during operations.

- Trade-Off: It may potentially reduce system performance, particularly during high-demand tasks.

- Power Gating:

- Benefit: Effectively eliminates leakage power when components are idle, ensuring higher efficiency.

- Trade-Off: It introduces challenges concerning wake-up latency and the complexity of routing power signals.

- Clock Gating:

- Benefit: Reduces dynamic switching power by disabling clocks to inactive modules, leading to energy savings.

- Trade-Off: The addition of logic for clock gating necessitates verification which can increase design timelines.

- Multi-Vt Design:

- Benefit: Manages leakage current selectively by using different threshold voltages for various circuit paths, optimizing performance and power usage.

- Trade-Off: It can complicate timing closure in the design process.

- Fine-Grain Domains:

- Benefit: Provides maximized flexibility in power management across different system components.

- Trade-Off: Increases design and test overhead, complicating system integration.

Best Practice Recommendation

The suggested best practice is to combine strategies like DVFS, clock gating, and power gating at various layers of the architecture (e.g., block, core, chip) to achieve optimal power efficiency alongside maintained performance levels. This multifaceted approach allows engineers to tailor solutions to the specific needs of their designs, ensuring that energy efficiency does not come at the cost of operational capability.

Youtube Videos

Audio Book

Dive deep into the subject with an immersive audiobook experience.

Lowering Voltage with DVFS

Chapter 1 of 6

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Lower Vdd Saves dynamic power May reduce performance (DVFS)

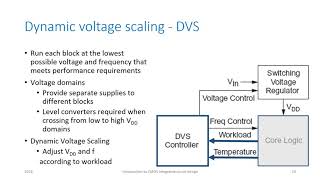

Detailed Explanation

Dynamic Voltage and Frequency Scaling (DVFS) is a technique used to lower the voltage (Vdd) and frequency during operation when the demand is low. This helps in saving dynamic power, which is the power consumed during the switching of transistor states. However, decreasing voltage may lead to reduced performance because the processing speed can slow down.

Examples & Analogies

Think of DVFS like running a car at a lower speed in a fuel-efficient mode. If you drive slower, you'll save gas, but it takes longer to reach your destination. In terms of electronics, the 'destination' is completing tasks efficiently.

Using Power Gating

Chapter 2 of 6

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Power Gating Eliminates leakage in idle Wake-up latency and routing

Detailed Explanation

Power gating is a method wherein power is completely cut off to certain parts of a circuit when they are not in use. This strategy effectively eliminates leakage current, which is the power lost in components that are idle. However, this technique introduces some challenges, such as longer wake-up times when those components are needed again and added complexity in the routing of power lines.

Examples & Analogies

Imagine turning off a room in your house when you're not using it. The room doesn't consume electricity (no leakage), but when you want to use it again, you need to turn the lights and heating back on, which takes a little time. Similarly, electronics 'wake up' from power gating, leading to some delay.

Implementing Clock Gating

Chapter 3 of 6

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Clock Gating Cuts dynamic switching Added logic and power verification

Detailed Explanation

Clock gating is a technique that turns off the clock signal to inactive circuit blocks, thus stopping unnecessary switching activity. This helps in reducing dynamic power consumption since the power used during switchings is significant. However, this method requires additional logical circuits to control the gating and also needs thorough verification to ensure that the design functions correctly without unintended issues.

Examples & Analogies

Consider clock gating like pausing a video game when you step away. When you pause, the game stops consuming resources (energy), but if you want to pause in a way that saves your progress, your console needs certain programs running to manage this.

Benefits and Complexity of Multi-Vt Design

Chapter 4 of 6

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Multi-Vt Design Controls leakage Timing closure complexity selectively

Detailed Explanation

Multi-threshold voltage (Multi-Vt) design employs transistors with different threshold voltages across the circuit to selectively control leakage power. Using high-threshold (high-Vt) transistors in non-critical paths helps reduce leakage, while low-threshold (low-Vt) transistors are used where speed is essential. This technique, however, adds complexity to the timing closure process, that is, ensuring that circuit signals meet timing requirements.

Examples & Analogies

Think of Multi-Vt like using different types of water-saving fixtures in your home. You install low-flow faucets in areas where quick water delivery is needed while using regular faucets elsewhere to save more water (or leakage) where it's less critical. However, ensuring all these fixtures operate in harmony requires thoughtful installation.

Advantages of Fine-Grain Power Domains

Chapter 5 of 6

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Fine-Grain Maximize flexibility Increases design/test overhead

Detailed Explanation

Fine-grain power domains refer to dividing a chip into many smaller sections, each with its own power control. This allows for maximum flexibility in managing power usage as different parts of a chip can be powered down individually. However, the trade-off is that this increases design complexity and testing overhead, as managing and verifying all these different sections can be more challenging.

Examples & Analogies

Imagine a large hotel where different floors can independently control their lights. This setup allows for energy savings when floors are unoccupied, but the hotel staff must ensure that each floor's system operates correctly, which adds to their tasks.

Best Practices for Power Management

Chapter 6 of 6

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Best practice: Combine DVFS + clock gating + power gating at different layers (block, core, chip) for optimal results.

Detailed Explanation

The best practice in power management is to implement a combination of techniques, including DVFS, clock gating, and power gating, across various layers of the design, such as at the block, core, and chip levels. This multi-faceted approach allows for more effective power savings, optimizing energy efficiency without sacrificing performance.

Examples & Analogies

Consider this like a layered strategy in a game: using various tactics like stealth (DVFS), tools to minimize noise (clock gating), and energy-efficient gadgets (power gating) allows a gamer to progress smoothly through challenges without alerting enemies (reducing wasted energy). Each tactic is effective individually, but combined, they create a much greater impact.

Key Concepts

-

Balancing Power and Performance: A crucial aspect of power management involving trade-offs between reduced power consumption and maintaining performance levels.

-

Effective Techniques: Utilizing methods like DVFS, power gating, and clock gating strategically to enhance power efficiency while managing complexities.

-

Best Practices: Combining various power management strategies across different architectural layers for optimal energy efficiency.

Examples & Applications

Using DVFS in mobile device applications to save battery life while ensuring adequate processing capability under varying workloads.

Employing power gating techniques in integrated circuits to minimize leakage current during idle operations, ensuring optimal energy efficiency.

Memory Aids

Interactive tools to help you remember key concepts

Rhymes

If you want power savings so bright, remember to dim before the night!

Stories

Imagine a sleeping giant (power gating); when awake, it roars; when idle, it remains silent, saving its energy for when needed.

Memory Tools

Remember 'Powers GONE when idling, wait LONG' for power gating.

Acronyms

DVFS

'Dynamic Voltage Feet Save' for efficiency in computing.

Flash Cards

Glossary

- DVFS

Dynamic Voltage and Frequency Scaling is a power management technique that dynamically adjusts the voltage and frequency in relation to the workload.

- Power Gating

A power management technique whereby power is cut off to idle components to eliminate leakage current.

- Clock Gating

A method to reduce dynamic power by disabling the clock signals to inactive modules.

- MultiVt Design

A design approach using multiple threshold voltages to control leakage current selectively, optimizing performance in various circuit paths.

- FineGrain Domains

Designs that allow for independent power management of smaller functional blocks, providing greater control over power consumption.

Reference links

Supplementary resources to enhance your learning experience.