PMOS Transistor Behavior

Enroll to start learning

You’ve not yet enrolled in this course. Please enroll for free to listen to audio lessons, classroom podcasts and take practice test.

Interactive Audio Lesson

Listen to a student-teacher conversation explaining the topic in a relatable way.

Understanding PMOS Characteristics

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Today, we're going to discuss PMOS transistors! To start, does anyone know what type of channel a PMOS transistor has?

Is it a p-type channel?

Exactly! PMOS devices have a p-type channel. Now, can someone tell me what happens when a negative gate-source voltage is applied?

The transistor turns on if the gate voltage is lower than the source voltage!

Great job! That leads us to the threshold voltage. Can anyone define what the threshold voltage is for a PMOS transistor?

It's the minimum negative gate voltage needed to conduct.

Exactly! And remember, VGS must be less than Vth for the PMOS to operate. Let's summarize: PMOS transistors are off when VGS is above Vth and on when below it.

Exploring PMOS Operation Regions

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Now, we’ll uncover the operation regions of PMOS devices. There are three main regions: cutoff, linear, and saturation. Who can explain the cutoff region?

In the cutoff region, if VGS is more positive than Vth, the PMOS is off.

Correct! In this state, no current flows. Now what about the linear region?

The PMOS acts like a resistor here, right? Current is proportional to VDS.

Absolutely! If VGS is negative enough and VDS is small, we see linear current flow. And as for saturation—what happens there?

In the saturation region, current is mostly controlled by VGS and doesn't depend on VDS much.

Excellent! To recap, PMOS operates in three regions: cutoff (off), linear (like a resistor), and saturation (current primarily from VGS).

Understanding I-V Characteristics

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Now let’s talk about PMOS I-V characteristics. The behavior in saturation can be summarized in an equation. What do you think is the primary equation for PMOS drain current in saturation?

It’s ID equals 1/2 Kp times (VSG minus |Vth|) squared times (1 plus λVDS).

Absolutely correct! Let’s break that down. Kp is a process constant. Can someone recall what VSG represents?

It's the source-gate voltage, which is negative for PMOS.

Right! And what's significant about the λ term in the equation?

The λ term shows how the current varies with VDS due to channel-length modulation.

Exactly! Recapping, PMOS operates through three regions with a key I-V equation governing its behavior.

Introduction & Overview

Read summaries of the section's main ideas at different levels of detail.

Quick Overview

Standard

PMOS transistors are p-type devices that conduct current when the gate-source voltage is negative and below a specific threshold. They exhibit three main operation regions: cutoff, linear, and saturation, each with distinct current behavior patterns important for integrated circuit design.

Detailed

PMOS Transistor Behavior

PMOS transistors, integral to CMOS technology, feature a p-type channel and operate based on a negative gate-source voltage (VGS). To understand the behavior of PMOS transistors, it is essential to consider the following aspects:

1. Threshold Voltage (Vth)

The threshold voltage (Vth) is defined as the minimum negative gate-source voltage required to turn the PMOS device on. In this case, conduction occurs when VGS is less than Vth (which is generally negative).

2. Operation Regions

PMOS transistors have three key operational regions:

- Cutoff Region: In this state, if VGS is greater than Vth (less negative), the transistor is off, and no current flows.

- Linear (Ohmic) Region: This occurs when VGS is suitably negative, and the drain-source voltage (VDS) is small, leading the PMOS to act like a resistor with linearly proportional current response.

- Saturation Region: Here, when VGS is sufficiently negative and VDS is large, the PMOS enters saturation. In this region, the current is primarily defined by VGS and is nearly independent of VDS.

3. I-V Characteristics

The drain current (ID) in saturation for PMOS can be described by the equation:

ID = 1/2 Kp (VSG - |Vth|)^2 (1 + λVDS)

Where:

- Kp is a process-dependent constant,

- λ is the channel-length modulation factor,

- VSG is the source-gate voltage (negative for PMOS),

- |Vth| represents the magnitude of the threshold voltage.

Understanding these characteristics is crucial for designing and using CMOS circuits effectively, as PMOS devices function symbiotically with NMOS counterpart devices to yield minimal static power consumption in applications.

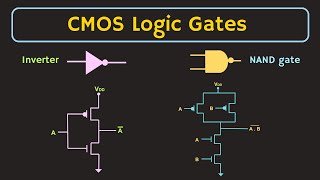

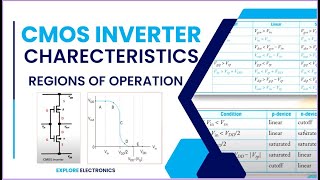

Youtube Videos

Audio Book

Dive deep into the subject with an immersive audiobook experience.

Introduction to PMOS Transistor

Chapter 1 of 4

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

A PMOS transistor has a p-type channel and is controlled by a negative gate-source voltage. The PMOS transistor conducts current when the gate voltage is lower than the source voltage (i.e., VGS < Vth).

Detailed Explanation

A PMOS transistor operates using a p-type channel, which allows it to conduct current when a negative voltage is applied to the gate in relation to the source. This means that if the voltage at the gate is lower than that at the source, the PMOS will be 'on' and allow current to flow.

Examples & Analogies

Think of a PMOS transistor like a door controlled by a pressure sensor. If the pressure on the sensor (akin to the voltage at the gate) is less than a certain threshold, it allows the door (current flow) to open. However, if the pressure is greater, the door remains closed.

Threshold Voltage (Vth)

Chapter 2 of 4

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Similar to NMOS, the PMOS transistor has a threshold voltage, which is typically negative for PMOS. The transistor turns on when VGS is sufficiently negative (below the threshold voltage).

Detailed Explanation

The threshold voltage (Vth) in a PMOS transistor is crucial for its operation. It defines the minimum gate-source voltage required to switch the transistor from 'off' to 'on'. For PMOS, this voltage is negative, meaning that the gate must be at a lower potential than the source to create a conductive channel.

Examples & Analogies

Imagine a slide that only allows someone to go down when the person stands on a platform at a level lower than the slide. The height of the platform represents the threshold voltage; if someone stands too high (less negative), the slide will not work.

Operation Regions of PMOS Transistor

Chapter 3 of 4

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

The PMOS transistor has three operation regions: Cutoff, Linear/Ohmic, and Saturation.

Detailed Explanation

Understanding the three operation regions of a PMOS transistor is essential. In the cutoff region, the PMOS is off and no current flows when VGS is above Vth. In the linear region, it behaves like a resistor and allows current to flow linearly with VDS when VGS is sufficiently negative and VDS is small. The saturation region occurs when VGS remains negative enough but VDS is large, making current primarily dependent on VGS.

Examples & Analogies

Think of a faucet. In the cutoff region, when you don't twist the handle (VGS above Vth), no water flows (no current). As you gradually twist it (move into the linear region), water flows out more steadily. Finally, if you twist it all the way (enter saturation), water flows out freely without much difference in the pressure of the pipe behind it.

I-V Characteristics of PMOS Transistor

Chapter 4 of 4

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

The drain current (ID) in the saturation region for PMOS is given by: ID = 1/2 Kp(VSG − |Vth|)²(1 + λVDS).

Detailed Explanation

This formula explains how the drain current in a PMOS transistor is calculated in the saturation region. It involves several parameters: Kp, which is a constant specific to PMOS transistors; VSG, the voltage from the source to the gate; and the term that includes |Vth|, the absolute value of the threshold voltage, which affects current flow. The equation describes how variations in these parameters influence how much current can flow through the transistor.

Examples & Analogies

You can think of this equation like a recipe for making orange juice. Kp is like the amount of oranges you need (a constant scaled to the specific juice), VSG might represent the ripeness of the oranges, and |Vth| shows the effects of using quality fruits! By adjusting these factors, you can determine how much juice (current) you can get out.

Key Concepts

-

PMOS Transistor: A p-type transistor that conducts when the gate voltage is more negative than a threshold.

-

Threshold Voltage: The negative voltage at which the PMOS starts to conduct.

-

Operation Regions: Cutoff, linear, and saturation are the three primary modes of PMOS operation.

-

I-V Characteristics: The equation describing current behavior in saturation based on gate-source voltage.

-

Channel-Length Modulation: Effect that influences current flow due to varying drain-source voltage.

Examples & Applications

A PMOS transistor connects in CMOS logic gates to perform switching based on input high or low.

In power management circuits, PMOS transistors help reduce power consumption by turning off during idle states.

Memory Aids

Interactive tools to help you remember key concepts

Rhymes

In PMOS so bright and bold, negative volts are what we're told, when VGS is low, current will flow, in operation regions to behold.

Stories

Imagine a switch that only turns on when given a negative push. The PMOS transistor waits patiently, only allowing power to flow when it gets that needed negativity from its gate.

Memory Tools

Remember the word 'CAP' for PMOS regions: C for Cutoff, A for Active (linear), and P for Saturation.

Acronyms

Use the acronym 'VG=TH' to remember

'V' for VGS

'G' for Gate

'=' for conduction condition

and 'TH' for Threshold negative.

Flash Cards

Glossary

- PMOS Transistor

A type of MOSFET that uses a p-type channel and conducts when the gate-source voltage is negative.

- Threshold Voltage (Vth)

The minimum gate-source voltage required for the PMOS to conduct current, typically negative.

- Operation Regions

The distinct regions (cutoff, linear, saturation) of PMOS behavior depending on gate-source and drain-source voltages.

- IV Characteristics

The current-voltage relationship for PMOS devices, described by an equation in the saturation region.

- ChannelLength Modulation

A phenomenon where the effective length of the conductive channel alters with the applied drain-source voltage.

Reference links

Supplementary resources to enhance your learning experience.