Pipeline Hazards

Enroll to start learning

You’ve not yet enrolled in this course. Please enroll for free to listen to audio lessons, classroom podcasts and take practice test.

Interactive Audio Lesson

Listen to a student-teacher conversation explaining the topic in a relatable way.

Data Hazards

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Today, we're discussing data hazards, which can really affect the performance of our processors. Can anyone tell me what they think a data hazard is?

Is it when one instruction depends on the result of another instruction?

Exactly! Data hazards occur when one instruction relies on the data from another instruction that hasn't finished executing yet. There are three types of data hazards: Read-after-Write, Write-after-Read, and Write-after-Write. Let's break these down. First, who can define Read-after-Write?

I think it's when an instruction tries to read data that is not yet written by a prior instruction.

Correct! This type of hazard is often called a true dependency. Now, what about Write-after-Read?

That would be when a later instruction tries to write data before an earlier one has read it?

Yes, good job! Lastly, let’s finish with Write-after-Write. Can anyone summarize that one?

It's when two instructions try to write to the same location, right?

Exactly! So, remember the acronym RAW for Read-after-Write, WAR for Write-after-Read, and WAW for Write-after-Write. They're key to understanding data hazards.

Control Hazards

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Next, let's talk about control hazards. Who can tell me what a control hazard is or give an example?

Isn't that when there's a branch or jump in the program?

Exactly! Control hazards occur due to branches or jumps when the processor is unsure which instruction to fetch next. Has anyone heard of branch prediction?

Yes, it's like guessing what the next instruction will be!

Right! Branch prediction uses algorithms to make educated guesses to reduce the delays caused by control hazards. What are the implications if our prediction is wrong?

The pipeline might need to flush instructions, wasting time!

Spot on! Control hazards emphasize the importance of efficient instruction flow in pipelining systems.

Structural Hazards

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Finally, let's discuss structural hazards. Can anyone explain what they are?

Aren't they problems that occur when there aren't enough resources to handle multiple instructions at once?

Correct! Structural hazards happen when hardware resources are insufficient, leading to conflicts. What can we do to prevent these hazards?

Maybe enhance hardware resources or redesign the pipeline?

Exactly! By improving the hardware or optimizing design, we can minimize structural hazards. Let’s summarize what we've learned about all types of hazards today.

Introduction & Overview

Read summaries of the section's main ideas at different levels of detail.

Quick Overview

Standard

This section explores the various pipeline hazards, including data hazards, control hazards, and structural hazards. Each type presents unique challenges and requires specific strategies to minimize their impact on processor performance.

Detailed

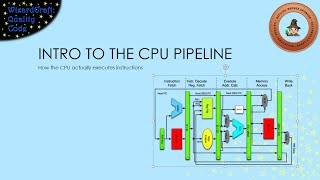

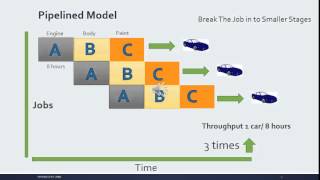

Pipeline Hazards

While pipelining significantly boosts the performance of processors, it also introduces several challenges known as pipeline hazards. These hazards can prevent the smooth execution of instructions, and to maintain system efficiency, they must be identified and addressed. The main types of pipeline hazards include:

1. Data Hazards

Data hazards occur when instructions that are close together in execution depend on the same data. There are three primary subtypes of data hazards:

- Read-after-Write (RAW): Also known as true dependency, it occurs when an instruction attempts to read data that is not yet available because a previous instruction is still writing it.

- Write-after-Read (WAR): This happens when an instruction tries to write data to a location before an earlier instruction has read it, leading to potential errors.

- Write-after-Write (WAW): This occurs when two instructions write to the same location, and the order of writes can lead to inconsistent data.

2. Control Hazards

Also known as branch hazards, these occur during branch instructions when the processor does not know which instruction to fetch next due to a possible change in the control flow of the program. Branch prediction strategies can be employed to minimize delays caused by these hazards.

3. Structural Hazards

Structural hazards arise from insufficient hardware resources to support all the stages of the pipeline for all instructions at the same time, such as inadequate ALUs or memory access ports. These limitations can cause conflicts and stalls in the execution of instructions.

Understanding these hazards is critical for developing techniques to mitigate their effects and ensure that pipelined architectures operate efficiently.

Youtube Videos

Audio Book

Dive deep into the subject with an immersive audiobook experience.

Introduction to Pipeline Hazards

Chapter 1 of 4

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

While pipelining significantly improves performance, it introduces several challenges, known as pipeline hazards, which need to be addressed to maintain the efficiency of the system.

Detailed Explanation

Pipeline hazards are issues that arise in a pipelined processor when there are dependencies or conflicts among instructions that are being processed simultaneously. These hazards can prevent the processor from achieving optimal performance, highlighting the importance of addressing them effectively.

Examples & Analogies

Consider a busy restaurant kitchen where multiple orders (instructions) need to be prepared at once. If one chef (stage) needs an ingredient that another chef is currently using (data dependency), it can slow down the whole operation, similar to how pipeline hazards can slow down a processor.

Data Hazards

Chapter 2 of 4

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Data Hazards: Occur when instructions that are close together depend on the same data. There are three types:

- Read-after-Write (RAW) hazard: Also known as a true dependency, occurs when an instruction needs data that is being written by a previous instruction.

- Write-after-Read (WAR) hazard: Occurs when a later instruction tries to write data to a location before an earlier instruction has read it.

- Write-after-Write (WAW) hazard: Occurs when two instructions write to the same register or memory location.

Detailed Explanation

Data hazards arise when multiple instructions operate on the same data in a way that affects their execution order. The types include:

1. RAW (Read After Write): This occurs when an instruction needs data that another instruction is still writing.

2. WAR (Write After Read): This happens when a subsequent instruction writes to a location before an earlier instruction has read from it.

3. WAW (Write After Write): This is when two instructions attempt to write to the same register or memory location, causing conflicts.

Examples & Analogies

Imagine a relay race where one runner (instruction) needs to pass the baton (data) to another runner. If the second runner starts running before receiving the baton, or if they both try to take the baton at the same time, it leads to confusion and delays, similar to how data hazards affect instruction execution in a pipeline.

Control Hazards

Chapter 3 of 4

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Control Hazards: Occur when there is a branch or jump in the program, and the processor does not know which instruction to fetch next.

- Branch Prediction: Using algorithms to predict the direction of branches to avoid delays.

Detailed Explanation

Control hazards arise during the execution of branch instructions, where the flow of instructions can change based on certain conditions. The processor may not know which instruction to execute next until the branch is resolved. Branch prediction is a technique used to guess the outcome of a branch to keep the pipeline filled and reduce stalls.

Examples & Analogies

Think of a driver's navigation system that must decide which route to take at a fork in the road (branch). If the system predicts the wrong turn, the driver may have to backtrack, similar to how a processor wastes time fetching the wrong instruction after a branch is encountered.

Structural Hazards

Chapter 4 of 4

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Structural Hazards: Occur when the hardware resources are insufficient to support all the instructions in the pipeline at once, such as not having enough ALUs or memory access ports.

Detailed Explanation

Structural hazards occur when multiple instructions require the same hardware resource simultaneously, leading to conflicts. For example, if there are not enough Arithmetic Logic Units (ALUs) to perform computations for all instructions in the pipeline, some instructions will have to wait.

Examples & Analogies

Consider a busy library where multiple students (instructions) want to access the same computer (hardware resource) at the same time. If the library only has a limited number of computers, some students will have to wait, causing delays—just like structural hazards in a processor.

Key Concepts

-

Data Hazards: Occur when instructions depend on the same data, leading to potential execution conflicts.

-

Read-after-Write Hazard: True dependency where an instruction needs the data being written by another instruction.

-

Control Hazards: Result from branches and jumps in instruction flow that can slow down execution.

-

Structural Hazards: Arise when insufficient hardware resources lead to execution conflicts in the pipeline.

Examples & Applications

If instruction I1 writes to a register and instruction I2 reads from the same register immediately after, it causes a Read-after-Write hazard.

A conditional branch instruction that results in incorrect predictions can lead to stalls in instruction execution, causing delays.

Memory Aids

Interactive tools to help you remember key concepts

Rhymes

In a pipeline race, data must place, / Read after write, we need the right space.

Stories

Imagine a chef in a busy kitchen (pipeline), where certain tasks (instructions) depend on others to be completed before they can start. If one chef needs a spicy sauce (data) while another is still preparing it, the kitchen gets delayed, just like how a data hazard slows down a pipeline.

Memory Tools

Remember 'RAW, WAR, and WAW' to keep track of data hazards: Read-After-Write, Write-After-Read, Write-After-Write.

Acronyms

Control hazards mean 'Branches Cause Pipelining Woes'—B.C.P.W.

Flash Cards

Glossary

- Data Hazards

Challenges in pipelining when instructions depend on the same data.

- ReadafterWrite (RAW) Hazard

A true dependency where an instruction needs data that is being written by a prior instruction.

- WriteafterRead (WAR) Hazard

Occurs when a later instruction writes data to a location before an earlier instruction has read it.

- WriteafterWrite (WAW) Hazard

Happens when two instructions write to the same register or memory location.

- Control Hazards

Hazards caused by branches or jumps in the program affecting instruction fetching.

- Structural Hazards

Result from insufficient hardware resources to support multiple instructions in the pipeline simultaneously.

- Branch Prediction

Algorithms that predict the outcome of branches to minimize control hazards.

Reference links

Supplementary resources to enhance your learning experience.