Pipeline Stalls and Forwarding

Enroll to start learning

You’ve not yet enrolled in this course. Please enroll for free to listen to audio lessons, classroom podcasts and take practice test.

Interactive Audio Lesson

Listen to a student-teacher conversation explaining the topic in a relatable way.

Understanding Pipeline Stalls

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Today, we're going to talk about pipeline stalls. Can anyone tell me what happens when an instruction in a pipeline gets delayed due to a data hazard?

Isn't that when the instruction has to wait for data from a previous instruction?

Exactly! That delay is what we refer to as a pipeline stall. It prevents other instructions from getting executed, resulting in lower throughput. Can anyone guess why stalling might be a problem?

It slows down the processing speed?

Correct! Each stall results in wasted clock cycles, which reduces the efficiency of the pipeline. So, stalling is a significant challenge for pipelined architectures.

How do processors deal with stalls?

Good question! We'll discuss techniques like forwarding shortly, but first, let’s recap: a pipeline stall happens due to a hazard and affects overall processing efficiency.

Forwarding Techniques

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Now, let’s talk about a technique called forwarding, also known as data bypassing. Can anyone describe what it does?

Doesn't it let data move directly between pipeline stages without going back to the registers?

That's correct! Forwarding allows us to access data from one pipeline stage to another immediately, thus minimizing the need for stalls. Why do you think this is beneficial?

It means instructions can keep processing without waiting, so we maintain a high throughput.

Exactly! It effectively reduces idle time in the pipeline. Can someone explain a situation where forwarding might be used?

If instruction B needs the result of instruction A before it’s written back, forwarding can provide that result instead of waiting.

Excellent example! Just to summarize, forwarding helps pass data along the pipeline quickly, reducing stalls and enhancing efficiency.

Pipeline Flush after Branch Prediction

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Let’s now address what happens when we encounter a branch prediction error. What do you think occurs in our pipeline then?

I think we have to discard the wrong instructions that we've fetched while waiting for the correct one.

That's right! This process is called a pipeline flush. It’s sometimes necessary when the processor mispredicts a branch direction. Why do you think flushing is a costly operation?

Because all those instructions we fetched become wasted effort, and we lose time.

Exactly! This shows how important accurate branch prediction is in maintaining pipeline efficiency. Let’s review: a flush clears incorrect instructions due to mispredictions, leading to a performance cost.

Introduction & Overview

Read summaries of the section's main ideas at different levels of detail.

Quick Overview

Standard

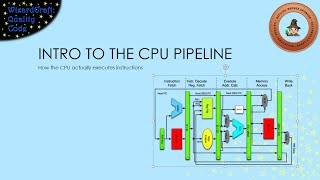

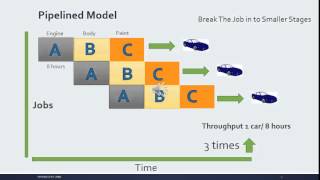

In this section, the concept of pipeline stalls and forwarding is explored, highlighting how they are implemented to mitigate data hazards and maintain smooth instruction execution in pipelined CPU architectures. Forwarding allows direct data transfer between pipeline stages to resolve hazards without unnecessary delays.

Detailed

Pipeline Stalls and Forwarding

The section outlines crucial methodologies used in modern processors to address pipeline hazards, specifically focusing on pipeline stalls and forwarding.

Pipeline Stalls

A pipeline stall occurs when a data hazard prevents an instruction from progressing, requiring the processor to introduce a delay. This can happen when an instruction is dependent on a result from a preceding instruction that hasn't yet completed.

Forwarding (Data Forwarding)

Also known as data bypassing, forwarding is a technique employed to improve pipeline efficiency. Instead of waiting for data to be written back to registers before making it available to subsequent instructions, forwarding allows data to be passed directly from one stage of the pipeline to another. This technique significantly reduces the number of stalls, thus enhancing overall system performance.

Pipeline Flush

Another related concept is the pipeline flush, which occurs in the event of an incorrect branch prediction. If a prediction fails, the system must discard all subsequent instructions that were incorrectly fetched, requiring a pipeline flush to fetch the correct instructions.

These techniques demonstrate how careful design choices can compensate for potential hazards in pipelining, ensuring that processors can maintain high throughput and efficiency.

Youtube Videos

Audio Book

Dive deep into the subject with an immersive audiobook experience.

Pipeline Stalls

Chapter 1 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

A stall occurs when a hazard prevents an instruction from continuing. The processor introduces a delay to resolve the issue.

Detailed Explanation

A pipeline stall happens when the next instruction cannot proceed because it depends on the result of a previous instruction that has not yet completed. This can cause the pipeline to pause, resulting in a delay. The processor essentially waits until it can receive the necessary data or resource to continue processing. Think of this as a line of cars at a traffic light; if one car (the instruction) can't move forward because it waits for another car to clear the intersection (results from a previous instruction), the cars behind it must also stop until the first one moves.

Examples & Analogies

Imagine a queue at a coffee shop where one person orders a complex drink. If the barista has to pause to prepare this order, other customers waiting for their simpler drinks must wait longer than necessary. This is similar to how pipeline stalls work, where one instruction's complexity can hold up the execution of others.

Forwarding (Data Forwarding)

Chapter 2 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Also known as data bypassing, this technique allows data to be passed directly from one pipeline stage to another to resolve data hazards without waiting for the data to be written back to registers.

Detailed Explanation

Forwarding, or data bypassing, is a method used to minimize the delays caused by stalls. Instead of waiting for an instruction to complete its process and write back the data to memory, the data is sent directly from one stage of the pipeline to where it's needed. For instance, if one instruction requires data from a previous instruction that is still being executed, the pipeline can 'forward' the data before completion, thus allowing the next instruction to proceed without waiting.

Examples & Analogies

Think of forwarding like passing a note in a classroom. If you need to know an answer for your homework but your friend hasn’t finished writing it down yet, you can pass them a note to ask for the answer directly from what they remember, without waiting for them to finish. This helps you continue your work promptly instead of waiting and falling behind.

Pipeline Flush

Chapter 3 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

If a branch prediction is incorrect, the pipeline must be flushed, and all subsequent instructions are discarded to fetch the correct instruction.

Detailed Explanation

A pipeline flush occurs when the processor realizes that it has made an incorrect prediction about which instruction to fetch next—typically due to branching decisions in the code. When this happens, all the instructions that were fetched based on the incorrect prediction need to be removed from the pipeline, and the correct instruction must then be fetched. This process can incur a performance penalty since the pipeline must be cleared and refilled.

Examples & Analogies

Imagine you are baking a cake and realized halfway through that you forgot to add a key ingredient. Instead of continuing and baking the cake incorrectly, you decide to start again from scratch, discarding everything you did. This is similar to a pipeline flush, where the processor must discard the incorrect instructions and start over to ensure the outcome is correct.

Key Concepts

-

Pipeline Stalls: Delays caused by hazards blocking instruction execution.

-

Forwarding: Technique for directly passing data between pipeline stages.

-

Pipeline Flush: The process of discarding instructions due to incorrect branch predictions.

Examples & Applications

Example of a data dependency where if instruction 2 needs the outcome of instruction 1, a pipeline stall occurs.

If the processor has a branch that is mispredicted, the pipeline must discard incorrect instructions and fetch new ones, leading to flushing.

Memory Aids

Interactive tools to help you remember key concepts

Rhymes

When data's in the pipe but can't find its spot, a stall will occur, which we surely do not want!

Stories

Imagine a factory assembly line where one worker (instruction) waits for a part (data) from another. If the part isn't ready, the whole line (pipeline) halts (stalls) until it arrives. To fix this, a manager (forwarding) allows the next worker to use the part from the previous position instead of waiting, keeping the line moving.

Memory Tools

S-F-F (Stall - Forwarding - Flush) to remember the three key concepts: Pipeline Stall, Forwarding, and Pipeline Flush.

Acronyms

Remember all hazards with DCB

Data hazards

Control hazards

and Structural hazards.

Flash Cards

Glossary

- Pipeline Stall

A delay that occurs in a pipelined processor when a hazard prevents an instruction from continuing execution.

- Forwarding

A technique that allows data to be passed directly between pipeline stages to resolve hazards and minimize stalls.

- Pipeline Flush

The process of discarding subsequent instructions in the pipeline when there is an incorrect branch prediction.

Reference links

Supplementary resources to enhance your learning experience.