Pipeline Stages

Enroll to start learning

You’ve not yet enrolled in this course. Please enroll for free to listen to audio lessons, classroom podcasts and take practice test.

Interactive Audio Lesson

Listen to a student-teacher conversation explaining the topic in a relatable way.

Introduction to Pipeline Stages

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Today, we will talk about pipeline stages in modern computer processors. Can anyone tell me why pipelining is important?

Is it to speed up the processing of instructions?

Exactly! Pipelining allows for multiple instructions to be processed at different stages simultaneously, which greatly improves throughput. Let’s break down the stages of pipelining. First, we have the Instruction Fetch stage.

What happens in the Instruction Fetch stage?

In the IF stage, the instruction is fetched from memory. It’s like taking a book off a shelf so you can read it! Next, we move on to the Instruction Decode stage.

What is the purpose of decoding the instruction?

The decode stage translates that instruction into something the processor can understand and execute. It's like understanding a recipe before you start cooking! Can anyone summarize what we've discussed so far?

We fetch instructions and then decode them to understand what to do next!

Great job! Now let’s dive into the Execute stage.

Execution and Memory Access Stages

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

After decoding, the instruction moves on to the Execute stage. What happens there?

The operation specified by the instruction is performed, right?

Correct! This is where the processor does the actual work, like performing calculations. Then comes the Memory Access stage. Can anyone explain its function?

That’s when the instruction can read data from or write data to memory if needed.

Exactly! This stage is essential for instructions that need data to complete their operations, such as loading numbers for arithmetic calculations. Now let’s wrap up with the Write Back stage.

What happens in the Write Back stage?

In the WB stage, the results of the computation are written back to the processor registers. Summarize these stages for me!

We execute the instruction, access memory if needed, and then write the results back.

Well done! These stages, when combined, create the efficient system of pipelining.

Benefits of Pipelining

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Let’s look at how these stages work together to enhance processor performance. Can anyone give me an example of why overlapping stages is beneficial?

It lets the CPU work on multiple instructions at once, right?

Absolutely! By having multiple instructions in the pipeline, the CPU can achieve a higher instruction throughput. What does that mean for performance?

It means we can process more instructions in less time!

Exactly! This efficiency is a key driver behind modern processor design. Can you summarize the main benefits of pipelining?

We get increased throughput and improved efficiency by overlapping instruction processing.

Fantastic! Remember, every stage in the pipeline is crucial for ensuring that we maximize our computational resources.

Introduction & Overview

Read summaries of the section's main ideas at different levels of detail.

Quick Overview

Standard

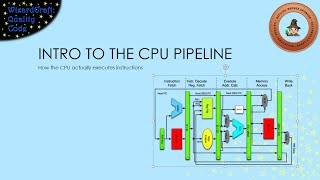

This section details the five key stages of instruction execution in pipelining: Instruction Fetch (IF), Instruction Decode (ID), Execute (EX), Memory Access (MEM), and Write Back (WB). Each stage operates concurrently, allowing for overlapping instruction execution and significantly boosting processor throughput.

Detailed

Pipeline Stages

Pipelining is a crucial technique in the design of modern processors, aimed at improving the overall instruction throughput. In this section, we cover the five main stages of the pipeline that help achieve this goal:

- Instruction Fetch (IF): The process begins with fetching the instruction from memory that needs to be executed.

- Instruction Decode (ID): Once fetched, the instruction is decoded to understand what operation is required, effectively translating machine code into actionable commands.

- Execute (EX): In this stage, the processor carries out the actual operation specified by the instruction, which may involve arithmetic computations or logical processing.

- Memory Access (MEM): Should the instruction require it, this stage involves reading data from or writing data to memory, further facilitating the command's execution.

- Write Back (WB): Finally, the results from the execution are written back into the register file, completing the instruction’s cycle.

These stages are not executed sequentially; rather, multiple instructions can occupy different stages of the pipeline simultaneously, thereby enhancing processing efficiency and throughput. This organizational structure is foundational to how modern processors achieve rapid execution of multiple instructions and is significant for increasing computational speed.

Youtube Videos

Audio Book

Dive deep into the subject with an immersive audiobook experience.

Overview of Pipeline Stages

Chapter 1 of 7

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

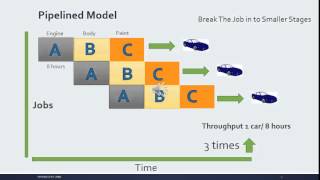

Pipelining breaks the execution of instructions into several stages. Each stage performs a different part of the instruction’s execution.

Detailed Explanation

Pipelining is like an assembly line in a factory where each worker (or stage) specializes in a specific task. Instead of completing one instruction before starting the next, pipelines allow different stages of multiple instructions to be processed at the same time. This way, the overall speed of executing instructions increases, as multiple instructions are being worked on simultaneously.

Examples & Analogies

Imagine a restaurant kitchen where different chefs handle different tasks: one chef prepares ingredients, another cooks, and a third plates the food. Instead of one chef waiting until a dish is completely prepared before starting the next, all chefs work on different dishes at the same time, speeding up the meal preparation process.

Instruction Fetch (IF)

Chapter 2 of 7

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

● Instruction Fetch (IF): The instruction is fetched from memory.

Detailed Explanation

During the Instruction Fetch stage, the processor retrieves the instruction it needs to execute from the memory. This is the first step in the pipeline, where the next instruction to be executed is locked and prepared for processing. It’s crucial because if the wrong instruction is fetched or if fetching takes too long, the entire pipeline can stall.

Examples & Analogies

Think of this as a librarian fetching a book from the shelves. If the librarian goes to the wrong section or takes too long to grab the book, the readers, who are waiting for the book, are stuck waiting instead of immediately starting to read.

Instruction Decode (ID)

Chapter 3 of 7

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

● Instruction Decode (ID): The fetched instruction is decoded to determine what operation it requires.

Detailed Explanation

In the Instruction Decode stage, the processor analyzes the fetched instruction to understand what operation it needs to perform. This involves interpreting the opcode (the part of the instruction that tells the processor what to do) and the operands (the data the operation will work on). This stage is essential for ensuring that the correct operation is executed in the next stages.

Examples & Analogies

You can compare this stage to a chef reading a recipe. Before they start cooking, they need to understand what dish they are making (operation) and what ingredients they need (operands). If the chef misinterprets the recipe, the dish will not turn out right.

Execute (EX)

Chapter 4 of 7

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

● Execute (EX): The operation specified by the instruction is performed.

Detailed Explanation

In the Execute stage, the actual execution of the operation specified by the instruction takes place. This could involve performing arithmetic calculations, logical operations, or manipulating data as needed. This is often the most crucial stage, as it involves changing data based on commands given by previously decoded instructions.

Examples & Analogies

This stage can be likened to the chef cooking the food based on the instructions in the recipe. For example, if the recipe says to sauté vegetables, the chef would carry that out at this stage, transforming raw ingredients into something ready to eat.

Memory Access (MEM)

Chapter 5 of 7

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

● Memory Access (MEM): Data is read from or written to memory if required by the instruction.

Detailed Explanation

The Memory Access stage occurs when the instruction requires data that needs to be fetched from memory or needs to write data back to the memory. For instance, if an instruction involves loading a value from a variable or saving a computed result back into memory, this stage deals with those actions. This step is essential to ensure that the execution results are correctly saved and that all data is available for processing.

Examples & Analogies

Imagine the cook checking the pantry for spices (loading data) or putting leftovers away after preparing a meal (writing data). Both actions are dependent on what they need for cooking or ensuring everything is stored correctly.

Write Back (WB)

Chapter 6 of 7

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

● Write Back (WB): The result of the instruction is written back to the register file.

Detailed Explanation

The Write Back stage is where the results from the execution of the instruction are sent back to the registers, which are small storage locations within the processor. This allows the results to be quickly accessed by future instructions that may require them. It finalizes the current instruction's process and prepares the registers for the next set of operations.

Examples & Analogies

Think of this stage as a chef plating a dish once it’s cooked. The chef puts the food on a plate (register) so that it can be served (used in future instructions) to the customers (other processes in the CPU). This detail ensures that every stage of preparation has access to the final product.

Concurrent Work in the Pipeline

Chapter 7 of 7

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Each of these stages works concurrently in a pipeline, allowing multiple instructions to be in different stages at the same time.

Detailed Explanation

One of the significant advantages of pipelining is that it allows various instructions to be processed at different stages of execution concurrently. This concurrent work means that, ideally, one new instruction can be completed in every clock cycle, greatly increasing the overall throughput of the system. By using the pipeline effectively, overall execution time decreases, and efficiency improves.

Examples & Analogies

Consider a multi-lane highway where several cars (instructions) can travel in parallel. Each car is at a different part of the journey—some are on the entrance ramp (fetching), some are cruising on the highway (executing), and others are exiting to their destination (writing back). This setup ensures smooth and efficient travel instead of a single line waiting at traffic lights.

Key Concepts

-

Instruction Fetch: The first stage where instructions are retrieved from memory.

-

Instruction Decode: The second stage that decodes the fetched instruction.

-

Execute: The third stage where the operation asked by the instruction is performed.

-

Memory Access: The fourth stage that allows reading from and writing to memory.

-

Write Back: The final stage where results are stored back to registers.

Examples & Applications

During the Instruction Fetch stage, the CPU fetches the ADD instruction from memory.

In the Execute stage, the CPU performs the specified arithmetic operation, such as addition, based on the decoded instruction.

Memory Aids

Interactive tools to help you remember key concepts

Rhymes

In the pipeline, instructions flow, IF to ID, EX to show, MEM accesses, WB will glow!

Stories

Imagine a factory line where each worker specializes. The first worker fetches the materials (IF), the second interprets the order (ID), the third does the work (EX), the fourth handles the materials if needed (MEM), and the fifth puts the finished products on the shelf (WB).

Memory Tools

For the pipeline stages, remember 'I Do Even More Work'—Instruction, Decode, Execute, Memory Access, Write Back!

Acronyms

1) IF, 2) ID, 3) EX, 4) MEM, 5) WB represents the pipeline stages.

Flash Cards

Glossary

- Instruction Fetch (IF)

The first stage of the pipeline where an instruction is retrieved from memory for execution.

- Instruction Decode (ID)

The stage in the pipeline where the fetched instruction is decoded to understand what operation it requires.

- Execute (EX)

The stage in the pipeline where the specified operation of the instruction is carried out.

- Memory Access (MEM)

The stage where data is read from or written to memory, if required by the instruction.

- Write Back (WB)

The final stage where the results of the execution are written back to the register file.

Reference links

Supplementary resources to enhance your learning experience.