Design Metrics and Measures

Enroll to start learning

You’ve not yet enrolled in this course. Please enroll for free to listen to audio lessons, classroom podcasts and take practice test.

Interactive Audio Lesson

Listen to a student-teacher conversation explaining the topic in a relatable way.

Clock Cycle Time

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Let's start with clock cycle time. Can someone tell me what they think it means?

I think it's how long a clock signal takes to cycle.

Exactly! The clock cycle time determines how many instructions can be executed per second. It's measured in seconds or nanoseconds. Remember, a shorter clock cycle time means the CPU can perform more operations per second.

Can you give an example of how it impacts performance?

Certainly! For instance, if one CPU has a clock cycle time of 2 ns and another has 1 ns, the second CPU can theoretically execute twice as many instructions in the same time frame. This leads to better performance.

So, a faster clock cycle equals better performance?

Yes, but it's not just about being fast; it's about how efficiently it uses those cycles. Higher speed needs better cooling and power management too! Let's summarize: the clock cycle time affects how many operations can be executed. A lower clock cycle time can lead to improved performance but needs proper design.

Instruction Set Efficiency

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Now let's look at instruction set efficiency. Who knows how it affects CPU performance?

Isn't it about how many instructions the CPU can execute?

Good point! The instruction set architecture defines the set of operations the CPU can perform. More efficient instruction sets can reduce complexity and execution time. Instruction set design can also influence memory use.

How does it relate to performance?

An optimized instruction set can lead to fewer cycles per instruction and faster execution. Consider RISC vs. CISC architectures—RISC has simpler instructions, requiring fewer cycles overall!

So, RISC can be more efficient?

Yes, often! But it depends on the application. Ultimately, a good instruction set enables the CPU to perform operations efficiently. To conclude: a well-designed instruction set is critical for efficient CPU performance. It minimizes cycles and maximizes throughput.

Performance Metrics

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Next, let's dive into performance metrics. Can anyone name a few?

Throughput, latency, and something with cycles?

Exactly! Throughput is the amount of work done within a given time, while latency measures delay. CPI, or cycles per instruction, reflects the efficiency level of instruction execution.

What about the differences?

Throughput focuses on output, latency is all about time, and CPI shows how many cycles an instruction takes. Understanding these helps us optimize performance. Remember: high throughput and low latency are desirable for any system.

So what's a good way to remember these metrics?

Let's use the acronym 'TLC': Throughput, Latency, and Cycles. This can help remind us of those three crucial metrics. In summary, throughput looks at the amount, latency at the delay, and CPI at the cycles needed for execution.

Cost/Performance Trade-off

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Finally, let's discuss the cost/performance trade-off. What do you think this means?

Balancing how much we spend on hardware with how well it performs?

Exactly! Achieving the right balance is crucial. Sometimes higher performance means higher costs, but we must assess if the performance gain justifies the expense.

Can you provide an example?

Sure! A top-line CPU may be powerful but very expensive. If you need a server for basic tasks, investing in high-end components may not be worth it. Consider the goal: is it worth the cost?

It's like choosing between a sports car and a regular car for a commute.

Exactly! Always ask: 'Does the performance benefit justify the expense?' To summarize: balancing costs with performance needs involves evaluating the overall system demands before making decisions.

Introduction & Overview

Read summaries of the section's main ideas at different levels of detail.

Quick Overview

Standard

Focusing on key design metrics, this section discusses clock cycle time, instruction set efficiency, various performance metrics like throughput and latency, and the cost/performance trade-off, emphasizing how each influences computer design and functionality.

Detailed

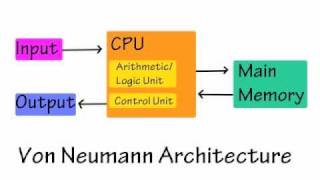

In this section, we explore the various design metrics and measures that are vital for assessing the performance and efficiency of computer systems. Key metrics include:

- Clock Cycle Time: The duration of a single cycle in a clock signal, which directly influences how many operations a CPU can complete per second.

- Instruction Set Efficiency: The impact of the architecture's instruction set design on CPU performance and complexity, impacting both execution speed and code compactness.

- Performance Metrics:

- Throughput: The amount of work performed in a given period.

- Latency: The delay before a transfer of data begins following an instruction for its transfer.

- Cycles Per Instruction (CPI): The average number of clock cycles each instruction takes to execute, reflective of RAW (Read After Write) dependencies.

- Cost/Performance Trade-off: The balancing act between the costs associated with hardware components and the desired performance, emphasizing the need for efficient allocation of resources. Understanding these metrics enables designers to make informed decisions that maximize system performance while managing costs.

Youtube Videos

Audio Book

Dive deep into the subject with an immersive audiobook experience.

Understanding Clock Cycle Time

Chapter 1 of 4

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

● Clock Cycle Time: How the clock cycle influences the performance of the system

Detailed Explanation

Clock cycle time refers to the duration of time required to complete one cycle of the processor's clock. This time is critical because it directly affects how many operations a processor can perform per second. A shorter clock cycle time often translates to a faster processor because it can execute instructions more quickly. Conversely, if the clock cycle is too short, it may lead to errors or require the processor to work harder than normal, causing inefficiencies.

Examples & Analogies

Think of clock cycle time like the time it takes for a light to turn green at a traffic signal. If the light stays green for a very brief moment, cars can go through the intersection quickly, but if it is too fast, some cars might not make it through without rushing. The perfect timing helps keep traffic flowing smoothly.

Instruction Set Efficiency

Chapter 2 of 4

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

● Instruction Set Efficiency: How the instruction set design affects the performance and complexity of the CPU

Detailed Explanation

The instruction set is a collection of commands that a CPU can execute. Efficiency in the instruction set design means that instructions should allow the CPU to perform many operations with fewer commands. A well-designed instruction set reduces the number of cycles needed to execute tasks, thus improving performance and simplifying CPU design. Complex instruction sets can lead to longer execution times and increased difficulty in programming.

Examples & Analogies

Imagine a Swiss Army knife, which includes many tools in one compact device. If each tool is efficient and easy to use, it allows you to accomplish more tasks quickly. However, if the tools are overly complicated or numerous, it can slow you down instead.

Performance Metrics

Chapter 3 of 4

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

● Performance Metrics: Throughput, latency, and cycles per instruction (CPI)

Detailed Explanation

Performance metrics are essential for analyzing how well a computer system functions. Throughput refers to the number of instructions a processor can execute in a given time frame. Latency is the time taken for a single instruction to complete. Cycles per instruction (CPI) indicates the number of clock cycles needed for each instruction. Understanding these metrics helps designers optimize systems for maximum efficiency.

Examples & Analogies

Consider a factory that produces toys. Throughput is the total number of toys produced in an hour. Latency is how long it takes to make a single toy from start to finish. If one toy takes longer than the others (high latency), it slows down overall production. Efficient production processes aim to maximize throughput while reducing latency.

Cost/Performance Trade-off

Chapter 4 of 4

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

● Cost/Performance Trade-off: Balancing the cost of hardware with performance needs

Detailed Explanation

The cost/performance trade-off involves finding the right balance between how much a computer system costs and how well it performs. Higher performance often comes with higher costs, making it essential to evaluate if the performance improvements justify the additional expenses. Designers must consider both immediate costs and long-term performance needs when choosing components.

Examples & Analogies

Imagine you're shopping for a car. You can buy a standard model that is inexpensive, but it may not have the speed and features you want. Alternatively, there's a high-performance sports car that costs significantly more. You need to weigh whether the extra speed and features of the sports car are worth the additional money compared to the standard model that meets basic needs.

Key Concepts

-

Clock Cycle Time: A critical measure influencing how many operations a CPU can complete per second.

-

Instruction Set Efficiency: Determines how effectively the CPU can execute instructions, impacting performance.

-

Throughput: Essential for measuring the amount of work performed within a specific time frame.

-

Latency: Indicates the delay before data transfer starts after an instruction.

-

Cycles Per Instruction (CPI): Represents the average clock cycles needed for executing instructions.

-

Cost/Performance Trade-off: The crucial evaluation of balancing costs and hardware performance.

Examples & Applications

A CPU with a clock cycle time of 1 ns can theoretically execute 1 billion cycles in one second.

RISC architectures often perform better in certain applications due to their simplified instruction sets, requiring fewer cycles to execute commands.

Memory Aids

Interactive tools to help you remember key concepts

Rhymes

Whenever the clock bells chime, faster is better, take less time.

Stories

Imagine a racecar clocking laps. Each lap represents a clock cycle; the faster it goes, the more laps are completed. But if the engine isn't efficient, it breaks down mid-race, showing how all parts must work in harmony.

Memory Tools

Remember 'CPC'—Clock Cycle, Performance, Cost, which are key pillars to consider in computer design.

Acronyms

Use 'TLC' for Throughput, Latency, and Cycles to recall essential performance metrics.

Flash Cards

Glossary

- Clock Cycle Time

The duration of one cycle in a computer's clock signal, crucial for determining operational speed.

- Instruction Set Efficiency

The effectiveness with which a CPU executes instructions, impacting performance and complexity.

- Throughput

The amount of processing that can be done in a given period.

- Latency

The time delay before a data transfer begins following an instruction that requests it.

- Cycles Per Instruction (CPI)

The average number of clock cycles required to execute an instruction, essential for assessing performance.

- Cost/Performance Tradeoff

The balancing of financial outlay for hardware against the performance gains it delivers.

Reference links

Supplementary resources to enhance your learning experience.