FPGA Implementation

Interactive Audio Lesson

Listen to a student-teacher conversation explaining the topic in a relatable way.

Introduction to FPGAs

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Today we're going to explore FPGAs, or Field-Programmable Gate Arrays. Can anyone tell me what they think FPGAs are?

Are they like regular chips but can be programmed for various tasks?

Exactly! Unlike ASICs, which are fixed at manufacture, FPGAs can be reprogrammed. They offer flexibility and are widely utilized in fields like digital signal processing.

So, can we change what functions they perform over time?

Yes! This reconfigurability is one of FPGAs' key advantages, making them ideal for evolving designs. Remember, FPGAs allow for parallel processing, which enhances their performance.

And they are used in many areas, right?

Correct again! Applications range from communications to video processing and cryptography. Let's summarize: FPGAs are flexible, reprogrammable devices critical for modern digital design.

Components of FPGAs

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Now let’s break down the components of an FPGA. Who can name one of the key components?

Logic blocks! Those are the building parts, right?

Absolutely! Logic blocks consist of Lookup Tables and Flip-Flops. LUTs can implement any Boolean function based on the inputs they receive. What about the inputs and outputs?

They also have I/O blocks that can be configured, right?

Yes! These interface with external components, adjusting for different voltage levels. Together, these components, including programmable interconnects and memory blocks, enable complex designs.

Can you recap the components for us?

Sure! The key components are logic blocks, programmable interconnects, I/O blocks, clock management, and memory blocks. This thorough understanding is essential for designing effective FPGA systems.

FPGA Design Flow

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Let’s dive into the FPGA design flow, the steps involved in creating your designs. Can anyone name the first stage?

Specification and requirements definition?

Right! It’s crucial to define your functional requirements clearly. Next, we enter the design entry phase. What tool might you use here?

We can use HDL like VHDL or Verilog!

Exactly! After writing the code, we move to synthesis, which transforms the HDL into a gate-level representation. Why do we need to optimize during synthesis?

To improve speed, area, and power consumption?

Correct! After implementation, we simulate the design to ensure everything runs correctly. Finally, we program the FPGA and test it. Would anyone like to summarize these stages?

So, it goes from specification to design entry, synthesis, implementation, simulation, programming, and testing, right?

Spot on! Understanding these stages ensures a robust FPGA design process.

Example: 4-bit Adder Implementation

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Now let’s look at a practical example – a 4-bit adder. Who can explain what it does?

It adds two 4-bit numbers together!

Exactly! We’ll write this in both VHDL and Verilog. Why do you think it's useful to see this in different languages?

So we can choose the best one for our projects or preferences?

Yes! Let's examine the VHDL code together... [explains code]. Now looking at Verilog... [continues explanation]. Can someone explain the purpose of the carry-out?

It indicates if there's an overflow beyond 4 bits!

Perfect! This adder gives us a clear illustration of how FPGA programming works in practice.

Challenges in FPGA Design

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Lastly, let’s discuss challenges in FPGA design. What do you think is a significant challenge?

Timing management seems tricky!

Absolutely! Timing and clock management are critical for ensuring synchronous operation. What are other challenges you can think of?

Resource constraints. We have limited logic blocks and RAM, right?

Correct! Each FPGA has finite resources, so optimization is key. Debugging is also a big challenge due to design complexity. How can we address this?

Using simulation tools like ModelSim or testing equipment like logic analyzers?

Exactly! Understanding these challenges will help you become a proficient FPGA designer. Let’s recap today’s lessons!

Introduction & Overview

Read summaries of the section's main ideas at different levels of detail.

Quick Overview

Standard

FPGA Implementation covers the fundamentals of FPGAs, including their reconfigurable nature, key components like logic blocks and I/O interfaces, the design flow process, and the challenges faced during implementation. An example of a 4-bit adder is also presented to demonstrate practical FPGA application.

Detailed

FPGA Implementation

Field-Programmable Gate Arrays (FPGAs) are versatile semiconductor devices that can be programmed to execute a variety of logical functions, providing significant advantages over fixed-function Application-Specific Integrated Circuits (ASICs). This section elucidates the essential components of FPGAs, including programmable logic blocks, interconnects, and I/O blocks, as well as their clock management and embedded memory.

The key advantages of FPGAs, such as flexibility, parallel processing capabilities, lower time-to-market, and cost-effectiveness for low to mid-volume production, make them suitable for various applications including digital signal processing and cryptography.

The section further details the FPGA design flow, comprising stages from defining requirements to programming and debugging the FPGA. A practical example illustrating the design of a simple 4-bit adder using VHDL and Verilog showcases the implementation process. Lastly, common challenges faced during FPGA design are discussed, particularly regarding timing management, resource constraints, and debugging complexities.

Youtube Videos

Audio Book

Dive deep into the subject with an immersive audiobook experience.

Introduction to FPGAs

Chapter 1 of 7

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Field-Programmable Gate Arrays (FPGAs) are semiconductor devices that can be programmed or configured to perform specific logical functions. Unlike traditional Application-Specific Integrated Circuits (ASICs), which are fixed after manufacturing, FPGAs can be reprogrammed to accommodate different design requirements. FPGAs are widely used in areas such as digital signal processing, communications, video processing, and cryptography, as they offer flexibility, parallelism, and high-speed performance. FPGAs consist of an array of logic blocks that can be programmed to implement various digital circuits. These logic blocks are interconnected through programmable routing resources. FPGAs also feature programmable input/output (I/O) blocks, clock management resources, and memory blocks, which can be utilized to design complex systems.

Detailed Explanation

FPGAs are versatile devices used in electronics to perform specific logical functions. Unlike ASICs that are fixed, FPGAs can be reconfigured even after manufacturing, making them adaptable for various applications like signal processing and video processing. The internal structure comprises logic blocks, which execute digital circuits, and these blocks are connected through programmable routing resources. Additionally, FPGAs include components for input and output management, clock management, and memory, allowing for the creation of complex systems.

Examples & Analogies

Think of an FPGA like a smartphone. Just as a smartphone can install different apps to perform various tasks such as taking photos, browsing the internet, or playing games, an FPGA can be programmed to perform different functions as needed. If a new app is desired, instead of getting a new phone (like getting a new ASIC), you can simply install the app. Similarly, with an FPGA, you can change its configuration to meet new requirements.

Components of an FPGA

Chapter 2 of 7

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Logic Blocks

The core of an FPGA consists of programmable logic blocks, each capable of implementing a variety of logic functions. These blocks can be configured to perform combinational or sequential logic.

- Lookup Tables (LUTs): The basic building blocks that define the logic functions. A 4-input LUT, for instance, can implement any Boolean function of four variables.

- Flip-Flops: Used for implementing sequential logic and storing state information.

Programmable Interconnects

These are the routing resources that connect the logic blocks. FPGAs allow the interconnection of logic blocks in a way that can be reprogrammed for different applications.

I/O Blocks

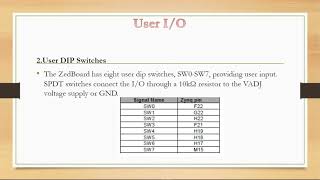

FPGAs offer configurable input and output blocks that support different voltage levels and communication standards. These are used to interface the FPGA with external components like sensors, processors, or other systems.

Clock Management

FPGAs include resources such as phase-locked loops (PLLs) and clock dividers to manage timing signals, ensuring that the system operates synchronously.

Embedded Memory Blocks

FPGAs typically include embedded memory blocks such as RAM or FIFOs, allowing the storage and retrieval of data within the FPGA. These are often used in applications requiring high-speed data storage, such as video processing.

Detailed Explanation

FPGAs are made up of several key components:

1. Logic Blocks: The heart of FPGAs, where logic functions are performed. They can be flipped to execute different tasks.

2. Programmable Interconnects: These are like roads that connect different logic blocks, allowing them to communicate.

3. I/O Blocks: Act as gateways to the outside world, letting the FPGA interface with external devices.

4. Clock Management: Ensures that everything runs on time, managing signals that synchronize the operations within the FPGA.

5. Embedded Memory Blocks: Internal storage that allows quick access and processing of data when needed, which is crucial for high-speed tasks.

Examples & Analogies

Imagine an FPGA as a modular furniture piece in your home. The logic blocks are like the individual furniture items (like a sofa or table) that can be arranged in various configurations to suit your needs. The programmable interconnects represent how these pieces can be put together in different ways, while the I/O blocks act like doors and windows, allowing you to connect your home with the outside. Clock management ensures that everything follows a rhythm, like a conductor leading an orchestra, while the embedded memory serves as storage space to keep items at hand for when you need them, similar to having drawers in your furniture.

Advantages of FPGAs

Chapter 3 of 7

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Flexibility and Reconfigurability

One of the main advantages of FPGAs is their ability to be reprogrammed after manufacture. This allows designers to implement a wide variety of functions without needing a new chip, making FPGAs ideal for prototyping, customization, and evolving designs.

Parallel Processing

FPGAs can execute many tasks simultaneously, making them ideal for applications that require high-speed processing. This parallelism provides significant performance improvements over traditional processors for certain tasks, such as signal processing and cryptography.

Lower Time-to-Market

Because FPGAs can be reprogrammed and do not require the manufacturing of custom chips (like ASICs), development times are shorter, which can significantly reduce the time-to-market for a product.

Cost-Effectiveness for Low to Mid-Volume Production

FPGAs are more cost-effective than ASICs for low to mid-volume production, as they do not require the expensive tooling and fabrication process of ASICs.

Detailed Explanation

FPGAs provide several advantages:

1. Flexibility: They can be reprogrammed to take on various functions, making them useful for designers needing to adapt designs without starting from scratch.

2. Parallel Processing: Unlike traditional processors that might handle one task at a time, FPGAs can tackle multiple tasks simultaneously, speeding up processes significantly.

3. Reduced Time-to-Market: Development is faster since there’s no need for custom chip manufacturing, allowing companies to bring products to market more quickly.

4. Cost-Effectiveness: For projects that don’t require thousands of chips, FPGAs save money compared to ASICs, which involve costly production processes.

Examples & Analogies

Consider FPGAs like a versatile Swiss Army knife. Just as a Swiss Army knife can adapt its tools for different tasks—like cutting, screwing, or opening bottles—FPGAs can be reprogrammed for different functions. If you only need a few tools (or chips), using the Swiss Army knife is more cost-effective than buying individual specialized tools. Similarly, in projects where only a few copies are needed, using an FPGA is a budget-friendly option compared to developing a specialized ASIC.

FPGA Design Flow

Chapter 4 of 7

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

The FPGA design flow typically involves the following stages:

1. Specification and Requirements Definition: Define the functional requirements and performance goals of the system. This stage involves understanding the problem and creating a detailed specification.

2. Design Entry: In this stage, the design is specified using hardware description languages (HDLs) such as VHDL or Verilog. You can either write the code manually or use a high-level design tool that supports graphical design entry.

3. Synthesis: The HDL code is synthesized into a gate-level representation that maps the design onto the FPGA’s programmable logic blocks. This process involves optimizing the design for speed, area, and power consumption.

4. Implementation: The synthesized design is placed and routed onto the FPGA fabric. The place-and-route process determines how the logic blocks and routing resources are mapped onto the FPGA.

5. Simulation and Verification: Before programming the FPGA, the design is simulated to ensure it behaves correctly. Simulation tools like ModelSim or Vivado Simulator can be used to check functionality and timing.

6. Programming the FPGA: Once verified, the design is compiled and programmed into the FPGA. This can be done using a tool like Xilinx ISE, Vivado, or Intel Quartus.

7. Testing and Debugging: The final step is to test the FPGA on the actual hardware. Tools like in-circuit debuggers and logic analyzers are used to validate the system’s performance and behavior.

Detailed Explanation

The design flow for creating an FPGA includes several steps:

1. Specification: Understand exactly what the project needs and document those needs clearly.

2. Design Entry: Write down the design using languages like VHDL or Verilog, either manually or by using design software.

3. Synthesis: Convert your code into a format that can be implemented on the FPGA.

4. Implementation: Assign the design to the FPGA’s physical architecture, determining how various blocks will connect.

5. Simulation: Test the design on a computer to find and fix bugs before hardware implementation.

6. Programming: Transfer the design into the FPGA.

7. Testing: Verify the FPGA works as intended, checking performance and functionality in real-world applications.

Examples & Analogies

Think of the FPGA design flow like building a house. First, you create blueprints (specifications) to understand what you want. Then, you choose materials and methods (design entry). Next, you organize how everything fits together (synthesis and implementation). Before construction, you might build a model or walkthrough (simulation) to ensure your plans work. Once ready, you start building (programming) and finally check that everything is properly constructed and usable (testing). Just as with house building, following a well-defined process is crucial to achieve a successful result.

FPGA Implementation Example: 4-bit Adder

Chapter 5 of 7

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Let's walk through the design and implementation of a simple 4-bit adder on an FPGA.

VHDL Code for 4-bit Adder

-- Entity Declaration for 4-bit Full Adder entity full_adder_4bit is port ( A : in std_logic_vector(3 downto 0); -- 4-bit input A B : in std_logic_vector(3 downto 0); -- 4-bit input B Cin : in std_logic; -- Carry-in Sum : out std_logic_vector(3 downto 0); -- 4-bit sum output Cout : out std_logic -- Carry-out ); end entity full_adder_4bit; -- Architecture Definition for Full Adder architecture behavior of full_adder_4bit is signal carry : std_logic_vector(3 downto 0); begin -- Full Adder Logic Sum(0) <= A(0) xor B(0) xor Cin; carry(0) <= (A(0) and B(0)) or (Cin and (A(0) xor B(0))); Sum(1) <= A(1) xor B(1) xor carry(0); carry(1) <= (A(1) and B(1)) or (carry(0) and (A(1) xor B(1))); Sum(2) <= A(2) xor B(2) xor carry(1); carry(2) <= (A(2) and B(2)) or (carry(1) and (A(2) xor B(2))); Sum(3) <= A(3) xor B(3) xor carry(2); Cout <= (A(3) and B(3)) or (carry(2) and (A(3) xor B(3))); end architecture behavior;

Verilog Code for 4-bit Adder

module full_adder_4bit( input [3:0] A, // 4-bit input A input [3:0] B, // 4-bit input B input Cin, // Carry-in output [3:0] Sum, // 4-bit sum output output Cout // Carry-out ); wire [3:0] carry; // Internal carry wires assign Sum[0] = A[0] ^ B[0] ^ Cin; assign carry[0] = (A[0] & B[0]) | (Cin & (A[0] ^ B[0])); assign Sum[1] = A[1] ^ B[1] ^ carry[0]; assign carry[1] = (A[1] & B[1]) | (carry[0] & (A[1] ^ B[1])); assign Sum[2] = A[2] ^ B[2] ^ carry[1]; assign carry[2] = (A[2] & B[2]) | (carry[1] & (A[2] ^ B[2])); assign Sum[3] = A[3] ^ B[3] ^ carry[2]; assign Cout = (A[3] & B[3]) | (carry[2] & (A[3] ^ B[3])); endmodule

FPGA Programming and Testing

- After synthesizing the design using tools like Xilinx Vivado or Intel Quartus, the configuration bitstream is generated.

- The FPGA is programmed with this bitstream file, and the system is verified by testing the inputs and monitoring the outputs on an FPGA development board using LEDs, switches, or a logic analyzer.

Detailed Explanation

In this section, we explore the design of a simple 4-bit adder using both VHDL and Verilog, which are standard hardware description languages for FPGAs. The VHDL code provides an entity for the adder, defining inputs and outputs, and the architecture describes how the adder operates using logic expressions. Similarly, the Verilog code provides a module definition accomplishing the same tasks. After the coding, the FPGA is programmed with these designs, verifying their functionality by connecting to a development board and observing outputs.

Examples & Analogies

Think of creating this 4-bit adder as cooking a new dish. The VHDL or Verilog code is the recipe that tells you how to combine ingredients (inputs A, B, and Cin) to create the final dish (Sum and Cout). Just like following a recipe step-by-step ensures a perfect dish, following the correct coding steps ensures our adder functions as intended. Once you’ve cooked, you taste (test) the dish to make sure it meets your expectations. Programming the FPGA with the design is akin to serving the dish after it’s completed.

Challenges in FPGA Design

Chapter 6 of 7

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Timing and Clock Management

One of the key challenges in FPGA design is ensuring that the system meets timing constraints. Clock management tools, such as PLLs (Phase-Locked Loops) and clock dividers, are essential for synchronizing various components of the FPGA.

Resource Constraints

FPGAs have a finite amount of logic blocks, memory, and I/O pins. Careful planning and optimization are required to ensure that the design fits within the FPGA's resources.

Debugging and Testing

Debugging FPGA designs can be challenging because of the complexity of parallel circuits. However, with proper simulation tools and debugging interfaces (such as JTAG and logic analyzers), these challenges can be addressed.

Detailed Explanation

Designing FPGAs comes with its own set of challenges:

1. Timing and Clock Management: Ensuring that all components of the FPGA operate in sync is tricky. Proper clock management helps maintain timing accuracy.

2. Resource Constraints: There’s a limit to how many logic blocks and storage units an FPGA has. Designers must optimize their designs to fit within these limits.

3. Debugging and Testing: The complexity of parallel circuits makes it hard to pinpoint issues. However, using tools like simulation and debugging interfaces simplifies this process.

Examples & Analogies

Imagine organizing a large concert as a project manager. Timing is crucial, ensuring musicians play in sync (timing constraints). However, you also have a limited number of seats and equipment (resource constraints). If too many bands apply to perform (complex designs), fitting them all into the schedule can be challenging. Lastly, if something goes wrong during the concert, troubleshooting issues quickly becomes essential, similar to debugging in FPGA design. Just as a manager can use walkie-talkies and monitoring tools to coordinate, engineers can use simulation and debugging tools to ensure everything functions well.

Summary of Key Concepts

Chapter 7 of 7

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

FPGA Basics

FPGAs are reconfigurable hardware devices that allow for parallel processing and high-speed computation.

Components of FPGA

Logic blocks, interconnects, I/O blocks, clock management, and memory blocks.

Design Flow

Involves specification, design entry (HDL), synthesis, implementation, simulation, and programming.

Design Example

4-bit adder designed using VHDL and Verilog, demonstrating the FPGA implementation process.

Challenges

Timing, resource constraints, and debugging are key challenges in FPGA design.

Detailed Explanation

This summary consolidates the major concepts related to FPGA implementation:

1. FPGA Basics: Highlights the reconfigurable nature of FPGAs that supports high-speed processing.

2. Components of FPGA: Outlines the essential building blocks like logic blocks and memory.

3. Design Flow: Summarizes the steps involved in creating an FPGA design.

4. Design Example: Reiterates the 4-bit adder example as a practical application.

5. Challenges: Reviews the common issues faced during FPGA design processes.

Examples & Analogies

Picture a car's dashboard, where each gauge and light serves the purpose of providing information about the vehicle's operation (components). Just as a driver needs to understand how to read these gauges to operate the vehicle efficiently (design flow), the summary gives an overview of the tools and challenges needed to create and use an FPGA. Recognizing challenges, like managing fuel (timing) or knowing there's only so much space in the car (resource constraints), mirrors the complexities of FPGA design.

Key Concepts

-

FPGA Flexibility: FPGAs can be reprogrammed after manufacturing to suit evolving design needs.

-

Components of FPGAs: Includes logic blocks, programmable interconnects, I/O blocks, clock management, and embedded memory.

-

FPGA Design Flow: A structured process from specification definition to testing.

-

4-bit Adder Implementation: An example of implementing a simple adder using VHDL and Verilog.

-

Challenges in FPGA Design: Key issues include timing, resource constraints, and debugging complexities.

Examples & Applications

An FPGA can be programmed to function as a digital filter in a communication device, processing data in real time.

A 4-bit adder demonstrated with provided HDL code that showcases how to implement basic arithmetic operations.

Memory Aids

Interactive tools to help you remember key concepts

Rhymes

FPGA, oh what a thing, flexible and fast, let logic swing!

Stories

Once upon a time, there was a magical chip called FPGA, always changing houses to fit new roles in the land of circuits.

Memory Tools

FLIP - Flexibility, Logic, Interfaces, Programming: The Key Features of an FPGA.

Acronyms

FIVE - Fields (applications), I/O (blocks), Versatile (designs), Efficient (processing).

Flash Cards

Glossary

- FieldProgrammable Gate Arrays (FPGAs)

Reconfigurable semiconductor devices that can perform various logical functions.

- Logic Blocks

Core components of FPGAs that execute combinational or sequential logic.

- Lookup Tables (LUTs)

Basic building blocks in FPGAs that define logic functions.

- FlipFlops

Circuits used for storing state information in sequential logic.

- Programmable Interconnects

Routing resources in FPGAs connecting logic blocks.

- I/O Blocks

Configurable input/output components interfacing with external systems.

- Clock Management

Resources used to manage timing signals in FPGA designs.

- Embedded Memory Blocks

Memory units within FPGAs for data storage and retrieval.

- Design Flow

Sequential stages to implement a design on an FPGA.

- VHDL/Verilog

Hardware description languages used for describing FPGA designs.

Reference links

Supplementary resources to enhance your learning experience.