FPGA Implementation Example: 4-bit Adder

Interactive Audio Lesson

Listen to a student-teacher conversation explaining the topic in a relatable way.

Introduction to 4-bit Adder Design

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Today, we’re diving into the design of a 4-bit adder using FPGA technology. Can anyone tell me what an adder does?

It adds binary numbers together, right?

Exactly! A 4-bit adder can add two 4-bit numbers. Can someone explain what inputs it might need?

It needs two 4-bit inputs and a carry-in, right?

Correct! These inputs allow the adder to handle situations where the addition may exceed the 4-bit limit. That's a crucial concept in digital logic design.

How does it handle the carry-in signal?

Good question! The carry-in is added to the least significant bit and may influence subsequent bits. Remember, we can represent addition with XOR for sum and AND for carries!

What’s a good way to remember that?

You can think of 'XOR for sum — adding friends together, and AND for carries — like calling extra friends into the group!' Let's summarize: A 4-bit adder takes two 4-bit inputs and a carry-in while outputting a 4-bit sum and a carry-out.

VHDL Code Explanation

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Now let's look at the VHDL implementation of our 4-bit adder. Who remembers what VHDL stands for?

VHDL stands for VHSIC Hardware Description Language.

Exactly! In our VHDL code, we declare inputs for the two 4-bit vectors, A and B, and then a carry-in signal. Can anyone spot the full adder logic within this code?

The Sum outputs are defined using XOR operations!

Right! And we use signals to track carries through the different stages of our addition. This step-wise carry management is crucial!

Why do we separate the carry signals?

Separating carry signals helps in managing their propagation through the adder efficiently. Let's summarize: VHDL allows us to describe our logic systematically, giving us control over how each part of the logic interacts.

Verilog Code Overview

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Next, we're exploring the Verilog implementation. Who can remind us what Verilog is also considered?

Verilog is another hardware description language, similar to VHDL.

Exactly! The key difference lies in the syntax. Can someone identify how we interact with signals in Verilog compared to VHDL?

In Verilog, we use the assign statement for connecting signals.

Yes! In the Verilog code, we specify inputs and outputs in a more straightforward way. Each bit's logic can be cascaded easily. How do you think this might help during debugging?

It's clearer and easier to identify issues because of the concise syntax!

Exactly right! Consistency and readability in code can save a lot of headaches during implementation.

Programming and Testing the FPGA

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Finally, let's discuss the programming and testing phase. Who can explain what happens after we finish coding our adder?

We need to synthesize the design first!

Correct! Synthesis translates our code into the configuration that the FPGA can understand. What tool would we commonly use for this?

Tools like Xilinx Vivado or Intel Quartus are popular for FPGA designs and synthesis!

Absolutely! After synthesis, the design is programmed into the FPGA. How can we verify our adder is functioning correctly?

We can use LEDs and switches on the FPGA development board to test inputs and outputs!

Great! This hands-on approach allows us to see our design in action and fix any real-world issues that arise. Summarizing, we synthesize, program, and then test the FPGA with our designed logic.

Introduction & Overview

Read summaries of the section's main ideas at different levels of detail.

Quick Overview

Standard

The section delves into the design and implementation of a 4-bit adder on an FPGA platform, presenting both VHDL and Verilog code snippets. Additionally, it highlights the process of programming and testing the FPGA, emphasizing how to verify functionality through hands-on verification methods.

Detailed

FPGA Implementation Example: 4-bit Adder

In this section, we explore the design and implementation of a 4-bit adder using FPGA technology. FPGAs offer significant advantages in flexibility and reconfigurability, making them suitable for implementing digital logic circuits like adders. The following subsections detail the VHDL and Verilog code for constructing a 4-bit full adder.

1. VHDL Code for 4-bit Adder

The VHDL entity for a 4-bit full adder includes input ports for two 4-bit vectors (A, B) and a carry-in signal (Cin), with output ports for a 4-bit sum and a carry-out signal (Cout). The logic of the adder is implemented using a series of XOR and AND operations within the architecture.

2. Verilog Code for 4-bit Adder

Similarly, the Verilog implementation follows the same logic pattern, utilizing wire connections to manage carry signals between bits. Each line demonstrates logical operations needed to produce both the sum and carry outputs.

3. FPGA Programming and Testing

After synthesizing the design using tools like Xilinx Vivado or Intel Quartus, you generate a configuration bitstream that is then programmed into the FPGA. Testing can be performed using an FPGA development board, where inputs and outputs are monitored through peripherals like LEDs and logic analyzers. This practical implementation facilitates understanding the full design cycle from concept to execution and application.

Youtube Videos

Audio Book

Dive deep into the subject with an immersive audiobook experience.

VHDL Code for 4-bit Adder

Chapter 1 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

-- Entity Declaration for 4-bit Full Adder entity full_adder_4bit is port ( A : in std_logic_vector(3 downto 0); -- 4-bit input A B : in std_logic_vector(3 downto 0); -- 4-bit input B Cin : in std_logic; -- Carry-in Sum : out std_logic_vector(3 downto 0); -- 4-bit sum output Cout : out std_logic -- Carry-out ); end entity full_adder_4bit; -- Architecture Definition for Full Adder architecture behavior of full_adder_4bit is signal carry : std_logic_vector(3 downto 0); begin -- Full Adder Logic Sum(0) <= A(0) xor B(0) xor Cin; carry(0) <= (A(0) and B(0)) or (Cin and (A(0) xor B(0))); Sum(1) <= A(1) xor B(1) xor carry(0); carry(1) <= (A(1) and B(1)) or (carry(0) and (A(1) xor B(1))); Sum(2) <= A(2) xor B(2) xor carry(1); carry(2) <= (A(2) and B(2)) or (carry(1) and (A(2) xor B(2))); Sum(3) <= A(3) xor B(3) xor carry(2); Cout <= (A(3) and B(3)) or (carry(2) and (A(3) xor B(3))); end architecture behavior;

Detailed Explanation

In this chunk, we define the VHDL code for implementing a 4-bit full adder. The 'entity' declaration at the beginning specifies the inputs and outputs of the adder. The inputs include two 4-bit vectors (A and B) and a single carry-in (Cin). The outputs are a 4-bit sum and a carry-out (Cout). The architecture part contains the logic for the full adder, which sums the bits of the inputs while managing carries using XOR and AND operations. For each bit, the sum and carry-out are determined based on the current inputs and the carry from the previous bit.

Examples & Analogies

Think of the 4-bit adder like a group of friends trying to add up their funds to buy something together. Each friend can only contribute a small amount, just like how each bit can only contribute 1 or 0. The carry-in is like capital that has been pooled together before the calculation starts, and the carry-out indicates if they need to go to the next friend to add more money if their total exceeds a certain amount.

Verilog Code for 4-bit Adder

Chapter 2 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

module full_adder_4bit( input [3:0] A, // 4-bit input A input [3:0] B, // 4-bit input B input Cin, // Carry-in output [3:0] Sum, // 4-bit sum output output Cout // Carry-out ); wire [3:0] carry; // Internal carry wires assign Sum[0] = A[0] ^ B[0] ^ Cin; assign carry[0] = (A[0] & B[0]) | (Cin & (A[0] ^ B[0])); assign Sum[1] = A[1] ^ B[1] ^ carry[0]; assign carry[1] = (A[1] & B[1]) | (carry[0] & (A[1] ^ B[1])); assign Sum[2] = A[2] ^ B[2] ^ carry[1]; assign carry[2] = (A[2] & B[2]) | (carry[1] & (A[2] ^ B[2])); assign Sum[3] = A[3] ^ B[3] ^ carry[2]; assign Cout = (A[3] & B[3]) | (carry[2] & (A[3] ^ B[3])); endmodule

Detailed Explanation

This chunk presents the Verilog code for a 4-bit adder, which serves a similar function as the VHDL code but uses a different syntax and structure. The module declaration identifies the inputs and outputs. The internal 'carry' wires are used to store intermediate carry values from each bit's addition. The 'assign' statements are utilized to define the logical operations that generate the sum and carry for each corresponding bit. This highlights how the adder functions to compile the overall sum from the individual binary digits, taking into account any carries generated.

Examples & Analogies

Imagine you're doing a group project with different sections assigned to each member. Each one independently counts their portion of the project (the bits), but they need to communicate (using the carry wires) to make sure the final count is correct. If one member has extra notes that need to be shared (the carry-out), it gets passed on to ensure everyone has their total just right.

FPGA Programming and Testing

Chapter 3 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

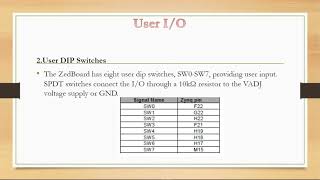

● After synthesizing the design using tools like Xilinx Vivado or Intel Quartus, the configuration bitstream is generated.

● The FPGA is programmed with this bitstream file, and the system is verified by testing the inputs and monitoring the outputs on an FPGA development board using LEDs, switches, or a logic analyzer.

Detailed Explanation

In this final chunk, we discuss how to take the designed code and turn it into a functioning circuit on an FPGA. The design code (written in VHDL or Verilog) needs to be synthesized, which means it’s translated into a form that the FPGA can understand. This results in a configuration bitstream — essentially a file that tells the FPGA how to configure its logic blocks and routing to implement the desired functionality. After programming the FPGA with this bitstream, the next critical step is testing. You can use tools such as LED indicators and switches to verify that the inputs produce the correct outputs, ensuring that the adder operates correctly.

Examples & Analogies

Think of programming an FPGA like baking a cake. First, you gather your ingredients and mix them according to the recipe (synthesis). The configuration bitstream is like your final cake batter, ready to be put into the oven (the FPGA). Once it's baked, you need to taste it to ensure it came out right, just like using inputs and outputs to test your FPGA setup to ensure everything is working as expected.

Key Concepts

-

4-bit Adder: A digital circuit that adds two 4-bit binary numbers along with a carry-in.

-

VHDL and Verilog: Hardware description languages used for coding the logical structure of digital systems.

-

Synthesis: The process of converting high-level code to a low-level design that can be implemented on an FPGA.

Examples & Applications

VHDL Example: The code for a 4-bit adder in VHDL demonstrates how to define inputs, outputs, and logic to perform binary addition.

Verilog Example: The Verilog code example similarly establishes the adder's function but uses different syntax and structure.

Memory Aids

Interactive tools to help you remember key concepts

Rhymes

When adding bits with all your might, XOR sums will lead you right! And if you find a carry out, AND/OR will clear your doubt.

Stories

Imagine two friends, A and B, who always share their numbers with a helper, Cin, who ensures the total count is correct. Together, they make magic happen — creating Sum and Cout, ensuring all is balanced!

Memory Tools

For a 4-bit adder: 'A B C = Add, But Carry!' helps to remember to add and consider carry for binary.

Acronyms

SUM — 'S' for Straightforward, 'U' for Uniting, 'M' for Managing carry gives a way to remember the process.

Flash Cards

Glossary

- VHDL

VHSIC Hardware Description Language, used for describing the structure and behavior of electronic systems.

- Verilog

A hardware description language that provides a way to describe digital and analog systems and is similar to VHDL.

- FPGA

Field-Programmable Gate Array, a semiconductor device that can be configured to perform specific logical functions.

- Carryin

An input that represents a carry value from a previous less significant addition.

- Sum

The output of an addition operation, resulting from adding the input values and the carry-in.

- Carryout

An output that represents a carry value that may be passed on to a more significant addition.

Reference links

Supplementary resources to enhance your learning experience.