Compile the Kernel Module

Enroll to start learning

You’ve not yet enrolled in this course. Please enroll for free to listen to audio lessons, classroom podcasts and take practice test.

Interactive Audio Lesson

Listen to a student-teacher conversation explaining the topic in a relatable way.

Creating the Makefile

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Today, we're going to learn how to compile our kernel module. The first step is to create a Makefile. Can anyone tell me what a Makefile does?

Isn't it a script that contains instructions for building the software?

Exactly! It lays out the rules for compiling and linking the modules. For our sensor module, we’ll have the line `obj-m += sensor.o`, which tells the build process to compile `sensor.c` into an object file.

What does the 'obj-m' mean?

'obj-m' indicates that we're building a loadable module. It’s essential for kernel programming.

Can we use the Makefile for other projects too?

Yes! A Makefile is very versatile. Remember, it facilitates quick builds.

In summary, a Makefile simplifies the compilation process. Next, we'll look at how to call it.

Compiling the Module

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Now that we’ve written our Makefile, what's the command we’ll use to compile the module?

It’s just `make`, isn’t it?

Correct! By running `make`, it reads our Makefile and compiles the code. It connects to the kernel build system to ensure compatibility.

What if it doesn't compile successfully?

Good question! If errors occur, it typically highlights what went wrong. Always read the terminal output carefully.

To recap, using `make` compiles our code with the rules we set up in our Makefile and helps in quickly finding errors. Let’s move on to the cleaning process next.

Cleaning Up

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

What do we do after compiling our module? Is there a way to clean up any extraneous files?

We can use the `make clean` command to remove compiled files, right?

Exactly! The `clean` target in our Makefile is critical for maintaining a tidy workspace. It removes the `*.o` and `*.ko` files.

Why is that important?

It prevents confusion and potential issues when recompiling. Always keep your directory organized.

In summary, using `make clean` helps keep our working directory manageable and prevents stale files from causing problems in future builds.

Introduction & Overview

Read summaries of the section's main ideas at different levels of detail.

Quick Overview

Standard

In this section, we delve into compiling the kernel module for the ultrasonic sensor. It includes creating a Makefile, invoking the make command to build the module, and ensuring proper setup for dynamic module compilation.

Detailed

In-Depth Summary

This section focuses on the compilation of the kernel module designed for the ultrasonic ranging sensor. To initiate the compilation process, the user is required to create a Makefile in the same directory as the source file (sensor.c). The Makefile specifies the build parameters necessary to compile the kernel module correctly, utilizing the existing modules in the Linux kernel as indicated by /lib/modules/$(shell uname -r)/build. The commands within the Makefile manage the build and clean processes efficiently by using standard Linux kernel build practices. By running the make command, users can compile the module into a .ko file that is essential for subsequent loading and interaction with the kernel. This segment is crucial for those aiming to develop and integrate kernel modules within a Linux environment.

Youtube Videos

Audio Book

Dive deep into the subject with an immersive audiobook experience.

Creating the Makefile

Chapter 1 of 2

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

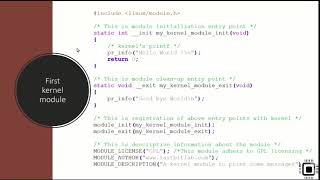

To compile the kernel module, create a Makefile in the same directory as your source file (sensor.c).

Makefile:

obj-m += sensor.o

all:

make -C /lib/modules/$(shell uname -r)/build M=$(PWD) modules

clean:

make -C /lib/modules/$(shell uname -r)/build M=$(PWD) clean

Detailed Explanation

The first step in compiling your kernel module is to create a Makefile. This Makefile tells the build system how to compile your code. You declare your object file (sensor.o) which is your compiled kernel module code. The 'all' target in the Makefile will invoke the kernel's build system to build the module, using the current kernel version as specified by 'uname -r'. The 'clean' target allows you to clean up the built files, helping you keep your workspace tidy.

Examples & Analogies

Think of the Makefile as a recipe card for baking a cake. It lists the ingredients (source code files) and the steps (commands to compile) you need to follow to create the cake (kernel module). Just as you need a recipe to bake correctly, the Makefile guides the computer to compile your code properly.

Building the Module

Chapter 2 of 2

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Run the following command to build the module:

make

Detailed Explanation

Once you have your Makefile ready, you simply run the command 'make' in the terminal. This command triggers the build process as instructed in your Makefile. The build system will now compile your sensor.c file into a kernel object file (.ko file), which can be loaded into the kernel.

Examples & Analogies

Imagine you are starting a mechanical assembly. The 'make' command is like pressing a button to start the assembly line; it gets everything working together to create the final product. Just as the assembly line puts parts together to create a machine, the make command compiles your code into a working kernel module.

Key Concepts

-

Makefile: A key file that automates the build process for kernel modules.

-

Kernel Module Compilation: The process of converting source code into a loadable kernel module.

-

obj-m: A directive in Makefiles indicating object files to be treated as modules.

-

Command Line Make: The command to execute the build process defined in the Makefile.

Examples & Applications

Creating a simple Makefile to compile a kernel module with obj-m += sensor.o.

Using the command make -C /lib/modules/$(shell uname -r)/build M=$(PWD) modules to compile a module.

Memory Aids

Interactive tools to help you remember key concepts

Rhymes

To compile a kernel with ease, just invoke make and please, see your module compile with glee!

Stories

Imagine a chef (the Makefile) preparing a meal (the kernel module). The chef uses ingredients (source files) and follows a recipe (build rules) to serve a delicious dish (the compiled module) to the diners (the operating system).

Memory Tools

Remember 'MOC' for Makefile, Object, Compilation: Make your Object clear!

Acronyms

M.O.D. - Makefile, Object, Done! Remember the process of compiling a module.

Flash Cards

Glossary

- Makefile

A file containing a set of directives used by a make build automation tool to generate a target/goal.

- Kernel Module

A piece of code that can be loaded into the Linux kernel to extend its functionality without requiring a system reboot.

- objm

A directive in a Makefile indicating that the specified object files are modules.

- make

A build automation tool that automatically builds executable programs and libraries from source code.

Reference links

Supplementary resources to enhance your learning experience.